Изобретение относится к области автоматики и вычислительной техники, может быть использовано для построения устройств ЭВМ и однородных вычислительнь1х сред и является усовершенствованием изобретения по авт. св. № 1196845.

Целью изобретения является повышение контролепригодности логической ячейки.

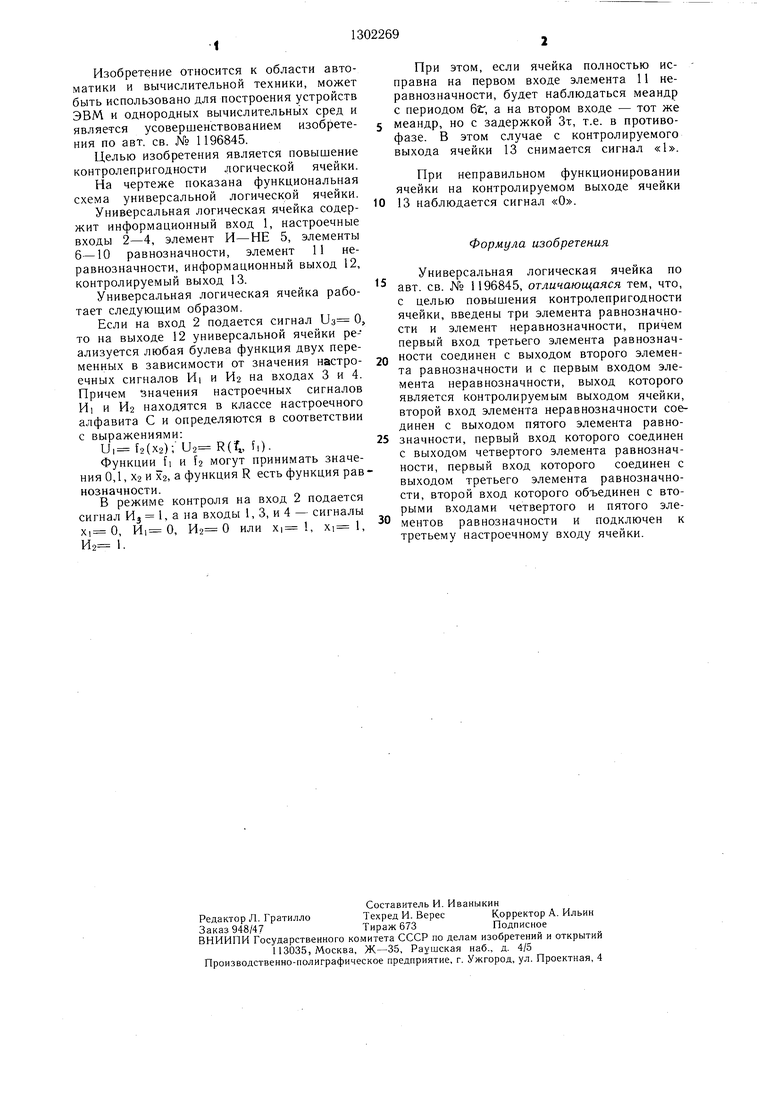

На чертеже показана функциональная схема универсальной логической ячейки.

Универсальная логическая ячейка содержит информационный вход 1, настроечные входы 2-4, элемент И-НЕ 5, элементы 6-10 равнозначности, элемент 11 неравнозначности, информационный выход 12, контролируемый выход 13.

Универсальная логическая ячейка работает следующим образом.

Если на вход 2 подается сигнал из О, то на выходе 12 универсальной ячейки ре- ализуется любая булева функция двух переменных в зависимости от значения настроечных сигналов HI и На на входах 3 и 4. Причем Значения настроечных сигналов И и И2 находятся в классе настроечного алфавита С и определяются в соответствии с выражениями:

(x2); U2 R(fv fi).

Функции fi и f2 могут принимать значения 0,1, Х2 и Х2, а функция R есть функция равнозначности.

В режиме контроля на вход 2 подается сигнал Из 1, а на входы 1, 3, и 4 - сигналы х, О, HI О, Н2 О или Х| 1, xi 1,

Н2 1.

Нри этом, если ячейка полностью исправна на первом входе элемента 11 неравнозначности, будет наблюдаться меандр с периодом бй, а на втором входе - тот же меандр, но с задержкой 3т, т.е. в противо- фазе. В этом случае с контролируемого выхода ячейки 13 снимается сигнал «1.

Нри неправильном функционировании ячейки на контролируемом выходе ячейки 13 наблюдается сигнал «О.

Формула изобретения

Универсальная логическая ячейка по

авт. св. № 1196845, отличающаяся тем, что, с целью повышения контролепригодности ячейки, введены три элемента равнозначности и элемент неравнозначности, причем первый вход третьего элемента равнозначности соединен с выходом второго элемента равнозначности и с первым входом элемента неравнозначности, выход которого является контролируемым выходом ячейки, второй вход элемента неравнозначности соединен с выходом пятого элемента равнозначности, первый вход которого соединен с выходом четвертого элемента равнозначности, первый вход которого соединен с выходом третьего элемента равнозначности, второй вход которого объединен с вторыми входами четвертого и пятого элементов равнозначности и подключен к третьему настроечному входу ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальная логическая ячейка | 1984 |

|

SU1196845A1 |

| Универсальный логический модуль | 1985 |

|

SU1260939A1 |

| Универсальный логический модуль | 1985 |

|

SU1269121A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1282112A1 |

| Многофункциональный логический модуль | 1987 |

|

SU1425648A2 |

| Многофункциональный логический модуль | 1985 |

|

SU1307452A2 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1765821A1 |

| Универсальный логический модуль | 1988 |

|

SU1520505A1 |

| Универсальный логический модуль | 1985 |

|

SU1312561A1 |

| Универсальная логическая ячейка с самоконтролем | 1985 |

|

SU1264183A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано для построения устройств ЭВМ и однородных вычислительных сред и является усовершенствованием изобретения по а. с. № 1196845. Целью изобретения является повышение контролепригодности логической ячейки. Универсальная логическая ячейка содержит информационный вход 1, настроечные входы 2-4, элемент И-НЕ 5, элементы 6-10 равнозначности, элемент II неравнозначности, информационный выход 12, контролируемый выход 13. 1 ил. 00 о lN3 I4D Ci со

| Универсальная логическая ячейка | 1984 |

|

SU1196845A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-07—Публикация

1984-06-26—Подача