113040312

Изобретение.относится к вычисли-же время сигнал 1 по второму входу тельной технике и может быть исполь-блока 12 запрещает двойное прохожде- зовано для объединения процессоров вние сигнала синхронизации, подтверж- высоконадежных и распределенных вы--дающего прием данных пассивным уст- числительных сетях ЭВМ. 5ройством (К СИП Б) к процессорам от

Целью изобретения является умень-пассивного внешнего устройства, кошение времени восстановления работо-торый в соответствии с дисциплиной способности аа счет организации по-обмена должен поступить в процессо- вторных циклов вывода информации вры спустя 10 мкс после обращения к магистраль, Овнешнему устройству. Каждьй случай

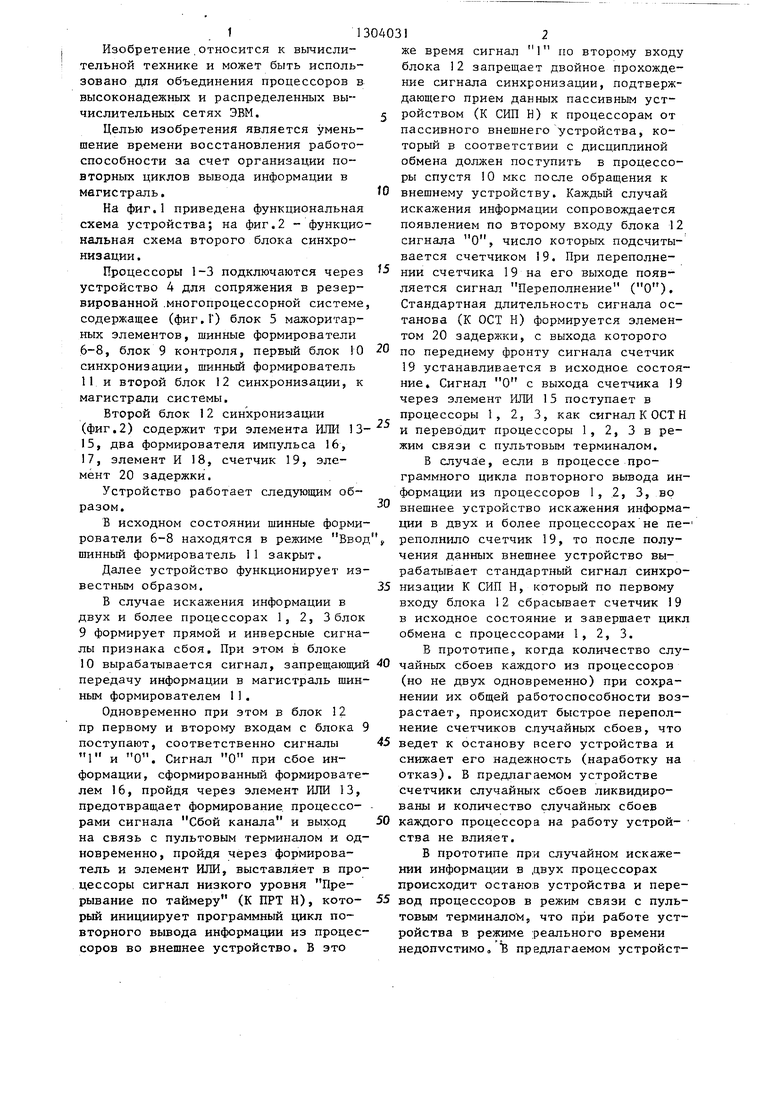

На фиг.1 приведена функциональнаяискажения информации сопровождается

схема устройства; на фиг.2 - функцио-появлением по второму входу блока 12

нальная схема второго блока синхро-сигнала О, число которых подсчитынизации.вается счетчиком 19. При переполнеПроцессоры 1-3 подключаются через счетчика 19 на его выходе появустройство 4 для. сопряжения в резер-ляется сигнал Переполнение (О),

вированной .многопроцессорной системе,Стандартная длительность сигнала оссодержащее (фиг.Г) блок 5 мажоритар-такова (К ОСТ Н) формируется элеменных элементов, шинные формирователитом 20 задержки, с выхода которого

6-8, блок 9 контроля, первый блок 10 0по переднему фронту сигнала счетчик

синхронизации, шинный формирователь19 устанавливается в исходное состоя11 и второй блок 12 синхронизации, кние. Сигнал О с выхода счетчика 19

магистрали системы.через элемент ИЛИ 15 поступает в

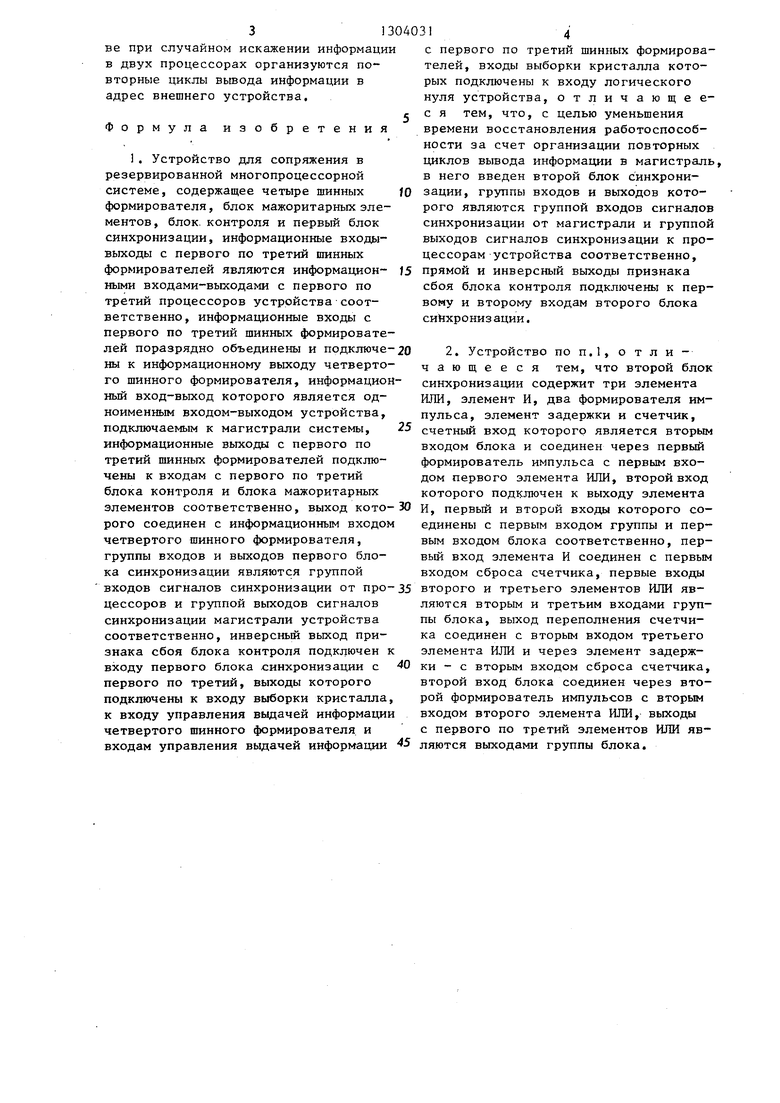

Второй блок 12 синхронизациипроцессоры 1, 2, 3, как сигнал К ОСТН

(фиг.2) содержит три элемента ИЛИ 13-и переводит процессоры 1, 2, 3 в ре15, два формирователя импульса 16,жим связи с пультовым терминалом. 17, элемент И 18, счетчик 19, эле- В случае, если в процессе промёнт 20 задержки.граммного цикла повторного вывода инУстройство работает следующим об-формации из процессоров 1, 2, 3, во

разом.- внешнее устройство искажения информаВ исходном состоянии шинные форми-ции в двух и более процессорах не пе- рователи 6-8 находятся в режиме Ввод,реполнило счетчик 19, то после полушинный формирователь 11 закрыт.чения данных внешнее устройство выДалее устройство функционирует из-рабатывает стандартный сигнал синхровестным образом.35низации К СИП Н, который по первому

В случае искажения информации ввходу блока 12 сбрасьгеает счетчик 19

двух и более процессорах 1, 2, 3 блокв исходное состояние и завершает цикл

9формирует прямой и инверсные сигна-обмена с процессорами 1, 2, 3.

лы признака сбоя. При этом в блоке В прототипе, когда количество слу10вырабатывается сигнал, запрещающий 40чайных сбоев каждого из процессоров передачу информации в магистраль шин-(но не двух одновременно) при сохра- ным формирователем 11.нении их общей работоспособности воз- Одновременно при этом в блок 12растает, происходит быстрое переполпр первому и второму входам с блока 9нение счетчиков случайных сбоев, что

поступают, соответственно сигналы 45ведет к останову всего устройства и

1 и О. Сигнал О при сбое ий-снижает его надежность (наработку на

формации, сформированный формировате-отказ). В предлагаемом устройстве

лем 16, пройдя через элемент ИЛИ 13,счетчики случайных сбоев ликвидиропредотвращает формирование, процессо- -ваны и количество случайных сбоев

рами сигнала Сбой канала и выход 50каждого процессора на работу устройна связь с пультовым терминалом и од-ства не влияет.

новременно, пройдя через формирова- В прототипе при случайном искажетель и элемент ИЛИ, выставляет в про-нии информации в двух процессорах

цессоры сигнал низкого уровня Пре-происходит останов устройства и перерывание по таймеру (К ПРТ Н), кото- 55вод процессоров в режим связи с пульрый инициирует программный цикл по-товым терминалов, что при работе уствторного вывода информации из процес-ройства в режиме реального времени

соров во внешнее устройство. В этонедопустимо В предлагаемом устройстве при случайном искажении информаци в двух процессорах организуются повторные циклы вывода информации в адрес внешнего устройства.

Формула изобретения

1. Устройство для сопряжения в резервированной многопроцессорной системе, содержащее четыре шинных формирователя, блок мажоритарных элементов, блок, контроля и первый блок

синхронизации, информационные входы- вьпсоды с первого по третий шинных формирователей являются информационными входами-выходами с первого по третий процессоров устройства соответственно, информационные входы с первого по третий шинных формирователей поразрядно объединены и подключены к информационному выходу четвертого шинного формирователя, информационный вход-выход которого является од- ноимен1п 1м входом-выходом устройства, подключаемым к магистрали системы, информационные выходы с первого по третий шинных формирователей подключены к входам с первого по третий блока контроля и блока мажоритарных

элементов соответственно, выход кото-30 и, первый и второй входы которого со- рого соединен с информационным входом четвертого шинного формирователя, группы входов и выходов первого блока синхронизации являются группой

единены с первым входом группы и первым входом блока соответственно, первый вход элемента И соединен с первым входом сброса счетчика, первые входы

входов сигналов синхронизации от про-35 второго и третьего элементов ИЛИ явцессоров и группой выходов сигналов синхронизации магистрали устройства соответственно, инверсный выход признака сбоя блока контроля подключен к входу первого блока синхронизации с 0 первого по третий, выходы которого подключены к входу выборки кристалла, к входу управления выдачей информации четвертого шинного формирователя и

ляются вторым и третьим входам пы блока, выход переполнения с ка соединен с вторым входом тр элемента ИЛИ и через элемент з ки - с вторым входом сброса сч второй вход блока соединен чер рой формирователь импульсов с входом второго элемента ИЛИ, в с первого по третий элементов

входам управления выдачей информации ляются выходами группы блока.

с первого по третий шинных формирователей, входы выборки кристалла которых подключены к входу логического нуля устройства, отличающеес я тем, что, с целью уменьшения времени восстановления работоспособности за счет организации повторных циклов вывода информации в магистраль, в него введен второй блок синхрони-

зации, группы входов и выходов которого являются группой входов сигналов синхронизации от магистрали и группой выходов сигналов синхронизации к процессорам устройства соответственно,

прямой и инверсный выходы признака сбоя блока контроля подключены к первому и второму входам второго блока сиМхрониз ации.

2. Устройство по п,1, отличающееся тем, что второй блок синхронизации содержит три элемента ИЛИ, элемент И, два формирователя импульса, элемент задержки и счетчик, счетный вход которого является вторым входом блока и соединен через первый формирователь импульса с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу элемента

и, первый и второй входы которого со-

единены с первым входом группы и первым входом блока соответственно, первый вход элемента И соединен с первым входом сброса счетчика, первые входы

ляются вторым и третьим входами группы блока, выход переполнения счетчика соединен с вторым входом третьего элемента ИЛИ и через элемент задержки - с вторым входом сброса счетчика, второй вход блока соединен через второй формирователь импульсов с вторым входом второго элемента ИЛИ, выходы с первого по третий элементов ИЛИ явРедактор М.Циткина

Составитель А.Ушаков

Техред В.Кадар Корректор с,Черни

Заказ 1313/50Тираж 673 Подписное

БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения в резервированной многопроцессорной системе | 1987 |

|

SU1501079A1 |

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

| Устройство обработки дискретной информации | 1982 |

|

SU1156087A1 |

| Устройство для имитации сбоев | 1990 |

|

SU1836684A3 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

| Устройство для контроля телефонных линий | 1990 |

|

SU1793557A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

Изобретение относится к области вычислительной техники и может быть использовано в высоконадежных многомашинных комплексах и сетях ЭВМ, при этом сокращается время восстановления работоспособности системы в случаях jj 1Jсбоя двух из трех резервированных процессоров, подключаемых посредством устройства к магистрали системы. Три процессора 1, 2, 3 подключаются к устройству 4, которое содержит блок 5 мажоритарных элементов, четыре шинных формирователя 6, 7, 8, 11, блок 9 контроля, первый блок 10 синхронизации, второй блок 12 синхронизации. В процессе синхронной работы процессоров 1, 2, 3 возможны случайные искажения информации, что приведет к останову устройства. Для его предотвращения служит блок 12, который формирует местные сигналы управления и организует повторные циклы передачи информации в адрес соответствующего устройства магистрали. 1 з.п, ф-лы, 2 ил. S (Л оо 4

| Патент США № 3921149, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство обработки дискретной информации | 1982 |

|

SU1156087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-15—Публикация

1985-07-01—Подача