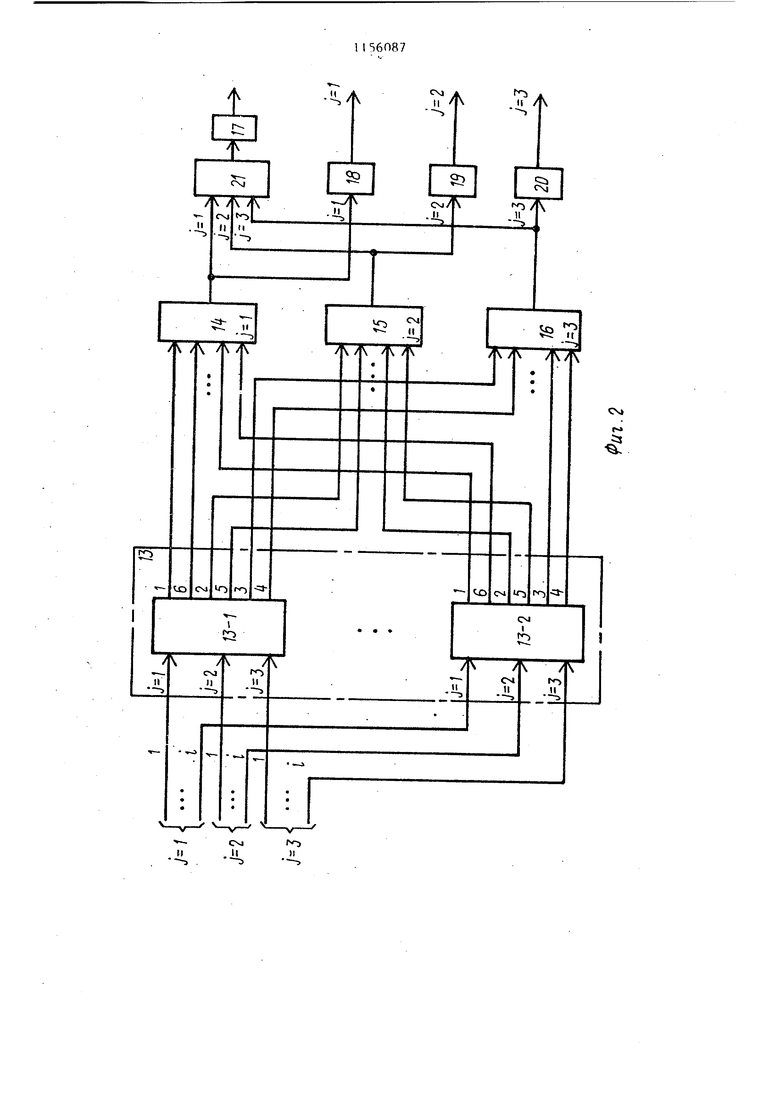

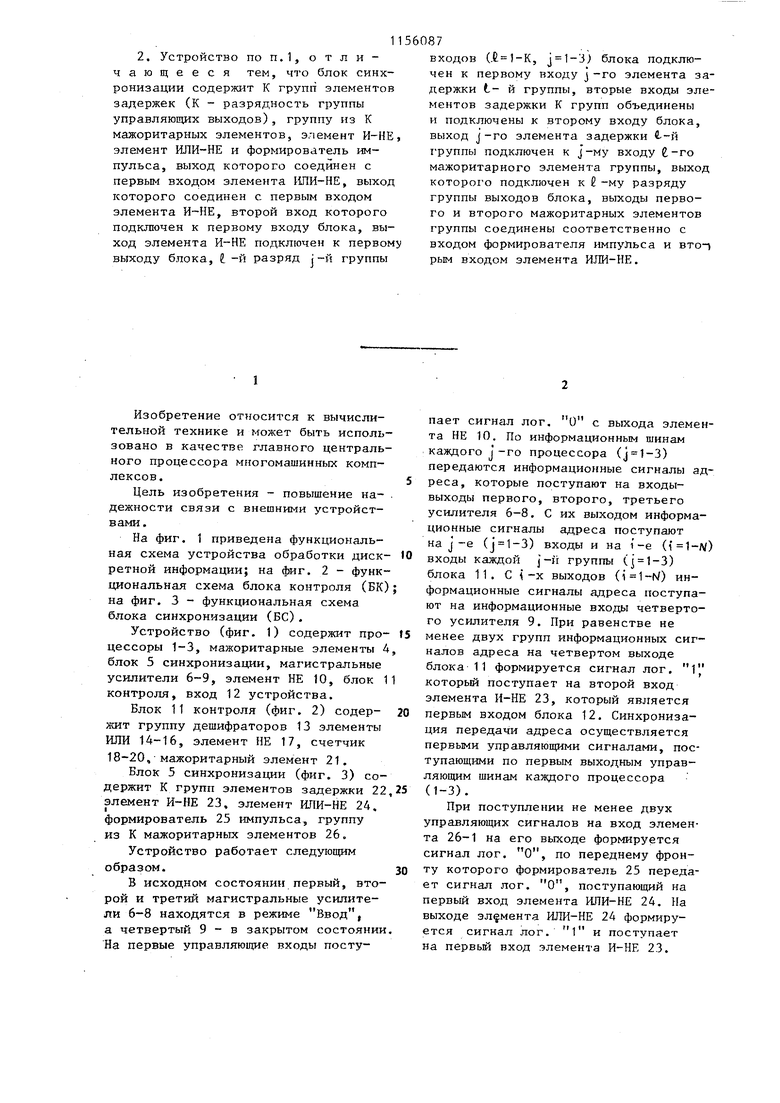

2. Устройство по п.1, отличающееся тем, что блок синхронизации содержит К групп элементов задержек (К - разрядность группы управляющих выходов), группу из К мажоритарных элементов, э.пемент И-НЕ элемент ИЛИ-НЕ и формирователь импульса, выход которого соединен с первым входом элемента НЛИ-НЕ, выход которого соединен с первым входом элемента , второй вход которого подключен к первому входу блока, выход элемента И-НЕ подключен к первом выходу блока, 2, -и разряд j-и группы входов (, j ) блока подключен к первому входу j-го элемента задержки t- и группы, вторые входы элементов задержки К групп объединены и подключены к второму входу блока, выход J -го элемента задержки Ь-й группы подключен к J-My входу -го мажоритарного элемента группы, выход которого подключен к -му разряду группы выходов блока, выходы первого и второго мажоритарных элементов группы соединены соответственно с входом формирователя импульса и вто- рым входом элемента ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения в резервированной многопроцессорной системе | 1987 |

|

SU1501079A1 |

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

| Устройство для обработки данных | 1982 |

|

SU1156086A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2002 |

|

RU2221267C1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Мажоритарно-резервированная магистральная модульная вычислительная система | 1986 |

|

SU1457643A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

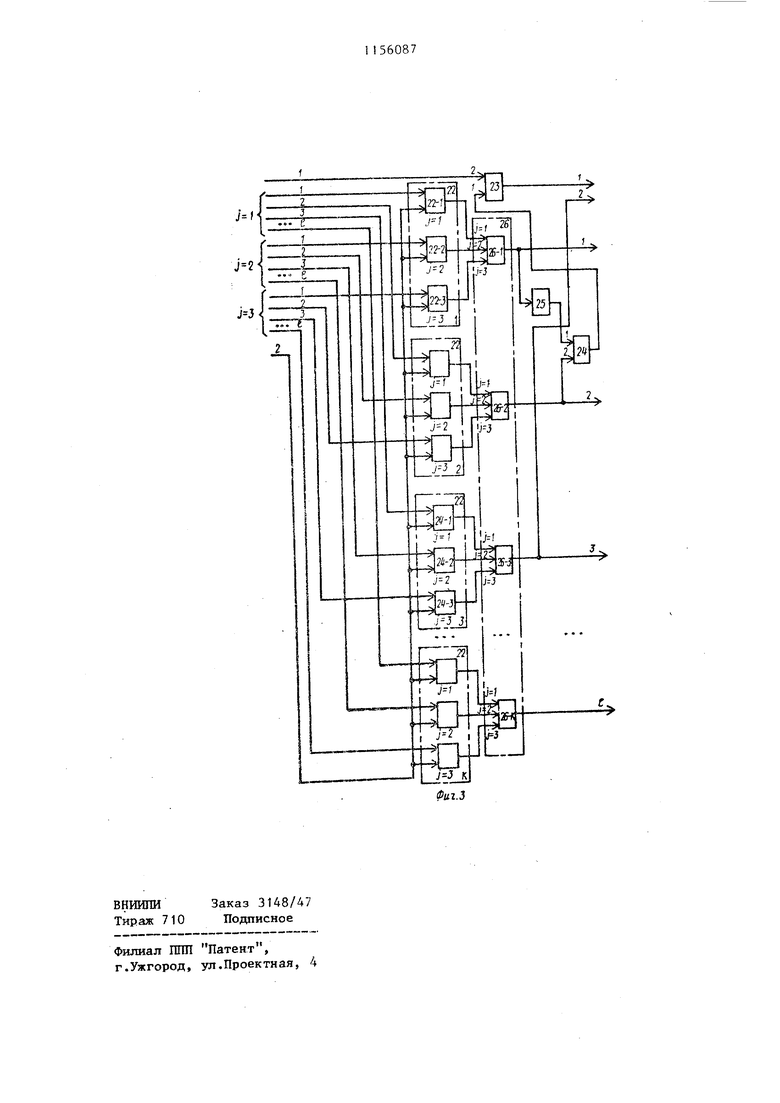

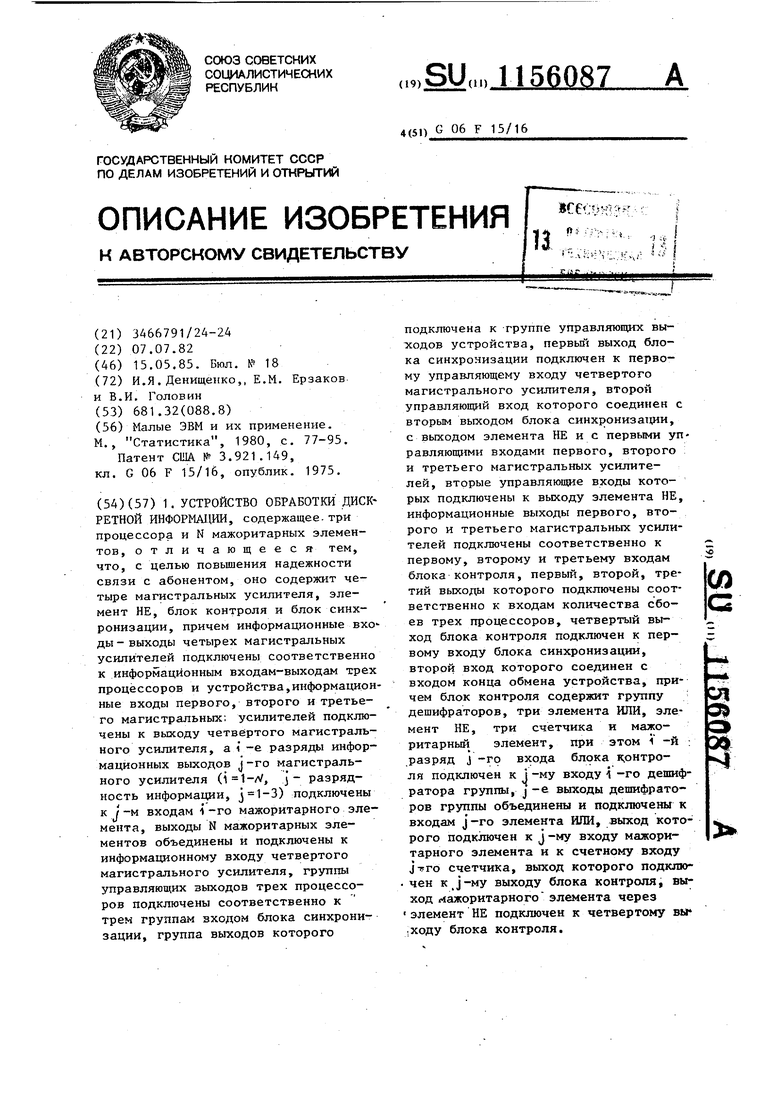

1. УСТРОЙСТВО ОБРАБОТКИ ДИСК РЕТНОЙ ИНФОРМАЦИИ, содержащее, три процессора и N мажоритарных элементов, отличающееся тем, что, с целью повьшения надежности связи с абонентом, оно содержит четыре магистральных усилителя, элемент НЕ, блок контроля и блок синхронизации, причем информационные вхо ды - выходы четырех магистральных усилителей подключены соответственно к информационным входам-выходам трех процессоров и устройства,информационные входы первого, второго и третьего магистральных; усилителей подключены к выходу четвёртого магистрального усилителя, а i-е разряды информационных выходов j-го магистрального усилителя (, j- разрядность информации, ) подключены к I -м входам 1 -го мажоритарного элемента, выходы N мажоритарных элементов объединены и подключены к информационному входу четвертого магистрального усилителя, группы управляющих выходов трех процессоров подключены соответственно к трем группам входом блока синхронизации, группа выходов которого подключена к группе управляющих выходов устройства, первьш выход блока синхронизации подключен к первому управляющему входу четвертого магистрального усилителя, второй управляющий вход которого соединен с вторым выходом блока cинxpoнизa p и, с выходом элемента НЕ и с первыми управляющими входами первого, второго : и третьего магистральных усилителей, вторые управляюи91е входы которых подключены к выходу элемента НЕ, информационные выходы первого, второго и третьего магистральных усилителей подключены соответственно к первому, второму и третьему входам блока контроля, первый, второй, треOf) тий выходы которого подключены соотс ветственно к входам количества сбоев трех процессоров, четвертый выход блока контроля подключен к первому входу блока синхронизации, второй вход которого соединен с входом конца обмена устройства, приCf| чем блок контроля содержит группу ф дешифраторов, три элемента ИЛИ, элемент НЕ, три счетчика и мажоритарный элемент, при этом V -и ; ЭФ разряд J -го входа блока к;онтроЧ ля подключен к J-му входу -го дешифратора группы, J-е выходы дешифраторов группы объединены и подключены к входам j-ro элемента ИЛИ, выход которого подключен к j-му входу мажоритарного элемента и к счетному входу j-яго счетчика, выход которого подключен к j-му выходу блока контроля, выход мажоритарного элемента через элемент НЕ подключен к четвертому вы ходу блока контроля.

Изобретение относится к вычислительной технике и может быть использовано в качестве главного центрального процессора многомашинных комплексов.

Цель изобретения - повышение надежности связи с внешними устройствами.

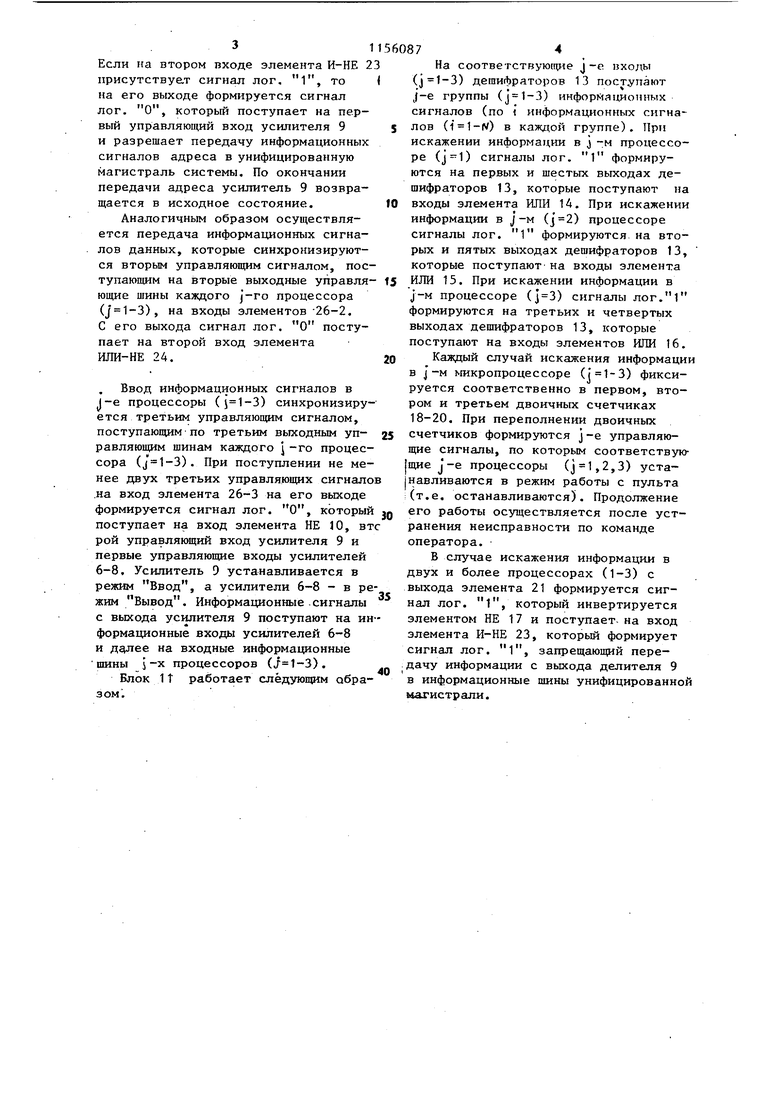

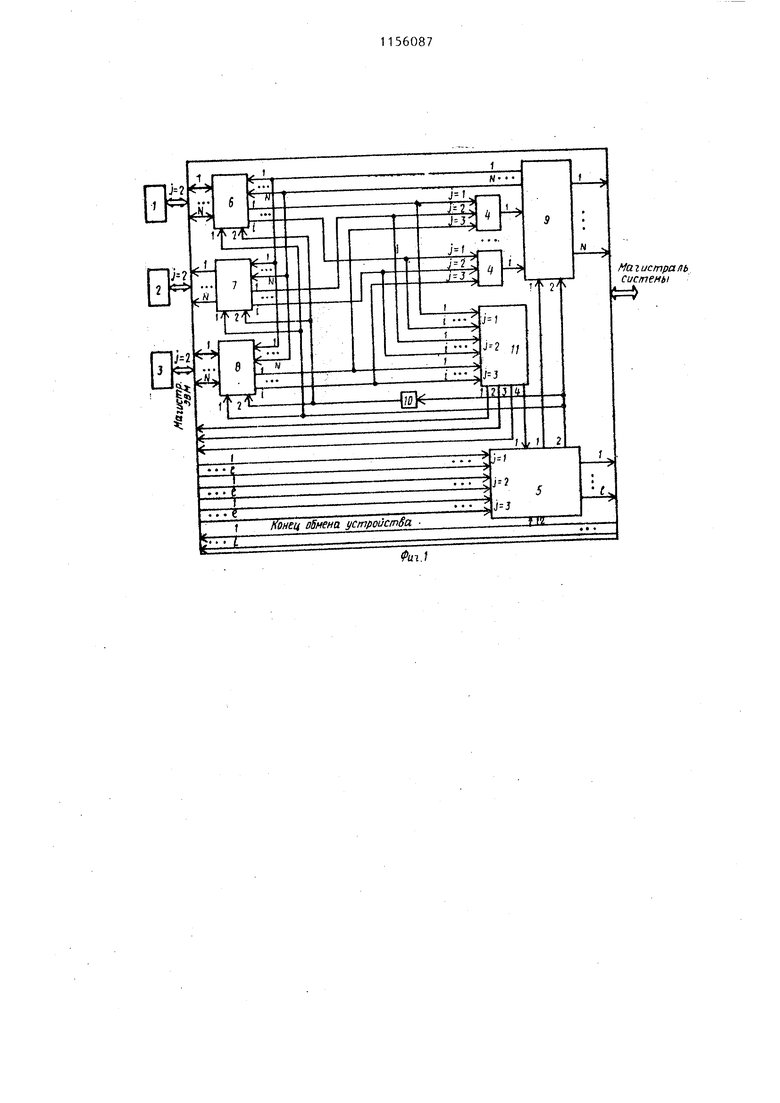

На фиг. 1 приведена функциональная схема устройства обработки дискретной информации; на фиг. 2 - функциональная схема блока контроля (БК) на фиг. 3 - функциональная схема блока синхронизации (БС).

Устройство (фиг. 1) содержит процессоры 1-3, мажоритарные элементы 4 блок 5 синхронизации, магистральные усилители 6-9, элемент НЕ 10, блок 1 контроля, вход 12 устройства.

Блок 11 контроля (фиг. 2) содержит группу дешифраторов 13 элементы ИЛИ 14-16, элемент НЕ 17, счетчик

18-20,-мажоритарный элемент 21.

Блок 5 синхронизации (фиг. 3) содержит К групп элементов задержки 22 элемент И-НЕ 23, элемент ИЛИ-НЕ 24. формирователь 25 импульса, группу из К мажоритарных элементов 26.

Устройство работает следуюпртм образом.

В исходном состоянии первый, второй и третий магистральные усилители 6-8 находятся в режиме Ввод, а четвертый 9 - в закрытом состоянии На первые управляющие входы поступает сигнал лог. О с выхода элемета НЕ 10. По информационным шинам каждого J-го процессора () передаются информационные сигналы адреса, которые поступают на входывыходы первого, второго, третьего усилителя 6-8. С их выходом информационные сигналы адреса поступают на J-е () входы и на 1-е ( входы каждой j-й группь ( 1-3) блока 11. С -X выходов () информационные сигналы адреса поступают на информационные входы четвертого усилителя 9. При равенстве не менее двух групп информационных сигналов адреса на четвертом выходе блока 11 формируется сигнал лог. 1 который поступает на второй вход элемента И-НЕ 23, который является первым входом блока 12. Синхронизация передачи адреса осуществляется первыми управляющими сигналами, поступающими по первым выходным управляющим шинам каждого процессора (1-3).

При поступлении не менее двух управляющих сигналов на вход элемента 26-1 на его выходе формируется сигнал лог. О, по переднему фронту которого формирователь 25 передает сигнал лог. О, поступающий на первый вход элемента РШИ-НЕ 24. На выходе элемента ИЛИ-НЕ 24 формируется сигнал лог. 1 и поступает на первьй вход элемента И-НЕ 23. 31 Если на втором входе элемента И-НЕ 2 присутствует сигнал лог, 1, то на его выходе формируется сигнал лог. О, который поступает на первый управляющий вход усилителя 9 и разрешает передачу информационных сигналов адреса в унифицированную магистраль системы. По окончании передачи адреса усилитель 9 возвращается в исходное состояние. Аналогичным образом осуществляется передача информационных сигналов данных, которые синхронизируются вторым управляющим сигналом, пос тупающим на вторые выходные управля ющие шины каждого -го процессора (j 1-3), на входы элементов-26-2. С его выхода сигнал лог. О поступает на второй вход элемента ИЛИ-НЕ 24. Ввод информационных сигналов в (-е процессоры () синхронизиру ется третьим управляющим сигналом, поступающим по третьим выходным управляющим шинам каждого -го процессора (). При поступлении не менее двух третьих управляющих сигнало .на вход элемента 26-3 на его выходе формируется сигнал лог. О, который поступает на вход элемента НЕ 10, вт рой управляющий вход усилителя 9 и первые управляющие входы усилителей 6-8. Усилитель D устанавливается в режим Ввод, а усилители 6-8 - в р жим Вывод. Информационные .сигналы с выхода усилителя 9 поступают на и формационные входы усилителей 6-8 и на входные информационные шины j-X процессоров ). Блок 1Т работает следующим обра зом. 7 На соответствую(аие j-е входы () дешифраторов 13 пост.упают j-e группы () инфорК{яциоиных сигналов (по информационных сигналов (V) в каждой группе). При искажении информации в -м процессоре () сигналы лог. Г формируются на первых и шестых выходах дешифраторов 13, которые поступают на входы элемента ИЛИ 1А. При искажении информации в () процессоре сигналы лог. Г формируются на вторых и пятых выходах дешифраторов 13, которые поступают на входы элемента ИЛИ 15. При искажении информации в J-M процессоре (3) сигналы лог.Г формируются на третьих и четвертых выходах дешифраторов 13, которые поступают на входы элементов ШШ 16. Каждый случай искажения информации в J-м микропроцессоре ((1-3) фиксируется соответственно в первом, втором и третьем двоичных счетчиках 18-20. При переполнении двоичных счетчиков формируются j-е управляющие сигналы, по которым соответствующие j-e процессоры (j 1,2,3) устанавливаются в режим работы с пульта (т.е. останавливаются). Продолжение его работы осуществляется после устранения неисправности по команде оператора. В случае искажения информации в двух и более процессорах (1-3) с выхода элемента 21 формируется сигнал лог. 1, который инвертируется элементом НЕ 17 и поступает- на вход элемента И-НЕ 23, который формирует сигнал лог. 1, запрещающий передачу информации с выхода делителя 9 в информационные шины унифицированной магистрали.

Магистраль системы

| Малые ЭВМ и их применение | |||

| М., Статистика, 1980, с | |||

| Спускная труба при плотине | 0 |

|

SU77A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1985-05-15—Публикация

1982-07-07—Подача