Изобретение относится к вычислительной технике и может быть использовано, например, в качестве центрального процессора в АСУ технологическими процессами или в АСУ в атомной энергетике, где требуется повышенная надежность.

Цель изобретения - повышение надежности и снижение времени восстановления системы.

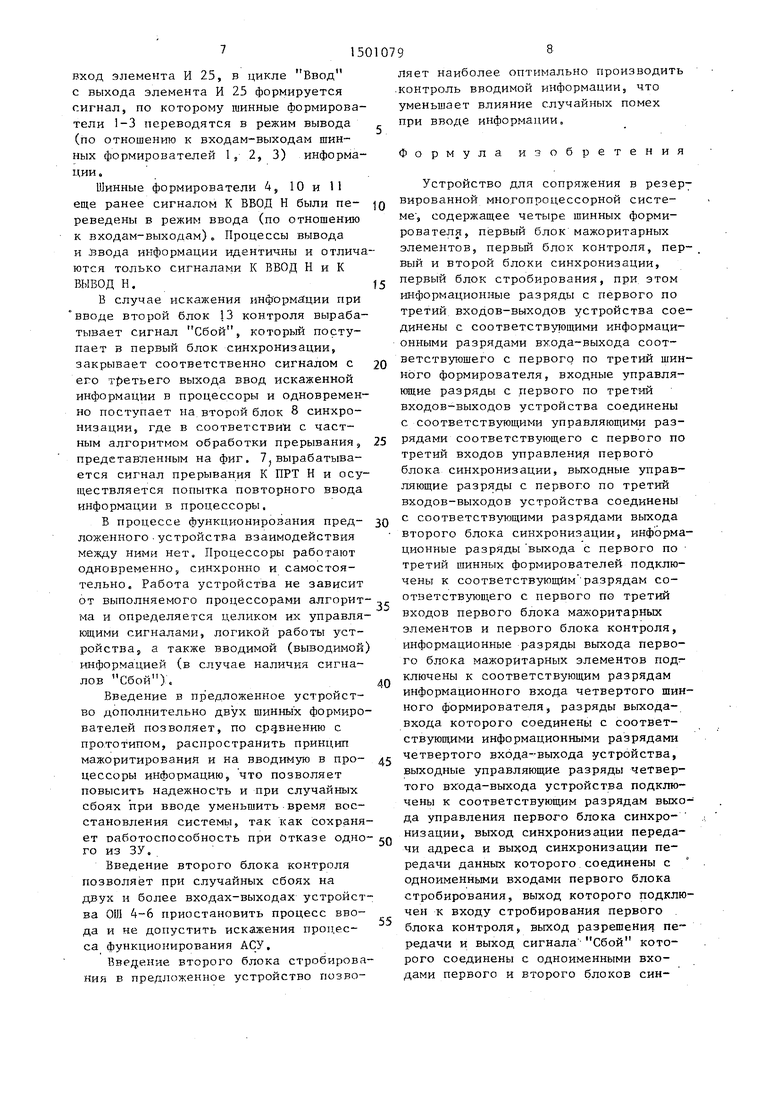

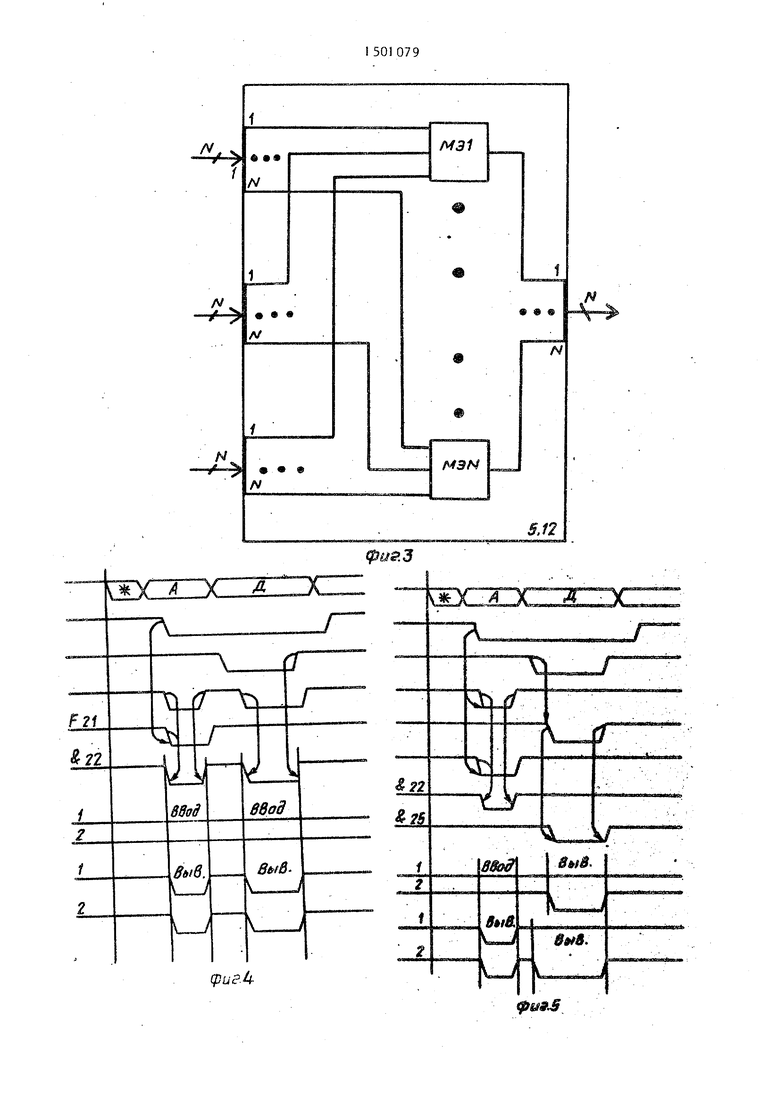

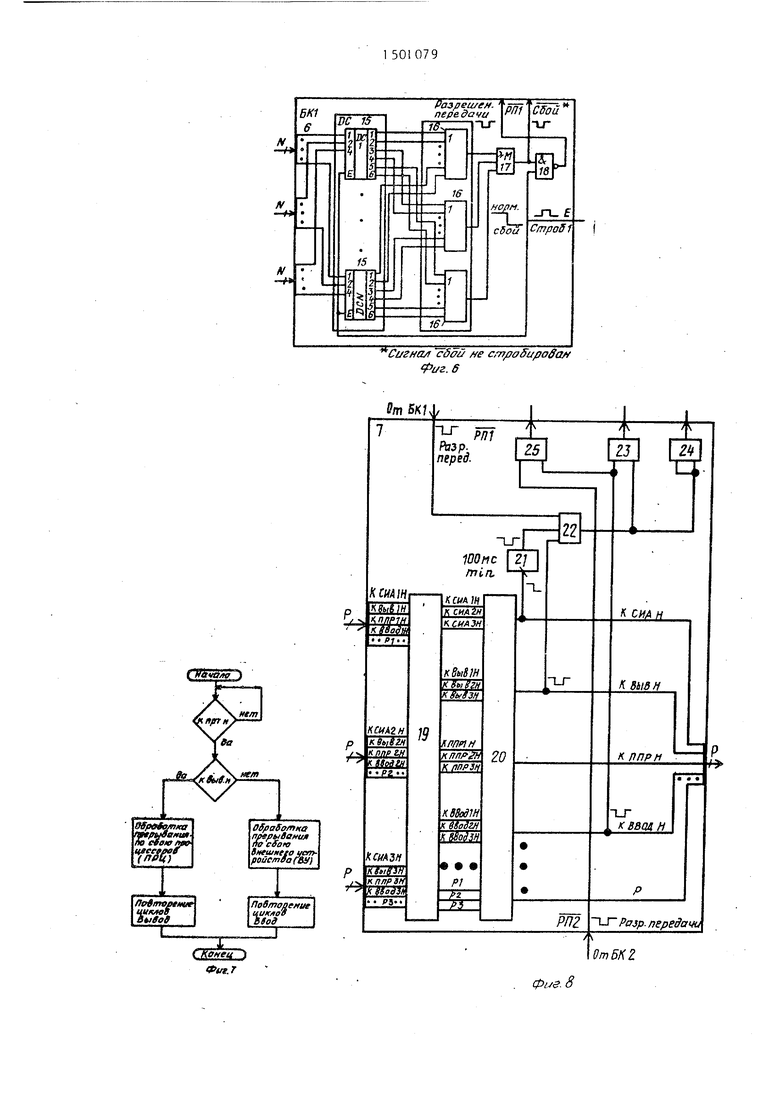

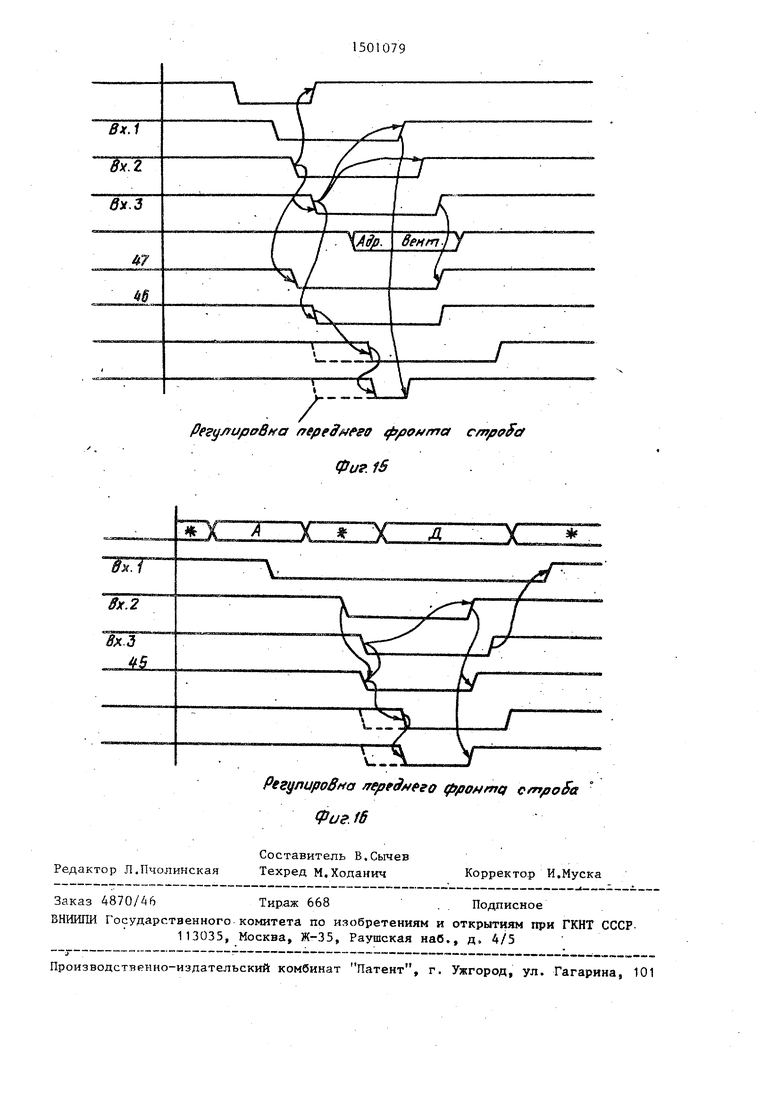

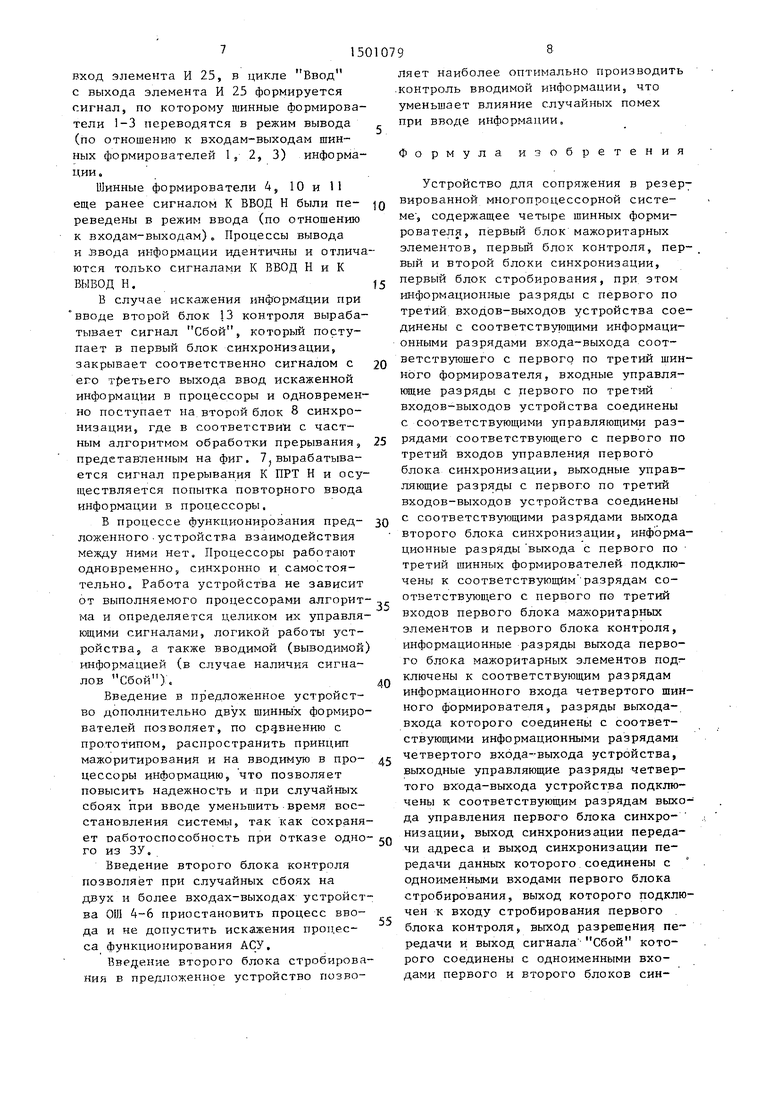

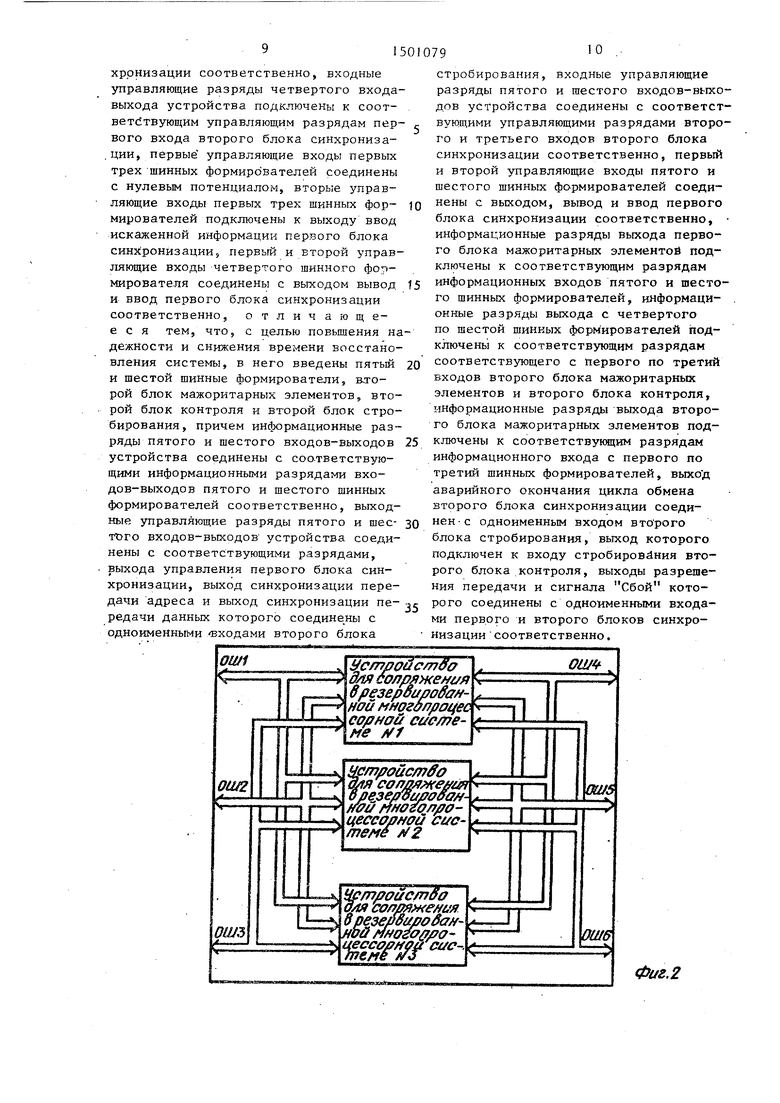

На фиг. 1 и 2 представлены функциональная схема устройства и вариант его выполнения, соответственно; на фиг. 3 - функциональная схема первого и второго блоков -мажоритар- ных элементов; на фиг. 4 и 5 - временные диаграммы работы устройства при выводе и вводе информации; на

фиг. 6. и 7 - функциональная схема первого блока контроля и алгоритм подпрограммы обработки прерывания по сигналу КПРТ -Н соответственно; на

сигналов, группа из-Р мажоритарных М элементов 20 (Р - разрядность вход ного управления сообщением), форми5 рователь 21, элемент ИЛИ-И 22, элементы ИЛИ 23 и 24, элемент И 25.

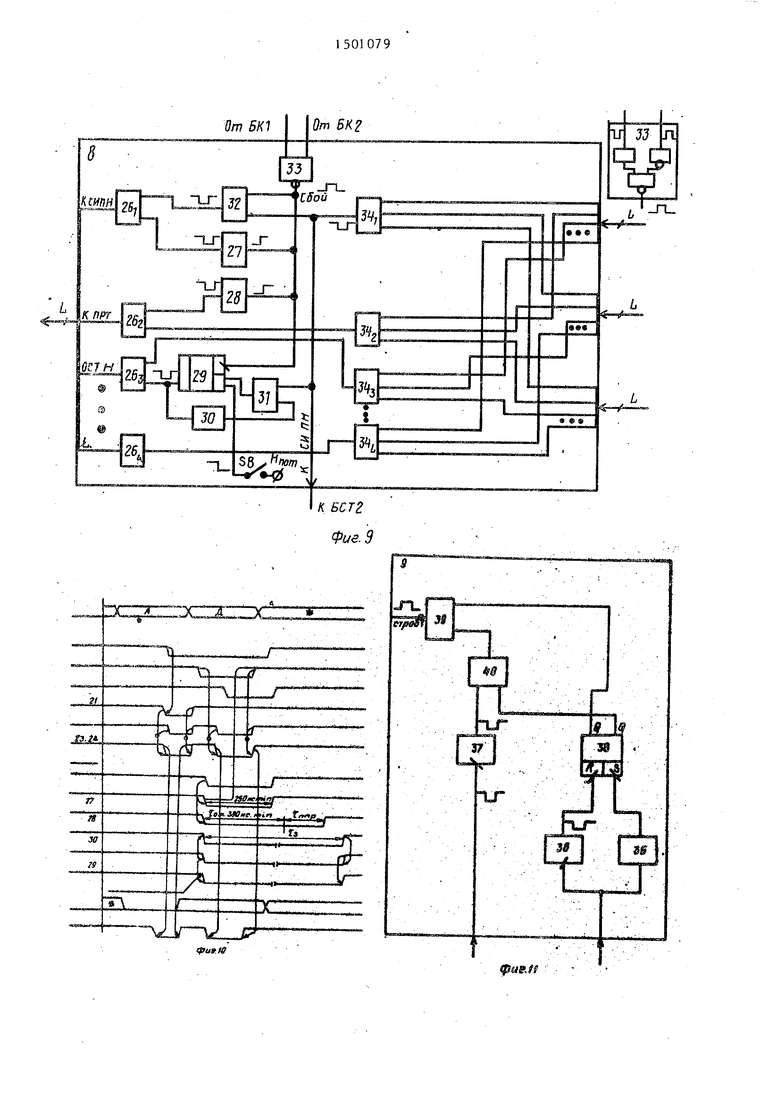

Второй блок 8 синхронизации содержит группу из L элементов ИЛИ 26 (L - разрядность выходного управле10 НИН сообщением), два формирователя 27 и 28, двоичный счетчик 29, элемент 30,задержки, элемент ИЛИ 31, элемент И 32, элемент ИЛИ-НЕ 33, группу из L мажоритарных 5 М элемен15 тов 34, .

Первый блок стробирования 9 состоит из элемента 35 задержки двух формирователей 36 и 37, триггера 38, элемента ИЛИ-НЕ 39 и элемент И 40.

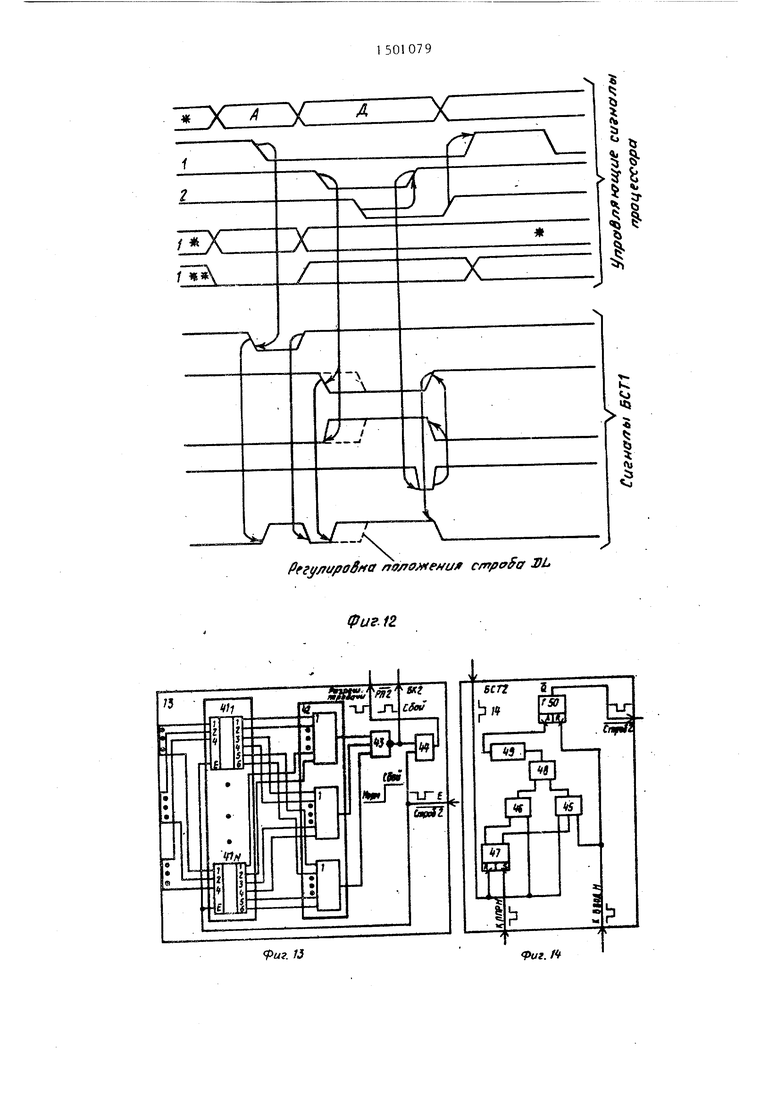

Второй блок контроля 13 содержит элементы, аналогичные по -своим выполняемым функциям и составу элементам первого блока контроля: группу

ИЛИ 42, мажоритарный М элемент 43 и элемент И 44, ,

фиг. 8 - функциональная схема первого 25 дешифраторов 41, группу элементов блока синхронизации; на фиг. 9 и 10- фун| циой альная схема и временная диаграмма работы второго блока синхронизации соответственно; на фиг.11

30

и 12 - функциональная схема первого блока стробирования и его временная диаграмма работы соответственно; на 13 - функциональная схема второго блока контроля; на фиг 14 - функциональная схема второго блока стробирования; на фиг. 15 и 16 - временные диаграммы работы второго блока стробирования при вводе информации и при вводе информации по прерыванию соответственно .

35

40

Мажоритарный М элемент 43 в отличие от элемента 17 осуществляет инвертирование выходного сигнала; элемент И 44 в отличие от элемента И-НЕ 18 не инвертирует выходной сиг-. нал.

Второй блок 14 стробирования (фиг. 14) содержит два элемента И 45 и 46, триггер 47, элемент ИЛИ 48, элемент 49 задержки и формирова тель 50.

Устройство работает следующим образом.

Устройство содержит шинные формирователя 1-4, первый блок 5. мажоритарных элементов, первый блок 6 контроля, первый 7 и второй 8 блоки .син- хройизации, первый блок 9 стробирования, шинные формирователи 10 и 11, второй блок 12 мажоритарных элементов, второй блок 13 контроля и второй блок 14 стробирования.

Первый блок 5 мажоритарных элемен- тов состоит из N Мажоритарных элементов (N - информационная разрядность сообщений).

Первый блок контроля содержит: группу из N дешифраторов 15, группу из трех элементов ИЛИ .16, мажоритарный Мэлемент 17 и элемент И-НЕ 18,

Первый блок 7 синхронизации об- раз тот узел 19 монтажной разводки

сигналов, группа из-Р мажоритарных М элементов 20 (Р - разрядность входного управления сообщением), формирователь 21, элемент ИЛИ-И 22, элементы ИЛИ 23 и 24, элемент И 25.

Второй блок 8 синхронизации содержит группу из L элементов ИЛИ 26 (L - разрядность выходного управлеНИН сообщением), два формирователя 27 и 28, двоичный счетчик 29, элемент 30,задержки, элемент ИЛИ 31, элемент И 32, элемент ИЛИ-НЕ 33, группу из L мажоритарных 5 М элементов 34, .

Первый блок стробирования 9 состоит из элемента 35 задержки двух формирователей 36 и 37, триггера 38, элемента ИЛИ-НЕ 39 и элемент И 40.

Второй блок контроля 13 содержит элементы, аналогичные по -своим выполняемым функциям и составу элементам первого блока контроля: группу

ИЛИ 42, мажоритарный М элемент 43 и элемент И 44, ,

дешифраторов 41, группу элементо

дешифраторов 41, группу элементов

Мажоритарный М элемент 43 в отличие от элемента 17 осуществляет инвертирование выходного сигнала; элемент И 44 в отличие от элемента И-НЕ 18 не инвертирует выходной сиг-. нал.

Второй блок 14 стробирования (фиг. 14) содержит два элемента И 45 и 46, триггер 47, элемент ИЛИ 48, элемент 49 задержки и формирова тель 50.

Устройство работает следующим образом.

В исходном состоянии все элементы, требующие установки в исходное состояние (регистры, триггеры, счетчики), установлены. Рассмотрим работу предложенного устройства,на примерах двух циклов обмена информации цикла Вывод и цикла Ввод информации.

Дпя выполнения любой команды процессорам в резервированной системе, в составе которой работает .предложенное устройство, требуется выполнить хотя бы одну операцию обращения к каналу. Первой такой операцией для всех команд является ввод данных из ячейки памяти, адрес которой определяется счетчиком команд.

В исходном, состоянии щинные формирователи 1-3 открыты и работают в режиме Ввод информации (ввод по

отношению к входам-выходам шинных формирователей 1-3), В соответствии с временными Диаграммами работы (фиг. 4 и 5)сигнал К СИЛ Н на выходе элемента М 20 сигнализирует о наличии адреса не менее чем на двух магистралях системы (входах-выходах устройства ОШ 1-3). По переднему фронту этого сигнала F 21 формируется сигнал, по которому при наличии разрешающего сигнала на 3-м входе элемента ИЛИ-И 22 через элементы ИЛИ 23 и 24 открываются выходные шинные формирователи 4, 10 и 11 устройства (т,е. переводятся по отношению к входам-выходам шинных формирователей 4, 10 и 11 в режим вывода).

Разрешающий сигнал на 3-й вход элемента ИЛИ-И 22 формируется

при наличии на выходе первого блока 9 стробирования разрешающего сигнала Строб 1, который поступает на вход Е первого блока контроля 6;

- при отсутствии искажений информации в двух и более процессорах (в данном случае идентичность адреса на любых двух процессорах), что сопроводается наличием высокого уровня В на выходе элемента Ь М 17.

При наличии этих условий на выходе элемента И-НЕ 18 формируется сиг- bian Разрешение-передачи 1 (РП), которьй и разрешает открытие шинных формирователей 4, 10 и П.

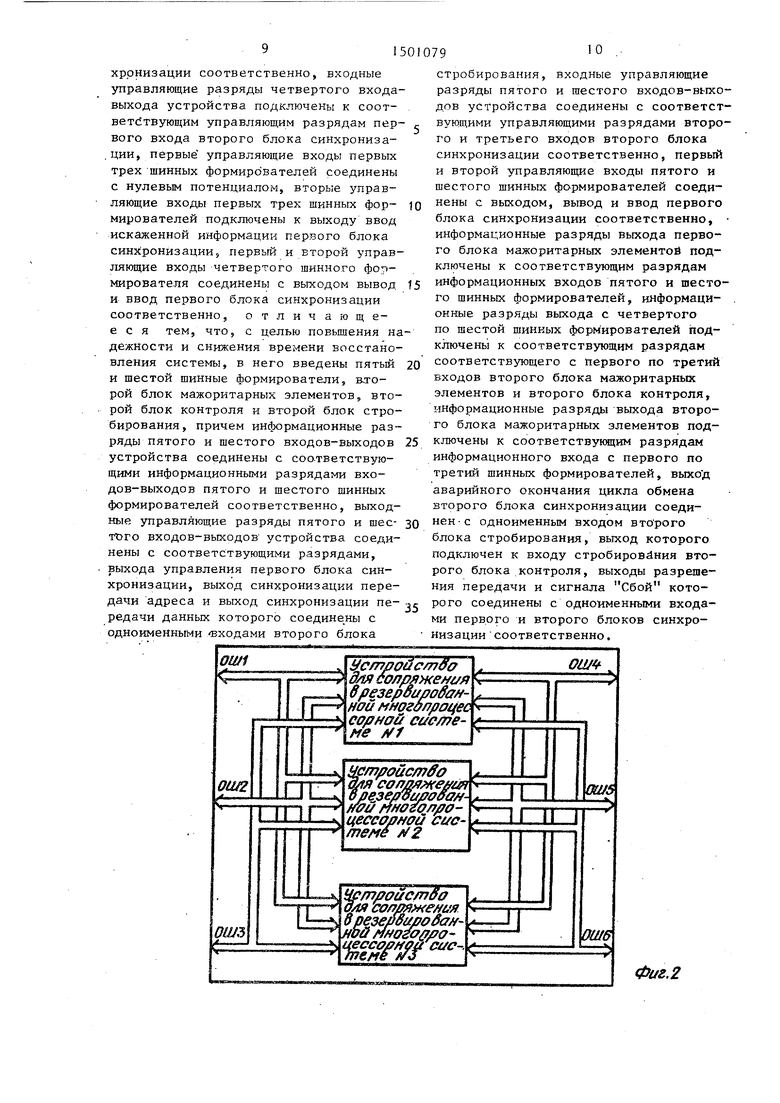

При наличии искажений адреса в двух и более процессорах на выходе элемента М 17 формируется нестроби- рованный сигнал низкого уровня Сбой который поступает на второй блок 8 синхронизации, где инвертируется элементом ИПИ-НЕ 33. Сигнал Сбой с этого элемента поступает на вход формирователей 27 и 28 и на 1-й вхоД элемента И 32, По переднему фронту, сигнала Сбой формирователи 27 и 28 формируют стандартные сигналы, которые соответственно поступают на элементы ИЛИ 26 и далее в каналы процессоров на входы-выходы устройства ОП) 1-3, По первому сигналу (местный сигнал К СИП Н) заканчивается неудавшийся цикл обмена, а по второму (сигнал требования прерывания К ПРТ Н) инициируется подпрограмма повторных циклов вывода информации или ввода (фиго 7)

0

5

0

0

5

Каждая неудавшаяся попытка произвести цикл обмена подсчитывается в счетчике 29. При его переполнении на выходе соответствующего элемента ИЛИ 26 формируется сигнал останова ОСТ Н,

Если искажения адреса не произошло и шинные формирователи 4, 10 и И открыты, то адрес поступает на входы- выходы устройства ОШ 4, 5, 6 и далее в ЗУ, соответственно связанные с ни- . ми. По этому адресу с этих ЗУ считывается соответствующая команда и код команды поступает на входы-выходы устройства ОШ 4-6 и далее на входы-выходы шинных формирователей 4, 10 и 11.

Внешние устройства (в данном случае ЗУ) помещают данные на линии ДА (в данном случае код команды) и вырабатывают сигналы К СИП Н, сигнализирующие о том, что данные (код команды) находятся в соответствующих каналах (входах-выходах устройства 4-6)., :

При наличии не менее двух кодов команды на входах-выходах устройства ОШ 4-6 с выхода элемента i М 34 передается сигнал К СИП Н, который поступает на вход аварийного окончания цикла обмена второго блока 1.4 стробирования по которому через элемент И 45, где в цикле Ввод на.3-м входе имеется разрешающий потенциал, и далее через элемент ИЛИ 48 и элемент 5 49 по переднему фронту запускается формирователь 50.

С выхода формирователя 50 формируется разрешающий сигнал Строб 2, Передний фронт строба регулируется элементом 49. Сброс сигнала Строб 2 происходит по окончании приема данных (кода команды) процессорами,

о чем они сигнализируют снятием сигнала К ВВОД Н.

По сигналу Строб 2, поступающему на вход стробирования второго блока контроля 13 при отсутствии/искажений кода команды на двух и более входах-выходах устройства ОШ 4-6 (или в 2-х и более ЗУ, так как искажения кода команды происходить и между ЗУ и вторым блоком контроля 13) с выхода элемента И 44 формируется сигнал, разрешающий передачу информации 5 (код команды) РП2.

По этому сигналу РП2, поступающему на вход разрешения передачи первого блока синхронизации и далее на 2-й

0

5

U

вход элемента И 25, в цикле Ввод с выхода элемента И 25 формируется сигнал, по которому шинные формирователи 1-3 переводятся в режим вывода (по отношению к входам-выходам шинных формирователей 1, 2, 3) информации.

Шинные формирователи 4, 10 и 11 еще ранее сигналом К ВВОД Н были пе- реведены в режим ввода (по отношению к входам-выходам)„ Процессы вывода и ввода информации идентичны и отличаются только сигналами К ВВОД Н и К ВЫВОД Н.

В случае искажения инф орма:ции при вводе второй блок 13 контроля вырабатывает Сигнал Сбой, который пос.ту- пает в первый блок синхронизации, закрывает соответственно сигналом с его третьего выхода ввод искаженной информации в процессоры и одновременно поступает на второй блок 8 синхро- низации, где в соответствии с частным алгоритмом обработки прерывания, предетав ленным на фиг. 7j вырабатывается сигнал прерывания К ПРТ Н и осуществляется попытка повторного ввода информации в процессоры,

В процессе функционирования пред- ложенного.устройства взаимодействия между ними нет. Процессоры работают одновременно, синхронно и самостоятельно. Работа устройства не зависит от выполняемого процессорами алгоритма и определяется целиком их управля юн;ими сигналами, логикой работы устройства, а также вводимой (выводимой информацией (в случае наличия сигналов Сбой).

Введение в предложенное устройство дополнительно двух шинных формирователей позволяет, по сравнению с прототипом, распространить принцип мажоритирования и на вводимую в про- цессоры информацию, что позволяет повысить надежность и при случайных сбоях при вводе уменьшить время восстановления системы, так как сохраняет работоспособность при отказе одно го из ЗУ.

Введение второго блока контроля позволяет при случарЧных сбоях на двух и более входах-выходах устройства ОШ 4-6 приостановить процесс ввода и не допустить искажения процесса функционирования АСУ.

Введение второго блока стробирова ния в предложенное устройство позво

а ,- а15010798

Ляет наиболее оптимально производить .контроль вводимой информации, что уменьшает влияние случайных помех при вводе информации.

Формула

и

зобоетения

Q 5

0 5

О 0

З Q

5

Устройство для сопряжения в резервированной многопроцессорной системе , содержащее четыре шинных формирователя, первый блок мажоритарных элементов, первьй блок контроля, первый и второй блоки синхронизации, первый блок стробирования, при, этом информационные разряды с первого по третий входов-выходов устройства соединены с соответствующими информационными разрядами входа-выхода соответствующего с первого по третий шинного формирователя, входные управляющие разряды с первого по третий входов-выходов устройства соединены с соответствующими управляющими разрядами соответствующего с первого по третий входов управление первого блока синхронизации, выходные управляющие разряды с первого по третий входов-выходов устройства соединены с соответствующими разрядами выхода второго блока синхронизации, информационные разряды выхода с первого по третий шинных формирователей подключены к соответствующим разрядам соответствующего с первого по третий входов первого блока мажоритарных элементов и первого блока контроля, информационные разряды выхода первого блока мажоритарных элементов подг- ключены к соответствующим разрядам информационного входа четвертого шинного формирователя, разряды выхода- входа которого соединены с соответствующими информационными разрядами четвертого входа-выхода устройства, выходные управляющие разряды четвертого входа-выхода устройства подключены к соответствующим разрядам выхода управления первого блока синхро- низации, выход синхронизации передачи адреса и выход синхронизации передачи данных которого соединены с одноименными входами первого блока стробирования, выход которого подключен к входу стробирования первого блока контроля, выход разрешения пе редачи и выход сигнала Сбой которого соединены с одноименными входами первого и второго блоков сиихррнизации соответственно, входные управляющие разряды четвертого входа- выхода устройства подключены к соот- BeTdTByroi4HM управляющим разрядам пер- вого входа второго блока синхронизации, первые управляющие входы первых трех ШИННЫХ формирователей соединены с нулевым потенциалом, вторь;е управляющие входы первых трех шинных фор- мирователей подключены к выходу ввод искаженной информации первого блока синх ронизации, первьгй и второй управляющие входы четвертого шинного формирователя соединены с выходом вывод и ввод первого блока синхронизации соответственно, отличающееся тем, что, с целью повьпяения надежности и снижения времени восстановления системы, в него введены пятый и шестой шинные формирователи, в-то- рой блок мажоритарных элементов, второй блок контроля и второй блок стро- бирования, причем информационные разряды пятого и шестого входов-выходов устройства соединены с соответствующими информационными разрядами входов-выходов пятого и шестого шинных формирователей соответственно, выходные зшравляющие разряды пятого и шее- того ВХОДОВ-ВЫХОДОВ устройства соединены с соответствующими разрядами, выхода управления первого блока синхронизации, выход синхронизации передачи адреса и выход синхронизации передачи данных которого соединены с одноименными /входами второго блока

г o 5 0 5 О

5

стробирования, входные управляющие разряды пятого и шестого входов-выходов устройства соединены с соответствующими управляющими разрядами второго и третьего входов второго блока синхронизации соответственно, первый и второй управляющие входы пятого и шестого шинных формирователей соединены с выходом, вывод и ввод первого блока синхронизации соответственно, информационные разряды выхода первого блока мажоритарных элементой подключены к соответствующим разрядам информационных входов пятого и шестого шинных формирователей, информационные разряды выхода с четвертого по шестой шинных формирователей подключены к соответствующим разрядам соответствующего с первого по третий входов второго блока мажоритарных элементов и второго блока контроля, информационные разряды выхода второго блока мажоритарных элементов подключены к соответствуннцим разрядам информационного входа с первого по третий шинных формирователей, выход аварийного окончания цикла обмена второго блока синхронизации соединен -с одноименным входом вто рого блока стробирозания, выход которого подключен к входу стробировйния второго блока контроля, выходы разрешения передачи и сигнала Сбой которого соединены с одноименными входами первого и второго блоков синхронизации соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное процессорное устройство | 1987 |

|

SU1594545A1 |

| Устройство обработки дискретной информации | 1982 |

|

SU1156087A1 |

| Устройство для сопряжения в резервированной многопроцессорной системе | 1985 |

|

SU1304031A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1986 |

|

SU1363226A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1522216A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

Изобретение относится к вычислительной технике и может быть использовано в АСУ ТП. Целью изобретения является повышение надежности и снижение времени восстановления системы. Предложенное устройство содержит шинные формирователи 1, 4, 10, 11, блоки мажоритарных элементов 5, 12, блоки контроля 6, 13, блоки синхронизации 7, 8, блоки стробирования 9, 14. Устройство сопрягает три идентичных процессора с тремя идентичными наборами внешних устройств. Три процессора выполняют одинаковые инструкции (счет) и передачу через устройство сопряжения информации (результатов вычислений) после мажоритарной обработки в адрес внешних устройств. Данные от трех наборов внешних устройств (например, ОЗУ) также поступают в устройство сопряжения, где происходит их мажоритарная обработка, и далее в адрес трех процессоров. Принимаемая и выдаваемая информация в предлагаемом устройстве контролируется соответственно блоками контроля. Моменты приема и выдачи информации при отсутствии искажений стробируются соответственно двумя блоками стробирования. Два блока синхронизации управляют работой устройства при приеме-выдаче информации. 16 ил.

Фиг.2

Cffgwg j Ф(ге.Г

агна/ cdoi/ ме cmflafuflaeiM фцг.б

Физ. 8

Wj

tb

M

Ш о

t

Pfey t/floSffcf nff/ro effUJt DL

9иг IS

Фиг. f2

. 14

JT.f

Ж2

в.З

47

V-J:

/

Pesy uflffBffo frepeS f ao c/n/j0fcf

Фи. 1$

Х/. I бемт.} У

vj

Ap

| Патент США № 4358824, кл, G 06 F 11/20, опублик | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Устройство для сопряжения в резервированной многопроцессорной системе | 1987 |

|

SU1441412A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-28—Подача