1

Изобретение относится к вычислительной технике и может быть использовано в цифровых и аналого-цифровы вычислительных комплексах, устройст вах управления позиционированием схвата манипуляционного робота, системах интерактивной машинной график

Целью изобретения является расширение области применения за счет дополнительной возможности преобразования исходных последовательносте аргументов.

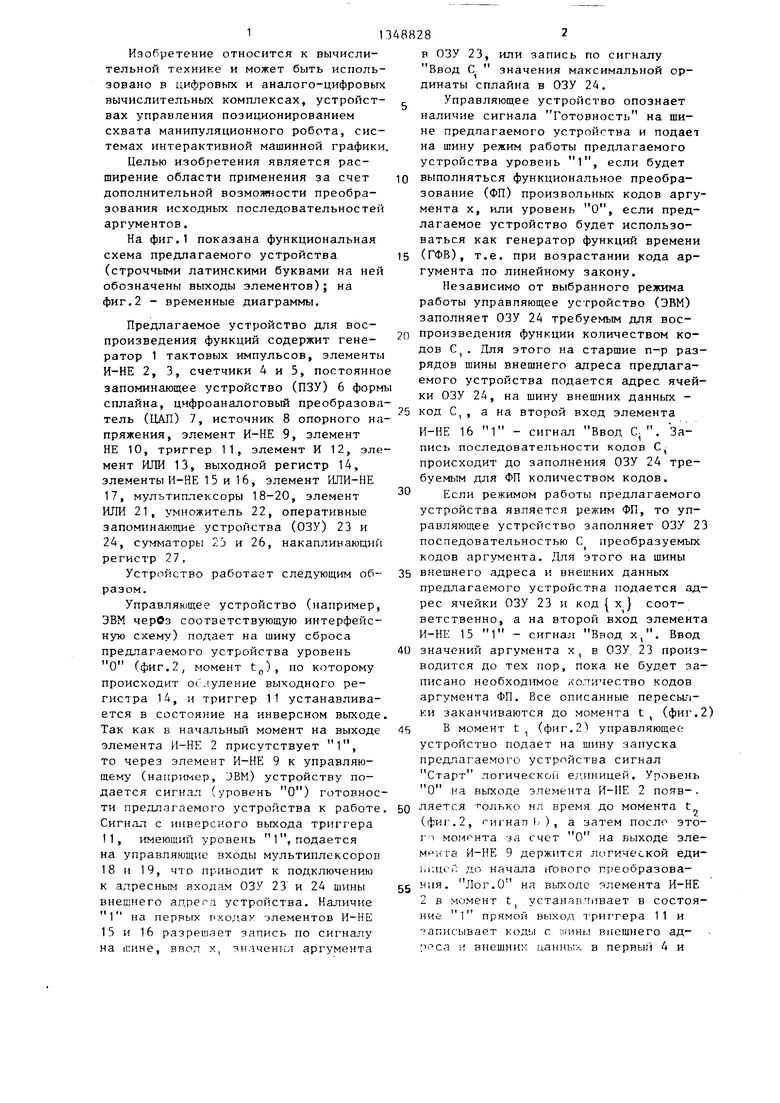

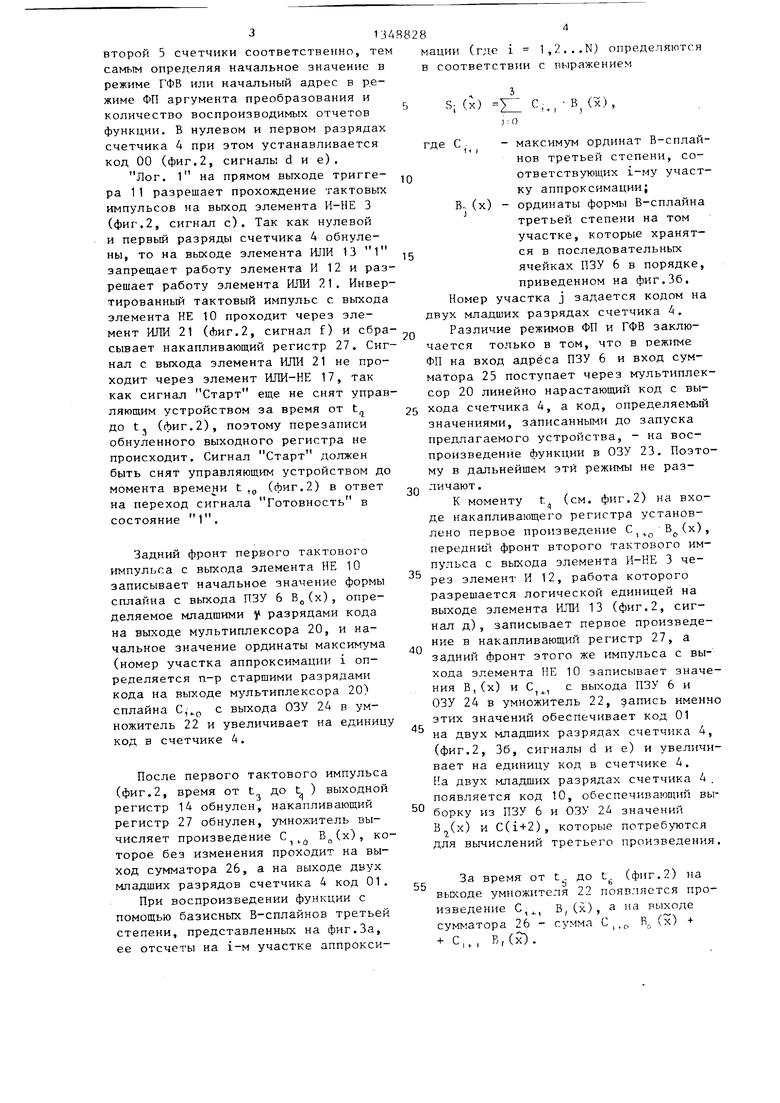

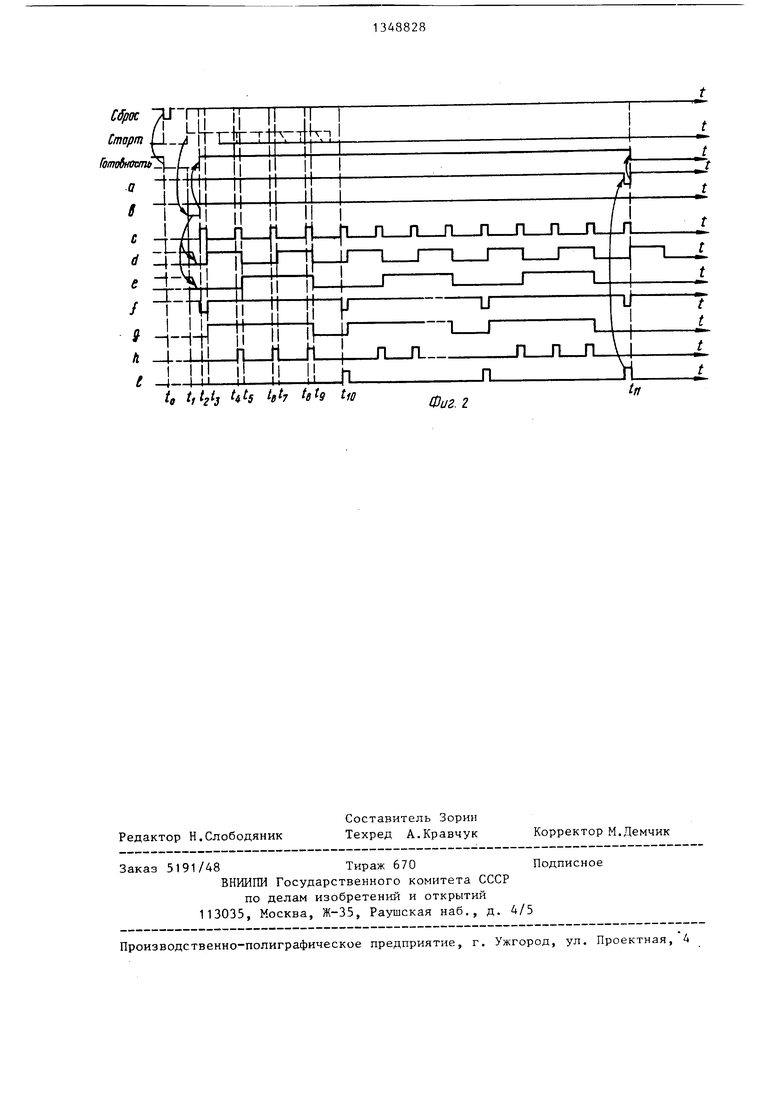

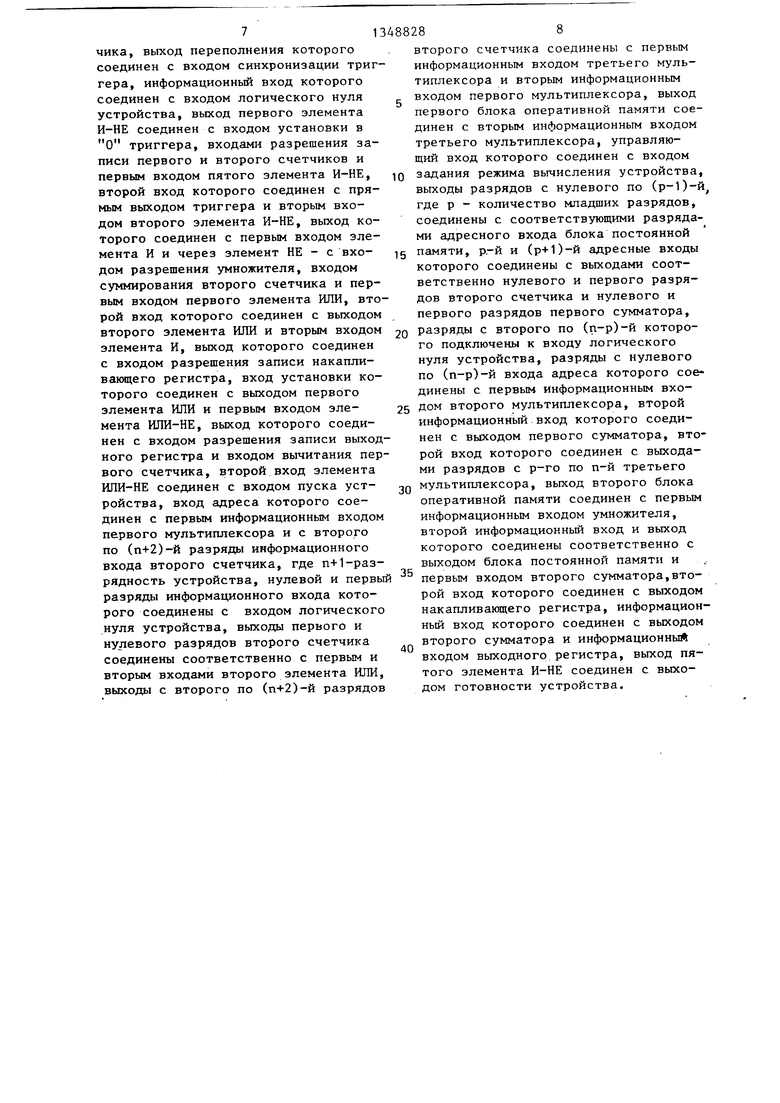

На фиг,1 показана функциональная схема предлагаемого устройства (строчными латинскими буквами на не обозначены выходы элементов); на фиг.2 - временные диаграммы.

Предлагаемое устройство для воспроизведения функций содержит генератор 1 тактовых импульсов, элементы И-НЕ 2, 3, счетчики 4 и 5, постоянное запоминающее устройство (ПЗУ) 6 сплайна, цифроанапоговый преобразователь (ЦАП) 7, источник 8 опорного напряжения, элемент И-НЕ 9, элемент НЕ 10, триггер 11, элемент И 12, элемент ИЛИ 13, выходной регистр 14, элементы И-НЕ 15 и 16, элемент ИЛИ-НЕ 17, мультиплексоры 18-20, элемент ИЛИ 21, умножитель 22, оперативные запоминающие устройства (ОЗУ) 23 и 24, сумматоры 25 и 26, накапливающий регистр 27,

Устройство работает следующим образом.

Управляющее устройство (например, ЭВМ черОз соответствующую интерфейсную схему) подает на шину сброса предлагаемого устройства уровень О (фиг.2, момент tp), по которому происходит об..уление выходного регистра 14, и триггер 11 устанавливается в состояние на инверсном выходе. Так как Б начальньш момент на выходе элемента И-НЕ 2 присутствует 1, то через элемент И-НЕ 9 к управляющему (например, ЭВМ) устройству подается сигнал (уровень О) готовности предлагаемого устройства к работе. Сигнал с инверсного выхода триггера II, имеющий уровень 1, подается на управляющие входы мультиплексоров 18 и 19, что приводит к подключению к адресным входам ОЗУ 23 и 24 щины внешнего адрега устройства. Наличие 1 на первых рходах -элементов И-НЕ 15 и 16 разрен1ает запись по сигналу на 1иине, ввод х, значентгл аргумента

5

0

5

0

5

0

5

0

5

1 - сигнал Ввод С- . ЗаС.

в ОЗУ 23, или запись по сигналу Ввод Ц значения максимальной ординаты сплайна в ОЗУ 24.

Управляющее устройство опознает наличие сигнала Готовность на шине предлагаемого устройства и подает на шину режим работы предлагаемого устройства уровень 1, если будет выполняться функциональное преобразование (ФП) произвольных кодов аргумента X, или уровень О, если предлагаемое устройство будет использоваться как генератор функций времени (ГФВ), т.е. при возрастании кода аргумента по линейному закону.

Независимо от выбранного режима работы управляющее устройство (ЭВМ) заполняет ОЗУ 24 требуемым для воспроизведения функции количеством кодов С . Для этого на старшие п-р разрядов шины внешнего адреса предлагаемого устройства подается адрес ячейки ОЗУ 24, на шину внешних данных - код С,, а на второй вход элемента

И-НЕ 16

пись последовательности кодов происходит до заполнения ОЗУ 24 требуемым для ФП количеством кодов.

Если режимом работы предлагаемого устройства является режим ФП, то управляющее устройство заполняет ОЗУ 23 последовательностью С преобразуемых кодов аргумента. Для этого на шины внешнего адреса и внешних данных предлагаемого устройства подается адрес ячейки ОЗУ 23 и код | х } соответственно, а на второй вход элемента И-НЕ 15 1 - сигнал Ввод х/ . Ввод значений аргумента х в ОЗУ. 23 производится до тех пор, пока не будет записано необходимое количество кодов аргумента ФП. Все описанные пересылки заканчиваются до момента t (фиг.2)

В момент t (фиг.2) управляющее устройство подает на шину запуска предлагаемого устройства сигнал Старт логической е;;иницей. Уровень О на выходе элемента И-НЕ 2 появ-. ляется т олько на время до момента t (фиг.2, сигнал ,), а затем поело это- п момента за счет О на выходе эле- менга И-НЕ 9 держится логической единице/; до начала ifoBoro преобразования. Лог.О на выходе элемента И-НЕ 2 в момент t устанавливает в состояние 1 прямой выход триггера 11 и аг исывает коды с итны внешнего ад- и внешних данных в первый 4 и

второй 5 счетчики соответственно, тем самым определяя начальное значение в режиме ГФВ или начальный адрес в режиме ФП аргумента преобразования и количество воспроизводимых отчетов функции. В нулевом и первом разрядах счетчика 4 при этом устанавливается код 00 (фиг.2, сигналы d и е).

Лог. 1 на прямом выходе триггера 11 разрешает прохождение тактовых импульсов на выход элемента И-НЕ 3 (фиг,2, сигнал с). Так как нулевой и первый разряды счетчика 4 обнулены, то на выходе элемента ИЛИ 13 1 запрещает работу элемента И 12 и разрешает работу элемента ИЛИ 21. Инвертированный тактовый импульс с выхода элемента НЕ 10 проходит через элемент ИЛИ 21 (Лиг.2, сигнал f) и сбрасывает накапливающий регистр 27. Сигнал с выхода элемента ИЛИ 21 не проходит через элемент ИЛИ-НЕ 17, так как сигнал Старт еще не снят управляющим устройством за время от t до tj (фиг.2), поэтому перезаписи обнуленного выходного регистра не происходит. Сигнал Старт должен быть снят управляющим устройством до момента времени t ,(, (фиг.2) в ответ

на переход сигнала Готовность в II II

состояние

Г

Задний фронт первого тактового импульса с выхода элемента НЕ 10 записывает начальное значение формы сплайна с выхода ПЗУ 6 В(х), определяемое младшими у разрядами кода на выходе мультиплексора 20, и начальное значение ординаты максимума (номер участка аппроксимации i определяется п-р старшими разрядами кода на выходе мультиплексора 20) сплайна C,Vo выхода ОЗУ 24 в умножитель 22 и увеличивает на единиц код в счетчике 4.

После первого тактового импульса (фиг.2, время от t до t ) выходной регистр 14 обнулен, накапливающий регистр 27 обнулен, умножитель вычисляет произведение С В(х), которое без изменения проходит на выход сумматора 26, а на выходе двух младших разрядов счетчика 4 код 01.

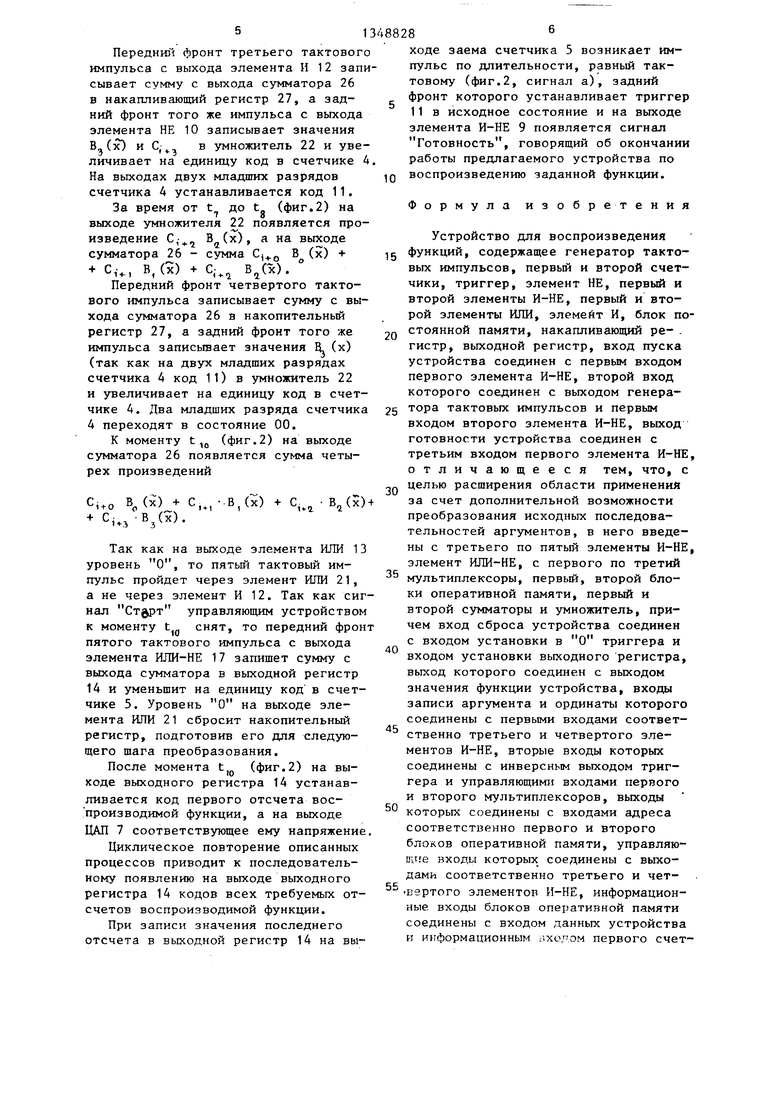

При воспроизведении функции с помощью базисных В-сплайнов третьей степени, представленных на фиг.За, ее отсчеты на i-м участке аппроксинации (где i 1,2...N) определяются в соответствии с выражением

S; (х)

С„,-В/х),

0

5

0

0

5

0

5

0

где С В. (х)

максимум ординат В-сплайнов третьей степени, соответствующих 1-му участку аппроксимации; ординаты формы В-сплайна третьей степени на том участке, которые хранятся в последовательных ячейках ПЗУ 6 в порядке, приведенном на фиг.36. Номер участка j задается кодом на двух младших разрядах счетчика 4.

Различие режимов ФП и ГФВ заключается только в том, что в реж11ме ФП на вход адреса ПЗУ 6 и вход сумматора 25 поступает через мультиплексор 20 линейно нapacтaюш й код с вы- 5 хода счетчика 4, а код, определяемый значениями, записанными до запуска предлагаемого ycTpoficTBa, - на воспроизведение функции в ОЗУ 23. Поэтому в дальнейщем эти режимы не различают .

К моменту t (см. фиг.2) на входе накапливающего регистра установлено первое произведение С В(х), передний фронт второго тактового импульса с выхода элемента И-НЕ 3 через элемент И 12, работа которого разрешается логической единицей на выходе элемента ИЛИ 13 (фиг.2, сигнал д), записывает первое произведение в накапливающий регистр 27, а задний фронт этого же импульса с выхода элемента НЕ 10 записывает значения В, (х) и С, с выхода ПЗУ 6 и ОЗУ 24 в умножитель 22, апись именно этих значений обеспечивает код 01 на двух младщих разрядах счетчика 4, (фиг.2, 36, сигналы d и е) и увеличивает на единицу код в счетчике 4. На двух младших разрядах счетчика 4 появляется код 10, обеспечивающи выборку из ПЗУ 6 и ОЗУ 24 значений В(х) и C(i+2), которые потребуются для вычислений третьего произведения.

За время от t- до t. (фиг.2) на

b

выходе умножителя 22 появляется произведение С,, В,(х), а на выходе сумматора 26 - сумма С, FV (х) + + С., , В, (х).

Переднш фронт третьего тактового импульса с выхода элемента И 12 записывает сумму с выхода сумматора 26 в накапливающий регистр 27, а задний фронт того же импульса с выхода элемента НЕ 10 записывает значения В (х) и С, в умножитель 22 и увеличивает на единицу код в счетчике 4. На выходах двух младших разрядов счетчика А устанавливается код 11,

За время от t. выходе умножителя изведение С,- сумматора 26 - сумма С В(х)

до 22 В(х),

. „ tg (фиг.2) на

появляется про- а на выходе

i-f о о -

. C,v, в, (х) + С;, В,(„, .

Передний фронт четвертого тактового импульса записывает сумму с выхода сумматора 26 в накопительный регистр 27, а задний фронт того же импульса записывает значения S (х)

(так как на двух младших разрядах счетчика 4 код 11) в умножитель 22 и увеличивает на единицу код в счетчике 4. Два младших разряда счетчика 4 переходят в состояние 00.

К моменту t ,д (фиг.2) на выходе сумматора 26 появляется сумма четырех произведений

С;

С,,, -.В/х) + С;,.В(х).

и-о

Так как на выходе элемента ИЛИ 13 уровень О, то пятый тактовый импульс пройдет через элемент ИЛИ 21, а не через элемент И 12. Так как сигнал управляющим устройством к моменту снят, то передний фрон пятого тактового импульса с выхода элемента ИЛИ-НЕ 17 запишет сумму с выхода сумматора в выходной регистр 14 и уменьшит на единицу код в счетчике 5. Уровень О на выходе элемента ИЛИ 21 сбросит накопительный регистр, подготовив его для следующего шага преобразования.

После момента t (фиг.2) на выходе выходного регистра 14 устанавливается код первого отсчета воспроизводимой функции, а на выходе ЦАП 7 соответствующее ему напряжение

Циклическое повторение описанных процессов приводит к последовательному появлению на выходе выходного регистра 14 кодов всех требуемых отсчетов воспроизводимой функции.

При записи значения последнего отсчета в выходной регистр 14 на вы

8828

ходе заема счетчика 5 возникает импульс по длительности, равный тактовому (фиг.2, сигнал а), задний фронт которого устанавливает триггер 11 в исходное состояние и на выходе злемента И-НЕ 9 появляется сигнал Готовность, говорящий об окончании работы предлагаемого устройства по воспроизведению заданной функции.

10

5

0

5

0

5

0

Формула изобретения

Устройство для воспроизведения функций, содержащее генератор тактовых импульсов, первый и второй счетчики, триггер, элемент НЕ, первый и второй элементы И-НЕ, первый и второй элементы ИЛИ, элемейт И, блок постоянной памяти, накапливающий ре- . гистр, выходной регистр, вход пуска устройства соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом генератора тактовых импульсов и первым входом второго элемента И-НЕ, выход готовности устройства соединен с третьим входом первого элемента И-НЕ, отличающееся тем, что, с целью расширения области применения за счет дополнительной возможности преобразования исходных последовательностей аргументов, в него введены с третьего по пятый элементы И-НЕ, элемент ИЛИ-НЕ, с первого по третий мультиплексоры, первый, второй блоки оперативной памяти, первый и второй сумматоры и умножитель, причем вход сброса устройства соединен с входом установки в О триггера и входом установки выходного регистра, выход которого соединен с выходом значения функции устройства, входы записи аргумента и ординаты которого соединены с первыми входами соответственно третьего и четвертого элементов И-НЕ, вторые входы которых соединены с инверсным выходом триггера и управляющими входами первого и второго мультиплексоров, выходы которых соединены с входами адреса соответственно первого и второго блоков оперативной памяти, управляющие входы которых соединены с выходами соответственно третьего и чет- вертого элементов И-НЕ, информационные входы блоков оперативной памяти соединены с входом данных устройства и информационным .мхо/ ом первого счетчика, выход переполнения которого соединен с входом синхронизации триггера, информационный вход которого соединен с входом логического нуля устройства, выход первого элемента И-НЕ соединен с входом установки в О триггера, входами разрешения записи первого и второго счетчиков и первым входом пятого элемента И-НЕ, второй вход которого соединен с прямым выходом триггера и вторым входом второго элемента И-НЕ, выход которого соединен с первым входом элемента И и через элемент НЕ - с входом разрешения умножителя, входом суммирования второго счетчика и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и вторым входом элемента И, выход которого соединен с входом разрешения записи накапливающего регистра, вход установки которого соединен с выходом первого элемента ИЛИ и первым входом элемента ИПИ-НЕ, выход которого соединен с входом разрешения записи выходного регистра и входом вычитания первого счетчика, второй вход элемента ИЛИ-НЕ соединен с входом пуска устройства, вход адреса которого соединен с первым информационным входом первого мультиплексора и с второго по (п+2)-й разряды информационного входа второго счетчика, где п+1-разрядность устройства, нулевой и первы разряды информационного входа которого соединены с входом логического нуля устройства, выходы первого и нулевого разрядов второго счетчика соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы с второго по (п+2)-й разрядов

10

15

20

3488288

второго счетчика соединены с первым информационным входом третьего мультиплексора и вторым информационным входом первого мультиплексора, выход первого блока оперативной памяти соединен с вторым информационным входом третьего мультиплексора, управляющий вход которого соединен с входом задания режима вычисления устройства, выходы разрядов с нулевого по (р-1)-й где р - количество младших разрядов, соединены с соответствующими разрядами адресного входа блока постоянной памяти, р.-й и (р+1)-й адресные входы которого соединены с выходами соответственно нулевого и первого разрядов второго счетчика и нулевого и первого разрядов первого сумматора, разряды с второго по (п-р)-й которого подключены к входу логического нуля устройства, разряды с нулевого по (п-р)-й входа адреса которого сое« динены с первым информационным вхо- 25 дом второго мультиплексора, второй информационный вход которого соединен с выходом первого сумматора, второй вход которого соединен с выходами разрядов с р-го по п-й третьего 2Q мультиплексора, выход второго блока оперативной памяти соединен с первым информационным входом умножителя, второй информационный вход и выход которого соединены соответственно с выходом блока постоянной памяти и первым входом второго сумматора,второй вход которого соединен с выходом накапливающего регистра, информационный вход которого соединен с выходом второго сумматора и информационньА входом выходного регистра, выход пятого элемента И-НЕ соединен с выходом готовности устройства.

35

40

CSpoc XT Г

III Ч Старт / I /|rri r rtf lf| l

Готобноаги :

t 4 -UUиииTL

to titgij l,t tetg tio

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1987 |

|

SU1472901A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Цифровой функциональный генератор | 1985 |

|

SU1282104A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1734102A1 |

| Устройство для воспроизведения функций | 1987 |

|

SU1562929A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых и аналого-цифровых вычислительных комплексах, устройствах управления позиционированием охвата манипуляционного робота, системах интерактивной машинной графики. Целью изобретения является расширение области применения устройства. Устройство содержит генератор тактовых импульсов, первый и второй элементы И-НЕ, первый и второй счетчики, ПЗУ формы сплайна, ЦАП, источник опорного напряжения, пятый элемент И-НЕ, элемент НЕ, триггер (D-типа), элемент И, второй элемент ИЛИ, выходной регистр, третий и четвертый элементы И-НЕ, элемент ИЛИ-НЕ, первый, второй и третий мультиплексоры, первый элемент ИЛИ, умножитель, первое и второе ОЗУ, первьш и второй сумматоры, накапливающий регистр. Благодаря новым связям и новому построению схемы устройство позволяет дополнительно реализовать режим функционального преобразования исходных последовательностей аргументов, обеспечивает представление выходной величины в двоичном коде и дает возможность произвольного выбора начального и конечного значений интервала воспроизведения функции. 2 ил. сл о;) 4 ОО 00 tsD 00

Редактор Н.Слободяник

Составитель Зорин Техред А.Кравчук

Заказ 5191/48Тираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М.Демчик

| Генератор функций | 1982 |

|

SU1057966A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1164745A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-23—Подача