рерывной последовательности импульсов. Преобразователь содержит элементы И 7 11, 12, элемент ИЛИ 20, RS-триггер I, D-триггер 6, счетчик 8 импульсов, регистры 2, 15, сутчма- тор 10, блок 9 сравнения кодов,, формирователь 14 импульсов, блок 17 коррекции. Преобразователь начинает работу по сигналу на шине 3 запуска, по которому начинается подсчет импульсов в счетчике 8, При совпадении кодов в счетчике Вив суммато зе 10 на выходе U-триггера 6 формируются

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах преобразования и кодирования информации а также в качестве узла цифровых функпиональных преобразователей, например синусоидальных.

Целью изобретения является повышение точности в режиме формирования неггрерывной последовательности им- пульсов,

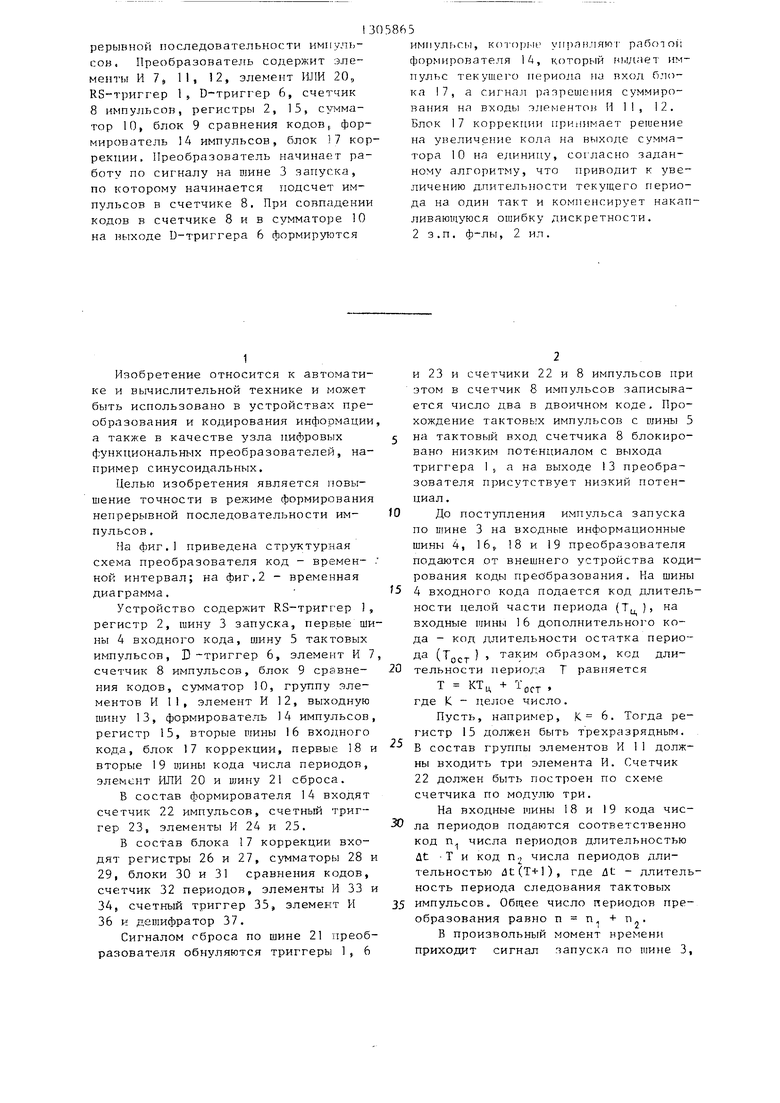

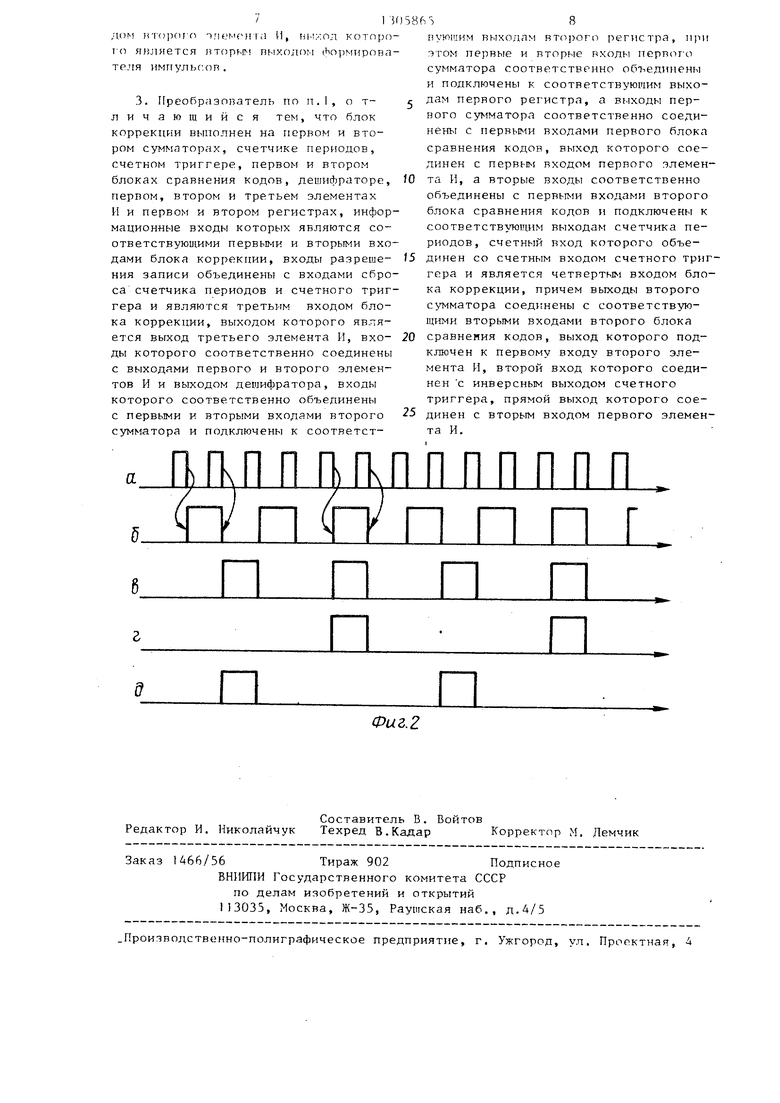

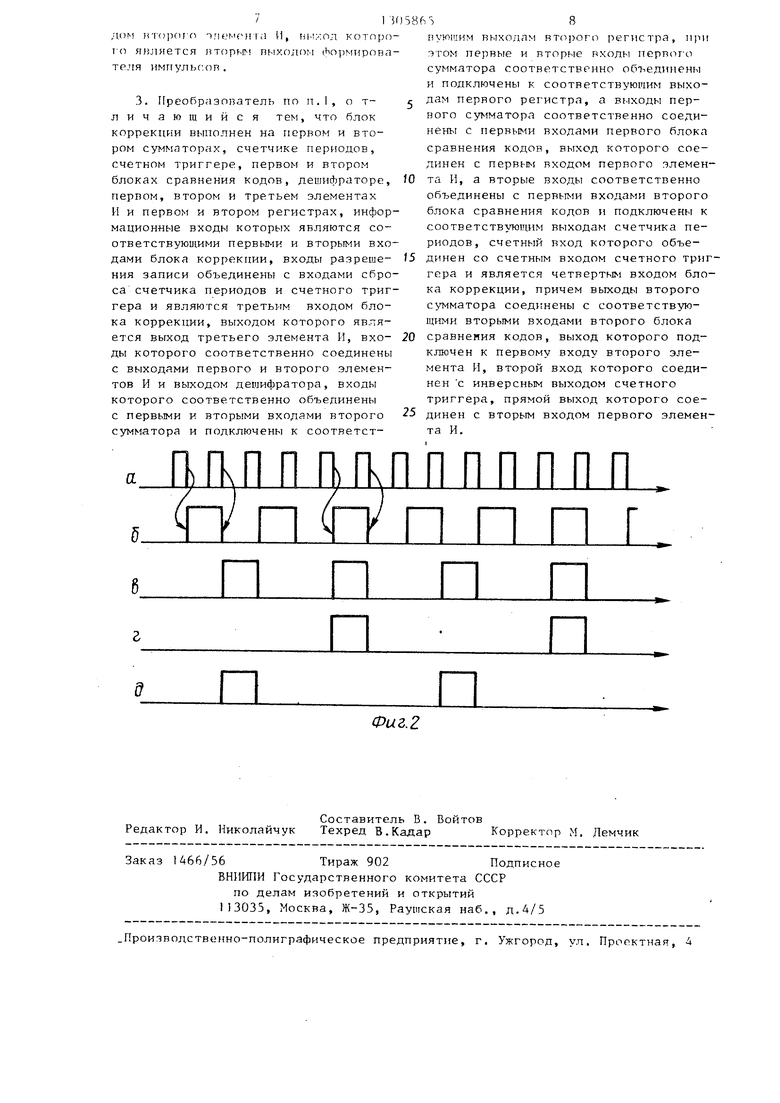

На фиг.1 приведена структурная схема преобразователя код - времен- ной интервал; на фиг,2 - временная диаграмма,

Устройство содержит RS-триггер ), регистр 2, шину 3 запуска, первые шины 4 входного кода, шину 5 тактовых импульсов, D-триггер 6, элемент И 7 счетчик В импульсов, блок 9 ср 9вне- ния кодов, сумматор 10, группу элементов И 11, элемент И 12, выходную шину 13, формирователь 14 импульсов, регистр 15, вторые шины 16 входного кода, блок 17 коррекпии, первые 18 и вторые 19 шины кода числа периодов, элемент 1-ШИ 20 и шину 21 сброса.

Б состав формирователя 14 входят счетчик 22 импульсов, счетный триггер 23, элементы И 24 и 25.

В состав блока 17 коррекции: входят регистры 26 и 27, сумматоры 28 и 29, блоки 30 и 31 срав 1ения кодов, счетчик 32 периодов, элементы И 33 и 34, счетный триггер 35, элемент И 36 и дешифратор 37.

Сигналом сброса по шине 21 преобразователя обнуляются триггеры 1, 6

импульс., KOTopi-u упранляюг работой: формирователя 14, который г ыдает импульс текущего периода на вход блока 17, а сигнал разрешения суммирования на входы элементов И 11, 12. Блок 17 коррекпии принимает решение на увеличение кола на выходе сумматора 10 на единицу, согласно заданному алгоритму, что приводит к увеличению длительности текущего периода на один такт и компенсирует накапливающуюся ошибку дискретности, 2 3.п, ф-лы, 2 ил.

и 23 и счетчики 22 и 8 импульсов при этом в счетчик 8 импульсов записывается число два в двоичном коде. Прохождение тактовь х импульсов с шины 5 на тактовый вход счетчика В блокировано низким потенциалом с выхода триггера 1, а на выходе 13 преобразователя присутствует низкий потен- пиал.

До поступления импульса запуска по шине 3 на входные информационные шины 4, 16„ 18 и 19 преобразователя подаются от внешнего устройства кодирования коды преобразования. На шины 4 входного кода подается код длительности целой части периода (Тц), на входные шины 16 дополнительного кода - код длительности остатка периода (TOC ) , таким образом, код длительности периода Т равняется

Т КТ + i ocT . где К - целое число.

Пусть, например, К 6. Тогда регистр 15 должен быть трехразрядным. В состав группы элементов И 11 должны входить три элемента И. Счетчик 22 должен быть построен по схеме счетчика по модулю три.

На входные шины 18 и 19 кода числа периодов подаются соответственно код п числа периодов длительностью At -Т и код П2 числа периодов длительностью 4С(Тн-1), где ЛС - длительность периода следования тактовых импульсов. Общее число периодов преобразования равно п п, + п .

В произвольный момент времени приходит сигнал запуска по шине 3,

при этом информация с входных тин 4, 16, 18 и 19 записывается в соответствующие регистры 2, 15, 26 и 27, счетчик 32 периодов и счетный триггер 35 обнуляются, а на выходе RS- триггера 1 устанавливается высокий потенциал, который снимает запрет на прохождение тактовых импульсов на тактовьп вход счетчика 8 импульсов, который начинает считать тактовые импульсы.

. В момент равенства текущего кода счетчика 8 импульсов и кода сумматора 10, на выходе которого присутствует код Тц(вторая группа кодов и вход сумматора 10 блокированы низким потенциалом с выхода формирователя 14), на выходе блока 9 сравнения появляется высокий потенциал, который поступает на информационньм вход D- триггера 6, выполняющего функцию защиты от помех. Задержка заднего фронта импульса на выходе В-триггера 6

Решение на увеличение длительности периода принимает блок 17 коррекотносительно момента сравнения кодов

счетчика 8 импульсов и сумматора 10- 25 ции, который работает следующим обравна двум периодам тактовой частоты, разом.

но так как в исходном состоянии в В регистрах 26 и 27 хранится код

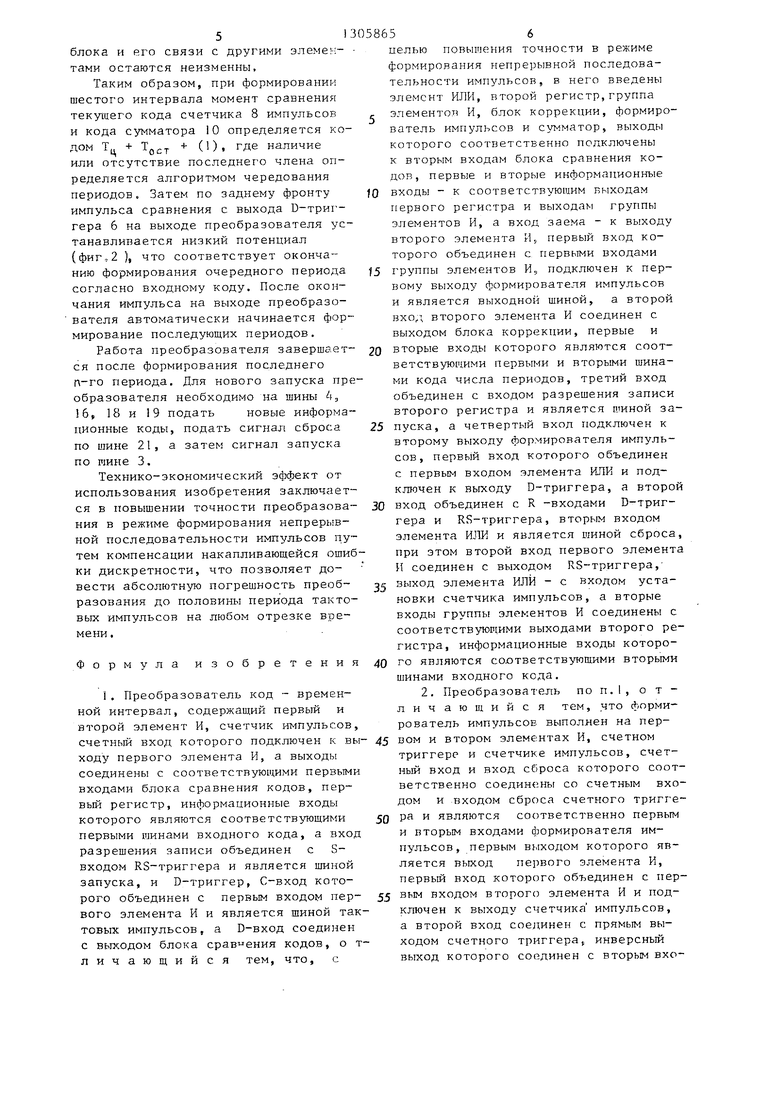

счетчик 8 импульсов записано число числа периодов П, и П соответствендва, то временной интервал между но. Первое условие алгоритма реализуфронтами импульсов на выходе D-триг-зо ется с помощью дешифратора 37. Втогера 6 соответствует коду Гц . Импульсы с выхода D-триггера 6 поступают на первый вход формирователя 14, временная диаграмма работы которого приведена на фиг.2, где а - импульсы на выходе D-триггера 6; S- импульсы на выходе счетного триггера 23; б - импульсы на выходе счетчика 22 по модулю три; 1- импульсы на первом вы35

рое и третье условия реализуются с помощью сумматоров 28 и 29, счетчика 32 периодов, счетного триггера 35, блоков 30 и 31 сравнения кодов, элементов И 33, 34 и 36. На сумматорах 28 и 29 производится умножение кодов П и п на два. Счетчик 32 периодов

выполняет номер текугцего периода. Счетный триггер 35 определяет чет- ходе формирователя 14; $- импульсы 40 ность текущего периода. На блоках . на втором выходе формирователя 14. 30 и 31 сравнения производится сравнение номера текущего периода с коИмпульс с выхода D-триггера 6 через элемент ИЛИ 20 обнудяет счетчик В импульсов (с записью кода два) и счетчик 8 начинает формировать новый интор ;ал времени, соответствуюдом удвоенного числа периодов п, и

П, согласно первым частям второго 45 и третьего условий. Логическое умножение правых и левых частей второго щий коду Тц . Работа схемы повторяется и третьего условий производится на без изменений, пока при формировании первом и втором элементах И 33 и 34 щестого интервала времени на перво) соответственно, выходы которых и вы- выходе формирователя 14, а следова- 50 Д дещифратора 37 объединены по ИЛИ тельно, и на выходной шине 13 не по- на третьем элементе И 36, Таким образом, информация на выходе блока 17 коррекции изменяется по заднему фронту импульса с второго выхода форми- 55 рователя 14 (фиг.2). Нри изменении алгоритма чередования периодов длительностью (31 Т ДЬ (Т + 1) возможны изменения в структуре блока 17 коррекции, но при этом функции

явится высокий потенциал (фиг.2) и не разблокирует поступления информации на вторую группу входов и вход заема сумматора 10.

К моменту поступления на второй вход первого элемента И 12 высокого потенциала с выхода формирователя 14, на его первый вход уже подана ин

формация, характеризующая увеличение длительности периода на один такт (4t). При увеличении длительности текущего перргода на один такт на первом входе первого элемента И 12 присутствует высокий потенциал. Чередование периодов с длительностями (jt-Т ид1(Т+1) на выходе преобразователя определяется алгоритмом

t . Т,если 1 ) П2 О

At

2)(2п,7П) А (п 2К+1)

3)(2пг.с п) Л(п 2К) (Т+1) - в противном случае;

где Т - длительность текущего периода;

номер текущего периода; К - натуральный ряд чисел (К

0,1,2,...).

Решение на увеличение длительности периода принимает блок 17 коррек

рое и третье условия реализуются с помощью сумматоров 28 и 29, счетчика 32 периодов, счетного триггера 35, блоков 30 и 31 сравнения кодов, элементов И 33, 34 и 36. На сумматорах 28 и 29 производится умножение кодов П и п на два. Счетчик 32 периодов

дом удвоенного числа периодов п, и

блока и его связи с другими элемек- тами остаются неизменны.

Таким образом, при формировании шестого интервала момент сравнения текущего кода счетчика 8 импульсов и кода сумматора 10 определяется кодом Тц + TQ + (1), где наличие или отсутствие последнего члена определяется алгоритмом чередования периодов. Затем по заднему фронту импульса сравнения с выхода В-триг - гера 6 на выходе преобразователя устанавливается низкий потенциал (фиг,2 ), что соответствует окончанию формирования очередного периода согласно входному коду. После окончания импульса на выходе преобразователя автоматически начинается формирование последующих периодов.

Работа преобразователя завершается после формирования последнего п-го периода. Для нового запуска преобразователя необходимо на шины 4, 6, 18 и 19 подать новые информационные коды, подать сигнал сброса по шине 21, а затем сигнал запуска по шине 3.

Технико-экономический эффект от использования изобретения заключается в повышении точности преобразования в режиме формирования непрерывной последовательности импульсов путем компенсации накапливающейся ошибки дискретности, что позволяет довести абсолютную погрешность преобразования до половины периода тактовых импульсов на любом отрезке времени .

ормула изобретения 40

,

1 . преобразователь код - временной интервал, содержащий первый и второй элемент И, счетчик импульсов, счетный вход которого подключен к выходу первого элемента И, а выходы соединены с соответствующими первыми входами блока сравнения кодов, первый регистр, информационные входы которого являются соответствующими первыми шинами входного кода, а вход разрешения записи объединен с S- входом RS-триггера и является шиной запуска, и D-триггер, С-вход которого объединен с первым входом первого элемента И и является шиной тактовых импульсов, а D-вход соединен с выходом блока сравнения кодов, о т личающийся тем, что, с

ш

15

40

20

25

058656

целью повышения точности в режиме формирования непрерывной последовательности импульсов, в него введены элемент ИЛИ, второй регистр,группа , элементов И, блок коррекции, формирователь импульсов и сумматор, выходы которого соответственно подключены к вторым входам блока сравнения кодов, первые и вторые информационные входы - к соответствующим выходам первого регистра и выходам группы элементов И, а вход заема - к выходу второго элемента И,, первый вход которого объединен с первыми входами группы элементов И,, подключен к первому выходу формирователя импульсов и является выходной шиной, а второй вхо,1, второго элемента И соединен с выходом блока коррекции, первые и вторые входы которого являются соответствующими первыми и вторыми шинами кода числа периодов, третий вход объединен с входом разрешения записи второго регистра и является шиной запуска, а четвертый вход подключен к второму выходу формирователя импульсов, первый вход которого объединен с первым входом элемента ИЛИ и подключен к выходу D-триггера, а второй вход объединен с R -входами D-триггера и RS-триггера, вторым входом элемента ИЛИ и является шиной сброса, при этом второй вход первого элемента И соединен с выходом RS-триггера, выход элемента ИЛИ - с входом установки счетчика импульсов, а вторые входы группы элементов И соединены с соответствуюр(ими выходами второго регистра, информационные входы которого являются соответствующими вторыми шинами входного кода.

2. Преобразователь по п.1, отличающийся тем, что формирователь импульсов выполнен на первом и втором элементах И, счетном триггере и счетчике импульсов, счетный вход и вход сброса которого соответственно соединены со счетным входом и входом сброса счетного триггера и являются соответственно первым и вторым входами формирователя импульсов, первым выходом которого является выходт; первого элемента И, первый вход которого объединен с первым входом второго элемента И и подключен к выходу счетчика импульсов, а второй вход соединен с прямым выходом счетного триггера, инверсный выход которого соединен с вторым вхо30

35

45

50

55

дом irroiKU f) 1.мем(мгга И, котпро- 141 5П Ляется liTopMM пыходг)м (Ьормнрова- теля импульс .оп .

3. Преобразователь по п.1, о т- ли чающийся тем, что блок коррекции выполнен на первом и втором сумматорах, счетчике периодов, счетном триггере, первом и втором блоках сравнения кодов, дешифраторе, первом, втором и третьем элементах И и первом и втором регистрах, информационные входы которых являются соответствующими первыми и вторыми вхо дами блока коррекции, входы разреше ния записи объединены с входами сброса счетчика периодов и счетного триг гера и являются третьим входом блока коррекции, выходом которого является выход третьего элемента И, входы которого соответственно соединены с выходами цервого и второго элементов И и выходом дешифратора, входы которого соответственно объединены с первыми и вторыми входами второго сумматора и подключены к соответст-

вующим выходам второго регистра, Hjni этом первые и вторые входы первогчт сумматора соответственно объединены и подключены к соответствующим выхо- г дам первого регистра, а выходы первого сумматора соответственно соединены с первыми входами первого блока сравнения кодов, выход которого соединен с первьп- входом первого злеменfO та И, а вторые входы соответственно объединены с первыми входами второго блока сравнения кодов и подключены к соответствующим выходам счетчика периодов, счетный вход которого объе- 15 динен со счетным входом счетного триггера и является четвертым входом блока коррекции, причем выходы второго сумматора соединены с соответствующими вторыми входами второго блока

20 сравнения кодов, выход которого подключен к первому входу второго элемента И, второй вход которого соединен с инверсным выходом счетного триггера, прямой выход которого сое25 динен с вторым входом первого элемента И.

а

ПП Г1ПчПППП ПП П

.

н

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Способ селективной записи импульсных процессов и устройство для его осуществления | 1988 |

|

SU1636800A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1986 |

|

SU1372620A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| Устройство для определения максимального значения | 1990 |

|

SU1815656A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах преобразования и кодирования информации. Цель изобретения - повышение точности в режиме формирования непГЗ (С (Л со о ел 00 Oi ел

Составитель В. Войтов Редактор И. Николайчук Техред В.Кадар Корректор м, Демчик

Заказ 1466/56Тираж 902Подписное

ВНИИ1ТИ Государственного комитета СССР

по делам изобретений и открытий 1)3035, Москва, Ж-35, Раушская наб., д.А/5

.Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Фиг.2

| Преобразователь двоичного кода во временной интервал | 1983 |

|

SU1115223A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1115225A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-23—Публикация

1985-12-30—Подача