тель в код СОК содержит аналого-цифровые преобразователи 1.1-l.n по модулю, где п - число оснований кода СОК, сумматоры 2.1-2.П по модулю, шифраторы 3. 1-З.П-1, блоки 4. 1-4.П-1 коррекции, счетчики 5.1 и 5.2 по модулю и блок 6 управления. Каждый блок

4; коррекции содержит элемент II; сравнения кодов, элемент И 12 и регистр 13. Максимально корректируемая ошибка в устройстве определяется как К;()/2 и не зависит от соотношения оснований р. (i l-n-l) и р„ . 2 3.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1986 |

|

SU1368989A1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1325697A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения датчиков аналоговой информации с вычислительными устройствами, функционирующими в коде системы остаточных классов JCOK), Цель изобретения - повышение достоверности преобразования. Аналого-цифровой преобразова

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сопряжения датчиков аналоговой информации с вычислительными устройствами, функцио- нирующими в коде системы остаточных классов (сок), а также для преобразования мгновенного значения аналогового сигнала в код СОК.

Цель изобретения - повышение до- стоверности преобразования.

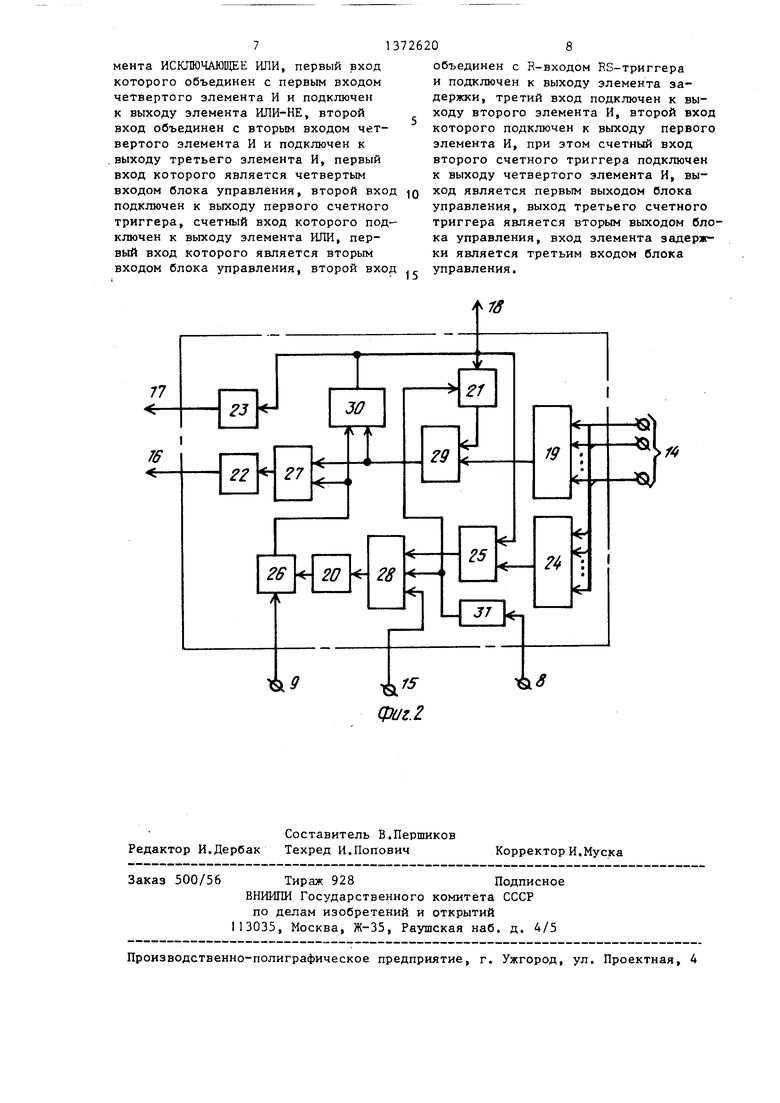

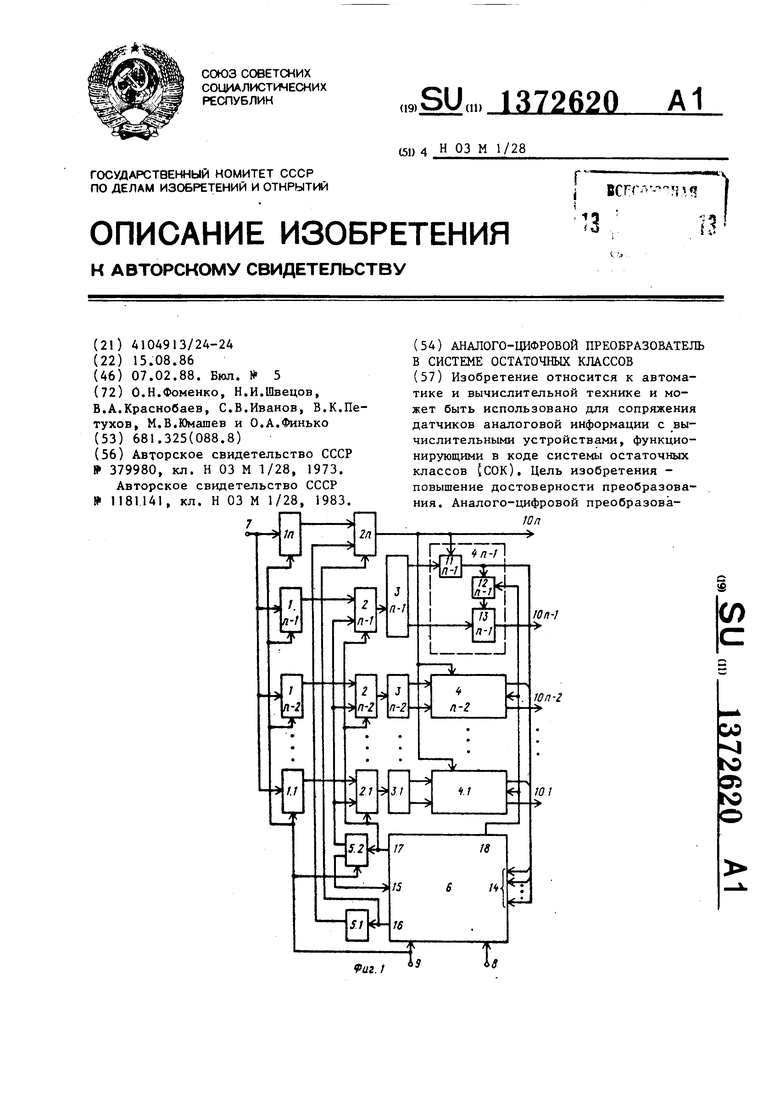

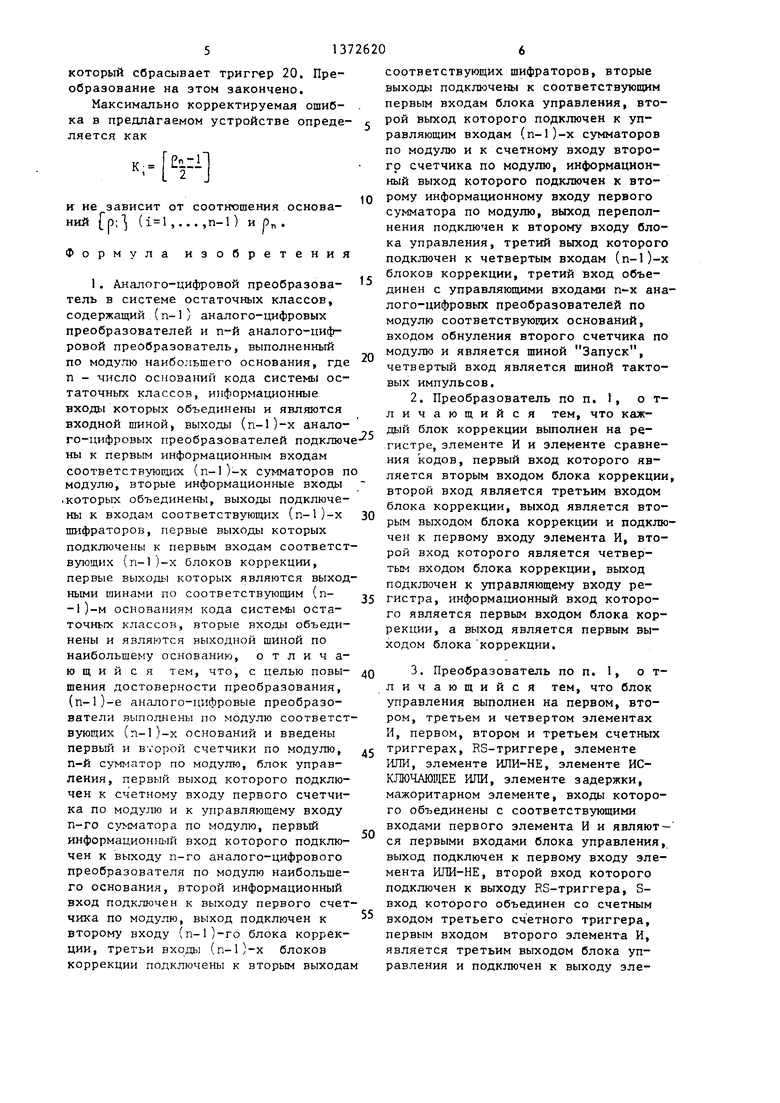

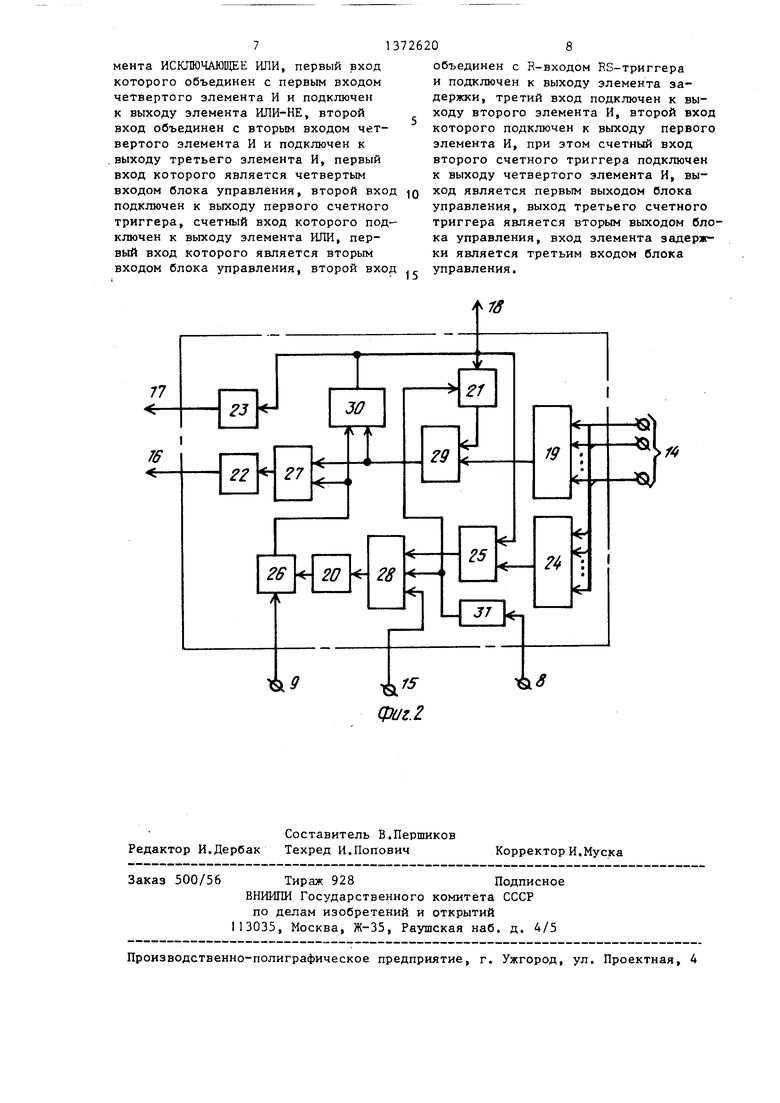

На фиг. 1 приведена функциональная схема аналого-цифрового преобразователя в код СОК; на фиг. 2 - функциональная схема блока управле- ния.

Аналого-цифровой преобразователь в код СОК содержит аналого-цифровые преобразователи 1.1-l.n по модулю, где п - число оснований кода СОК, сумматоры 2.1-2.П по модулю, шифраторы 3.1-З.П-1, блоки 4.1-4.П-1 коррекции, первый 5.1 и второй 5.2 счетчики по модулю, блок 6 управления, входную шину 7, шину 8 Запуск, ши- ну 9 тактовых импульсов и выходные шины 10.1-10.п. Каждый блок 4.1 коррекции содержит элемент ll.i сравнения кодов, элемент И 12, и регистр 13. Блок 6 управления имеет первые 14 и второй 15 входы, первый 16, второй 17 и третий 18 выходы. При этом 1блок 6 выполнен (фиг. 2) на мажоритарном элементе 19, первом счетном триггере 20, ЕБ-триггере 21, втором 22 и третьем 23 счетных триггерах, элементах И 24-27 (с первого по четвертый), элементе ИЛИ 28, элементе ШШ-НЕ 29, элементе ИСКЛЮЧАЮ1ЧЕЕ ИЛИ 30 и элементе 31 задержки.

Аналого-цифровой преобразователь в код СОК работает следующим образом.

В коде СОК цифровой эквивалент преобразуемой аналоговой величины представляется остатками oi, , Ы,..., по взаимно простым основаниям р, , 0; ,. .. , р. в то же время цифровой эквивалент можно представить остатка- Р Рг РП-| по составным основаниям р, ,р, рг,р„, ....Ph-ipn. Тогда для каждого из остатков t О (,...,п-1) можно получить информационный остаток

iHpilp;(1)

и контрольный остаток

n-lfb;lp. (2)

Для определения верности преобразования сравнивают foi. J, ( ,п-1) Cdip . Если ошибок нет, то

--0. , (,П-1)h)

если ошибки есть, то для соответствующих номеров оснований

oin , (,n-l). (4)

Неправильные остатки из f3; х (,n-l) корректируются, если ошибка К; удовлетворяет условию .

0 5

30

K,.-V

Неравенство (4) выполняется, если дляо ft ИТ) выполняется К,рп-1.

Однако неправильным может быть и остаток (Чт. Считают, что остаток oi, получен неправильно, если большин- ство остатков fу (,n-l) (т.е. более п/2) не совпадают с -:«. Тог- ца корректируют остаток ы. до прлу- чения меньшинства остатков ,, « (,n-l)(т.е. менее п/2), не совпадаюиих с oi,

, после чего корректируют неправильные остатки П Л (1 1,

г-1 I

Т).

А1Ш 1.1-1,п преобразуют входную величину А в коды остатков, . pn--,« n.

Сумматоры 2.1-2.П по модулям

соответстостатков . (,n-l) путем проверки выполнения условия (З) или (4).

Если в АЦП 1.п происходит ошибка (т.е. большинство потенциалов на выходах схем ll.l-ll.n-l сравнения соответствуют нулю), то потенциал на выходе мажоритарного элемента 19 соответствует нулю, а на выходе элеменР,-рп ,ргрп.---.рп-,Рп Р .

венно корректируют рстатки /.,/3, 10 ИЛИ-НЕ 29 - единице, поэтому такРП.,,(„. Первый и второй вход каждо-, го сумматора являются информационными, а управляющий служит для управления режимом работы сумматора (сложение или вычитание).

Шифраторы 3. 1-З.П-1 преобразуют остатки р,- (,п-1) информацион- ные остатки (,n-l) по первому выходу и в контрольные остатки (,n-l) по второму выходу соответственно.

Блоки 4.1-4.П-1 коррекции предназначены для выделения правильного результата преобразования его записи и хранения.

Счетчики 5,1 и 5.2 по модулю

15

20

25

товый импульс с выхода элемента И 27 поступает на счетный вход триггера 22 и изменяет его состояние. Таким образом, на счетный вход счетчика 5.1 поступают импульсы частоты до тех пор, пока содержимое счетчика 5.1 и режим работы сумматора 2.п соответствуют величине и знаку ошибки в АДП 1.П, т.е. когда на выходе мажоритарного элемента 19 потенциал соответствует единице, а таким образом, на выходе элемента ИЛИ-НЕ 29 - нулю. Теперь тактовый импульс появляется на выходе элемента ИС- КПЮЧАВЩЕЕ ШШ 30, который поступает на вторые входы элементов И 12.1- 12.пт1 и тем самым позволяет занести в регистры 13,1-13.п-1, номера которых соответствуют номерам АЦП 1.1-1.П-1, в которых нет ошибки правильные результаты преобразования и устанавливает триггер 21 в единичное состояние с целью исключить дальнейшее влияние на работу устройства сигналов на выходе мажоритарного элемента 19. При этом, если во всех АЦП 1.1-1.П-1 ошибок нет, то на выходе элемента И 24 потенциал соответствует единице, что позволяет тактовому импульсу, появившемуся на выхо- 40 де элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 сбросить триггер 20. Преобразование на этом считается законченным.

+1 предназначены для выработки

корректирующей величины для п-го и l-(n-l)-x каналов соответственно. В исходном состоянии в регистры 13 блоков 4.1-4.П-1 коррекции занесены значения остатков (tj ) (,n-l) предыдущего отсчета преобразования. Содержимое счетчика 5.1 соответствует величине ошибки в, АЦП 1.П в предыдущем отсчете преобразования. Содержимое счетчика 5.2 произвольно. Триггер 20 блока управления обнулен, а состояние триггеров 21-23 безразлично. Тактовые импульсы с частотой Г„ по шине 9 поступают на первый вход И 26.

элемента

tj-.

начала пре-

В момент времени

образования по шине 8 поступает импульс запуска, который запускает АЦП 1.1-1.П, сбрасывает содержимое счетчика 5.2 и через время задержки элементом 31, определяемое временем преобразования АЦП 1.1-l.n, устанавливает триггер 20 в единичное, а триггер 21 в нулевое состояния. Тактовые импульсы с частотой Г-гц с выхода элемента И 26 поступают на первые входы элементов И 27 и ИСКЛЮЧАЮЩЕЕ ИЛИ 30. В то же время схемы 11,1-11.п-1 сравнения определяют верность получения информационных

остатков . (,n-l) путем проверки выполнения условия (З) или (4).

Если в АЦП 1.п происходит ошибка (т.е. большинство потенциалов на выходах схем ll.l-ll.n-l сравнения соответствуют нулю), то потенциал на выходе мажоритарного элемента 19 соответствует нулю, а на выходе элемен ИЛИ-НЕ 29 - единице, поэтому так

товый импульс с выхода элемента И 27 поступает на счетный вход триггера 22 и изменяет его состояние. Таким образом, на счетный вход счетчика 5.1 поступают импульсы частоты до тех пор, пока содержимое счетчика 5.1 и режим работы сумматора 2.п соответствуют величине и знаку ошибки в АДП 1.П, т.е. когда на выходе мажоритарного элемента 19 потенциал соответствует единице, а таким образом, на выходе элемента ИЛИ-НЕ 29 - нулю. Теперь тактовый импульс появляется на выходе элемента ИС- КПЮЧАВЩЕЕ ШШ 30, который поступает на вторые входы элементов И 12.1- 12.пт1 и тем самым позволяет занести в регистры 13,1-13.п-1, номера которых соответствуют номерам АЦП 1.1-1.П-1, в которых нет ошибки правильные результаты преобразования и устанавливает триггер 21 в единичное состояние с целью исключить дальнейшее влияние на работу устройства сигналов на выходе мажоритарного элемента 19. При этом, если во всех АЦП 1.1-1.П-1 ошибок нет, то на выходе элемента И 24 потенциал соответствует единице, что позволяет тактовому импульсу, появившемуся на выхо- де элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 сбросить триггер 20. Преобразование на этом считается законченным.

Если хотя бы в одном из АЦП 1.1- 1.П-1 происходит ошибка у то по мере поступления тактовых импульсов на счетный вход триггера 23 с частотой /2 увеличивается содержимое счетчика 5.2 и с частотой f изменяется режим работы сумматоров 2.1-2.П-1. По мере коррекции АЦП 1.1-l.n-l, в которых происходят ошибки, по сигналам соответствующих схем ll.l-ll.n-l сравнения в соответствующие регистры 13.l-13.n-l самостоятельно заносятся правильные результаты преобразования. Когда наступает переполнение счетчика 5.2, на его втором .выходе вырабатывается единичный импульс,

который сбрасывает триггер 20. Преобразование на этом закончено.

Максимально корректируемая ошиб- ка в предлагаемом устройстве опреде-

ляется как

г

.:

и не зависит от соотношения оснований fp; ( ,... ,п-1) и РП .

Формула изобретения

соответству1ощих (n-l)-x сумматоров п модулю, вторые информационные входы .которых объединены, выходы подключены к входам соответствующих (n-l)-x шифраторов, первые выходы которых подключены к первым входам соответствующих (п-1)-х блоков коррекции, первые выходы которых являются выходными шинами по соответствующим (п- -1)-м основаниям кода системы остаточных классов, вторые входы объединены и являются выходной шиной по наибольшему основанию, отличающийся тем, что, с целью повышения достоверности преобразования, (n-l)-e аналого-цифровые преобразователи выполнены по модулю соответствующих (n-l)-x оснований и введены первый и второй счетчики по модулю, п-й сумматор по модулю, блок управления, первый выход которого подключен к счетному входу первого счетчика по модулю и к управляющему входу п-го сумматора по модулю, первый информационный вход которого подключен к выходу п-го аналого-цифрового преобразователя по модулю наибольшего основания, второй информационный вход подключен к выходу первого счет

чика по модулю, выход подключен к второму входу (n-l)-ro блока коррекции, третьи входы (n-l)-x блоков коррекции подключены к вторым выхода

с

0

5

0

0

соответствующих шифраторов, вторые выходы подключены к соответствующим первым входам блока управления, второй выход которого подключен к управляющим входам (n-l)-x сумматоров по модулю и к счетному входу второго счетчика по модулю, информационный выход которого подключен к второму информационному входу первого сумматора по модулю, выход переполнения подключен к второму входу блока управления, третий выход которого подключен к четвертым входам (n-l)-x блоков коррекции, третий вход объединен с управляющими входами п-х аналого-цифровых преобразователей по модулю соответствующих оснований, входом обнуления второго счетчика по модулю и является шиной Запуск, четвертый вход является шиной тактовых импульсов.

мента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого объединен с первым входом четвертого элемента И и подключен к выходу элемента ИЛИ-НЕ, второй вход объединен с вторым входом четвертого элемента И и подключен к .выходу третьего элемента И, первый вход которого является четвертым входом блока управления, второй вход подключен к выходу первого счетного триггера, счетный вход которого подключен к выходу элемента ИЛИ, первый вход которого является вторым

ходом блока управления, второй вход . управления 1J

объединен и подключе держки, тр ходу второ которого п элемента И второго сч к выходу ч ход являет управления триггера я ка управле ки являетс

управления

объединен с R-входом RS-триггера и подключен к выходу элемента задержки, третий вход подключен к выходу второго элемента И, второй вход которого подключен к выходу первого элемента И, при этом счетный вход второго счетного триггера подключен к выходу четвертого элемента И, выход является первым выходом блока управления, выход третьего счетного триггера является вторым выходом блока управления, вход элемента задержки является третьим входом блока

фиг.г

| ПРЕОБРАЗОВАТЕЛЬ «НАПРЯЖЕНИЕ — КОД» В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 0 |

|

SU379980A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1983 |

|

SU1181141A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-07—Публикация

1986-08-15—Подача