1130

Изобретение относится к импульсной технике и может быть использовано при передаче по общему импульсному каналу связи аналоговой информации от нескольких абонентов.

Цель изобретения - повышение помехозащищенности путем уменьшения искажений входных сигналов за счет обеспечения и возможности их расфа- зировки и повьш1ение надежности рабо- ты устройства.

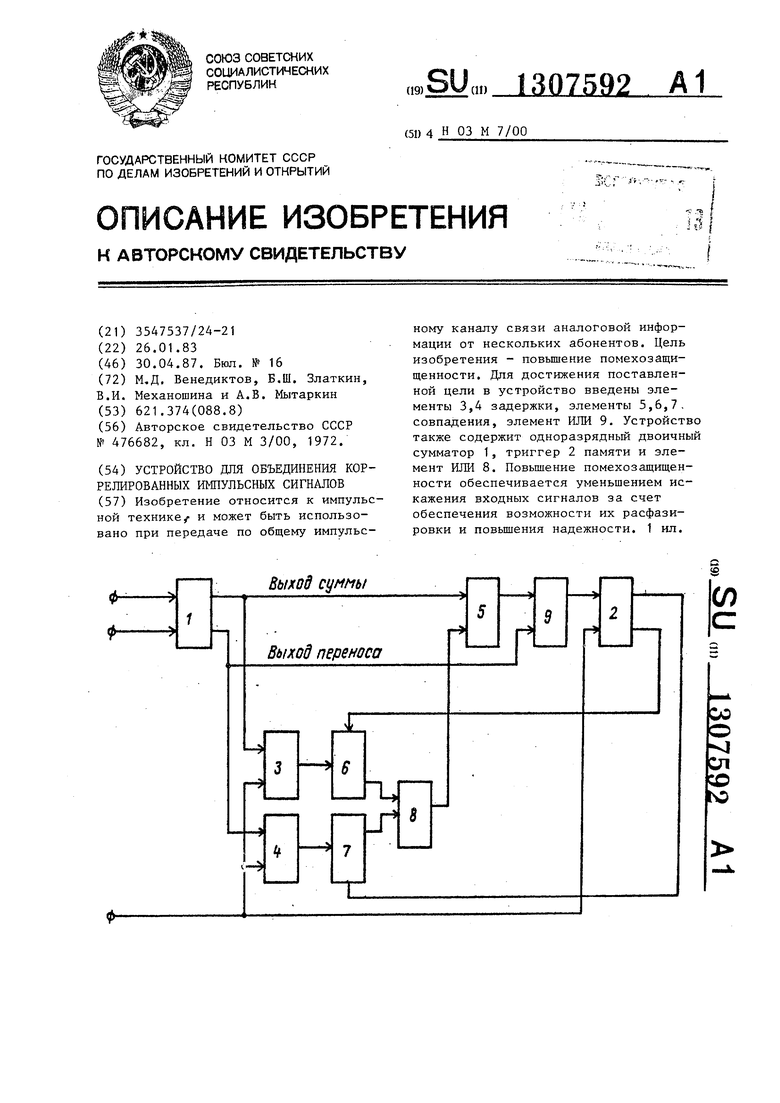

На чертеже представлена функциональная схема устройства для объединения коррелированных импульсных сигналов.

Устройство для объединения коррелированных импульсных сигналов содержит одноразрядный двоичный-сумматор 1 и триггер 2 памяти. Выход суммы одноразрядного двоичного сумматора 1 соединен с входом элемента 3 задержки, а выход переноса подключен к входу элемента 4 задержки. Кроме то

го, выход суммы одноразрядного двоич

ного сумматора 1 подключен к одному из входов элемента 5 совпадения.

Выход элемента 3 задержки и инверсный выход триггера 2 памяти подключены к входам элемента 6 совпаде. „

ния, а выход 4 и прямой выход триггера 2 памяти подключены к входам элемента 7 совпадения. Выходы элементов 6 и 7 совпадения через элемент ИЛИ 8 подключены к второму входу элемента 5 совпадения, выход кото- рого и выход переноса одноразрядного двоичного сумматора 1 подключены к информационному входу триггера 2 памяти через элемент ИЛИ 9.

Устройство работает следующим об- разом.

При совпадении символов в объединяемых сигналах на выходе переноса одноразрядного двоичного сумматора 1 возникает импульс. Этот импульс про- ходит через элемент ИЛИ 9 на инфор- мационньй вход триггера 2 памяти и независимо от состояния триггера 2 памяти в предьщущий момент времени устанавливает его в единичное состоя- ние.

Таким образом, если в объединяемых сигналах в данном такте имеется одновременно символ 1, то на выходе . устройства формируется символ 1.

При совпадении символов О в объединяемых сигналах на выходах суммы и переноса одноразрядного двоичного

5

0

5

30

J5 40

45 50

.55

сумматора импульсы не образуются, На информационный вход триггера 2 памяти импульс не поступает, и независимо от предыдущего состояния триггер устанавливается в нулевое состояние.

Таким образом, при совпадении символов О на выходе устройства импульс отсутствует.

Если в одном из объединяемых сигналов возникает символ 1, а в другом - символ О, то на выходе переноса одноразрядного двоичного сумматора 1 импульс отсутствует, а на выходе суммы возникает импульс. Если в предыдущем такте совпадали символы 1, то на выходе триггера 2 памяти, а также на выходе элементов 3 и 4 задержки на такт возникают импульсы. Эти импульсы проходят через элементы 6 и 7 совпадения и элемент ИЛИ 8 на элемент 5 совпадения. С выхода элемента 5 совпадения через элемент ИЛИ 9 импульс поступает на информационный вход триггера памяти и поддерживает его в единичном состоянии.

Если в предыдущем такте в объединяемых сигналах совпадали символы О, то на выходе триггера 2 памяти импульс отсутствует. Отсутствуют импульсы также на выходах элементов 3 и 4 задержки на такт элементов 6 и 7 совпадения, элемента ИЛИ 8, элемента 5 совпадения и элемента ИЛИ 9. Поэтому на информационном входе триггера 2 памяти импульс отсутствует и триггер остается в нулевом состоянии.

в предыдущем такте в объединяемых сигналах совпадал,и символы 1 и о, то на выходе элемента 3 задержки формируется импульс, а на выходе элемента 4 импульс отсутствует.

Если триггер 2 памяти в предыдущем такте находился в единичном состоянии, то на выходах элементов 6 и 7 совпадения, элемента ИЛИ 8, элемента 5 совпадения и элемента ИЛИ 9 импульс отсутствует и триггер 2 памяти переходит в нулевое состояние. I

Если в предьщущем такте триггер 2 памяти находился в нулевом состоянии, то на выходе элемента 6 совпадения формируется импульс. Этот импульс проходит через элемент ИЛИ 8, элемент 5 совпадения и элемент ИЛИ 9 на ин- формационньм вход триггера 2 памяти и устанавливает его в единичное состояние .

313075924

Поэтому если в одном из суммируе- суммы и переноса одноразрядного дво- мых сигналов возникает символ 1, ичного сумматора через первый и вто- а в другом - символ О, выходной рой элементы задержки соединены соот- сигнал устройства представляет собой ветственно с первыми входами первого чередующуюся последовательность сим- и второго элементов совпадения, к волов 1 и О. Память на один такт вторым входам которых подключены со- осуществляется триггером 2 памяти ответственно прямой и инверсньш вы- и элементами 3 и 4 задержки.ходы триггера памяти, входы управления первого и второго элементов заФормула изобретения О держки подключены к шине тактовой

частоты, выходы первого и второго

Устройство для объединения корре- элементов совпадения через первьш лированных импульсных сигналов, со- элемент ИЛИ подключены к первому держащее одноразрядный двоичньй сум- входу .третьего элемента совпадения, матор, к входам которого подключены 5 второй вход которого подключен к вы- первая и вторая входные шины соответ- ходу суммы одноразрядного двоичного ственно, первьш элемент ИПИ, триггер сумматора, выход третьего элемента памяти и шина тактовой частоты, о т- совпадения и выход переноса однораз- личающееся тем, что, с це- рядного двоичного сумматора соедине- лью повьшшния помехозащищенности и 20 ны с входами второго элемента ИЛИ, повьшения надежности работы, в него выход которого подключен к управляю- дополнительно введены два элемента щему входу триггера памяти, вход син- задержки, три элемента совпадения, хронизаДии которого соединен с шиной второй элемент ИЛИ, причем выходы тактовой частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство объединения сигналов дельта-модуляции | 1972 |

|

SU476682A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Устройство для преобразования двоичного кода в код системы счисления с отрицательным основанием /его варианты/ | 1982 |

|

SU1097994A1 |

| ПРЕОБРАЗОВАТЕЛЬ СТЫКОВ ДЛЯ ПЕРЕДАЧИ ЦИФРОВЫХ СИГНАЛОВ (ВАРИАНТЫ) | 1994 |

|

RU2105413C1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU962931A1 |

Изобретение относится к импульсной техникеу и может быть использовано при передаче по общему импульсфВыход суммы Выход переноса Г- ному каналу связи аналоговой информации от нескольких абонентов. Цель изобретения - повьшение помехозащищенности. Для достижения поставленной цели в устройство введены элементы 3,4 задержки, элементы 5,6,7, совпадения, элемент ИЛИ 9. Устройство также содержит одноразрядный двоичный сумматор 1, триггер 2 памяти и элемент ИЛИ 8. Повьшение помехозащищенности обеспечивается уменьшением искажения входных сигналов за счет обеспечения возможности их расфази- ровки и повьшения надежности. 1 ил. (Л Ц LT | СЛ со

| Устройство объединения сигналов дельта-модуляции | 1972 |

|

SU476682A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-04-30—Публикация

1983-01-26—Подача