11309258

Изобретение относится к радиотехнике и-может быть использовано в системах обработки и передачи дискретной информации, гидролокации и другой аппаратуре, где используется циф- 5 ровая фильтрация.

Целью изобретения является расширение функциональных возможностей устройства для цифровой обработки сигналов за счет обеспечения возможности работы в нелинейном режиме - фильтрации.

10

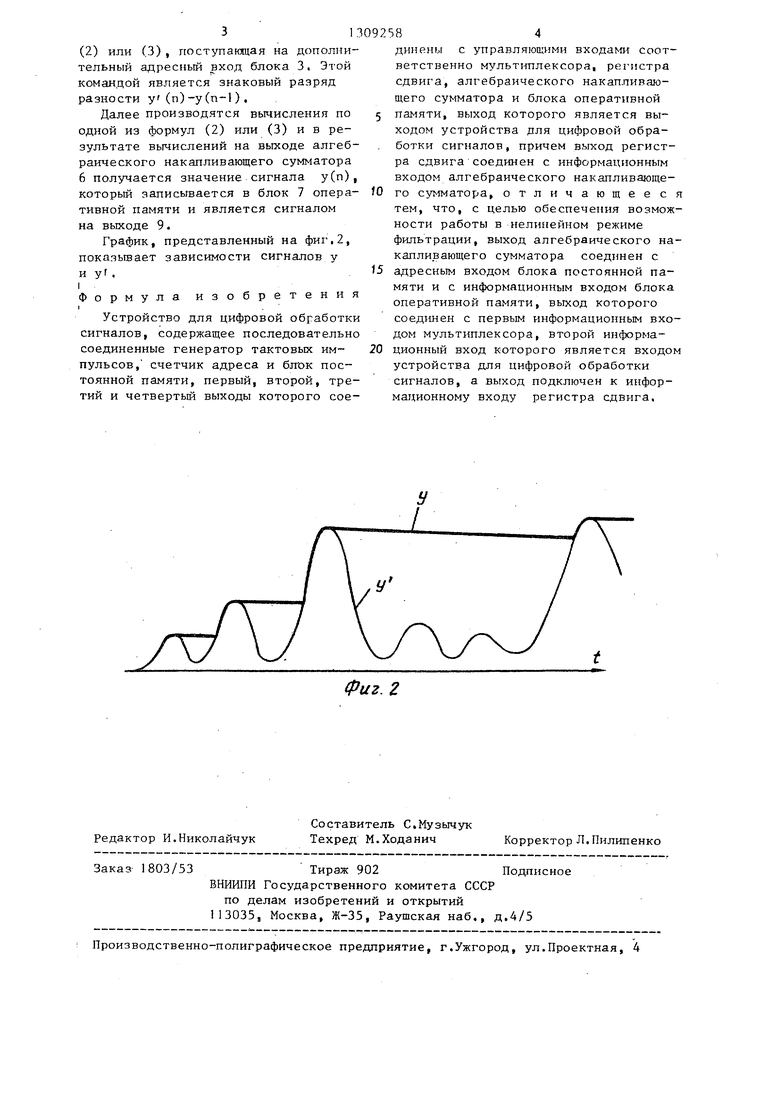

На фиг.) представлена структурная схема устройства для цифровой обработки сигналов; на фиг, 2 - вид выходного сигна,па устройства.

Устройство для цифровой обработки сигналов содержит генератор 1 тактовых импульсов, счетчик 2 адреса, блок 3 постоянной памятиJ мультиплексор 4, регистр 5 сдвига, алгебраический накапливающий сумматор 6, блок 7

оперативной памяти, вход 8 и выход 9 сигнал у (п-), умножается на единиустройства для цифровой обработки сигналов.

Устройство функционально можно разделить на две части: управляющую и операционную. Управляющая часть состоит из генератора 1 тактовых импульсов счетчика 2 адреса и блока 3, в котором заложен алгоритм работы всего устройства. Остальная часть устройства относится к операционной и состоит из мультиплексора 4, регистра 5 сдвига алгебраического накапливающего сумматора 6 и блока 7 оперативной памяти. Операционная часть предназначена для вычислений по формулам

у (п) х(п)с/.,+ у (п-1)(1-о/,); ()

y(ii) у(п-1)() +

+ y (n)e/i, если у (п)-у(п-1)0; (2)

у(п) у (п) (l-oij) +

+ у (п)о, если у (п)-у(п-1)7/0,

где х(п) сигнал на.входе Sj

-сигнал на выходе 9 в предыдущем цикле вычислений;

у (п) - промежуточный результат вычисленийр используемый для сравнения с сигналом на выходе 9;

-промежуточный результат вычислений, полученный

в предыдущем цикле вычис лений; у(п) - сигнал на выходе 9;

30

уСп)

y (n-l)

цу, т.е. сдвига не происходит, и пос тупает на вход алгебраического накап ливающего сумматора 6, где суммирует ся с накопленным в нем результатом вычислений. Далее по команде с блока 3 происходит сдвиг информатщи в регистре 5 сдвига на log-.o тактов, на выходе регистра 5 сдвига получает ся произведение у (п-1)о, , которое поступает на вход алгебраического на 35 капливающего сумматора б, где происходит очередная операция суммирования (или вычитания). I

Таким образом, в результате санных операций производится вычисление по формуле () значения у (п) которое по окончании, вычислений по формуле (1) з 1писывается в блок 7 оперативной Пс1мяти и хранится там

/ до следующего цикла вьиисленр Й, По команде из блока 3 из блока 7 оперативной памяти вызывается сигнал у(п-1) и подается через мультиплексор 4 и регистр 5 сдвига на вход гебраического накапливающего тора 6о Затем из блока 3 подается на управляк1Щий вход алгебраического накапливающего сумматора 6 команда на сравнение (вычитание) у (п) и

.j у(п-). После сравнения величин

У (п

у(п-1) на выходе алгебраического накапливающего сумматора 6 вырабатьшается команда на вычисление сигнала на выходе 9 по с1юрмуле

оС, - коэффициент умножения;

соответствующий постоянной времени фнпьтра d-i - коэффициент умножения,

соответствующий постоянной времени фильтра причем С

Устройство для цифровой обработки сигналов в каждом цикле вычислений работает следующим образом.

На вход 8 поступает информационный сигнал х(п) , мультиплексор 4 по команде из блока 3 передает его на вход регистра 5 сдвига, где он сдвигается на log d разрядов по команде блока 3, тем самым производится умножение x(n). Затем результат умножения поступает на вход алгебраического накапливающего сумматора 6, предварительно обнуленного в начале цикла вычислений. Затем из блока 7 оперативной памяти через мультиплексор 4 на регистр 5 сдвига подается

30

цу, т.е. сдвига не происходит, и поступает на вход алгебраического накапливающего сумматора 6, где суммируется с накопленным в нем результатом вычислений. Далее по команде с блока 3 происходит сдвиг информатщи в регистре 5 сдвига на log-.o тактов, на выходе регистра 5 сдвига получается произведение у (п-1)о, , которое поступает на вход алгебраического на- 35 капливающего сумматора б, где происходит очередная операция суммирования (или вычитания). I

Таким образом, в результате санных операций производится вычисление по формуле () значения у (п) которое по окончании, вычислений по формуле (1) з 1писывается в блок 7 оперативной Пс1мяти и хранится там

/ до следующего цикла вьиисленр Й, По команде из блока 3 из блока 7 оперативной памяти вызывается сигнал у(п-1) и подается через мультиплексор 4 и регистр 5 сдвига на вход гебраического накапливающего тора 6о Затем из блока 3 подается на управляк1Щий вход алгебраического накапливающего сумматора 6 команда на сравнение (вычитание) у (п) и

.j у(п-). После сравнения величин

У (п

у(п-1) на выходе алгебраического накапливающего сумматора 6 вырабатьшается команда на вычисление сигнала на выходе 9 по с1юрмуле

(2) или (3), поступающая на дополпи- тельный адресный вход блока 3. Этой командой является знаковый разряд разности у (п)-у(п-1).

Далее производятся вычисления по одной из формул (2) или (3) и в результате вычислений на выходе алгебраического накапливающего сумматора 6 получается значение сигнала у(п), который записывается в блок 7 оперативной памяти и является сигналом на выходе 9.

График, представленный на фиг.2, покаяьгоает зависимости сигналов у

и у ,

I

Формула изобретения

Устройство для цифровой обработки сигналов, содержащее последовательно соединенные генератор тактовых импульсов, счетчик адреса и блок постоянной памяти, первый, второй, третий и четвертый выходы которого соединены с управляющими входами соответственно мультиплексора, регистра сдвига, алгебраического накапливающего сумматора и блока оперативной памяти, выход которого является выходом устройства для цифровой обработки сигналов, причем выход регистра сдвига соединен с информационным входом алгебраического накапливающего сумматора, отличающее с я тем, что, с целью обеспечения возможности работы в нелинейном режиме фильтрации, выход алгебраического накапливающего сумматора соединен с

адресным входом блока постоянной памяти и с информационным входом блока оперативной памяти, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого является входом устройства для цифровой обработки сигналов, а выход подключен к информационному входу регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1983 |

|

SU1120348A1 |

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| Анализатор спектра | 1986 |

|

SU1691852A1 |

| Система управления вибростендом | 1984 |

|

SU1275396A1 |

| Цифровой генератор случайных процессов | 1978 |

|

SU750466A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Цифровой фильтр | 1985 |

|

SU1302296A1 |

Изобретение относится к радиотехнике. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности работы в Нелинейном режиме фильтрации. Устр-во состоит из управлянлцей и операционной частей. Первая из них состоит из генератора 1 тактовых импульсов, счетчика 2 адреса и блока 3 постоянной памяти , в котором заложен алгоритм работы всего устр-ва, а вто8 рая часть, осуществляющая вычисление по формулам - из мультиплексора 4, регистра сдвига (PC) 5, алгебраического накапливающего сумматора (АНС) 6 и блока 7 оперативной памяти. В каждом цикле поступающий на вход 8 информационный сигнал х(п) в PC 5 сдвигается на несколько разря дов.Умноженный т.обр. на коэф. oCi сигнал поступает на АЛС 6. Затем из блока 7 через мультиплексор 4 на PC 5 подается сигнал, который проходит по АНС 6 без сдвига. Далее информация сдвигается PC 5, суммируется в АНС 6 с накопленным в нем результатом и записывается в блок 7, где хранится со следующего цикла. Затем по команде блока 3 в АНС 6 происходит сравнение полученного значения со значением сигнала на выходе 9. Результат сравнения в виде знакового разряда разности поступает на адресный вход блока 3, где происходит вычисление выходного сигнала устр-ва по формуле. Результат записывается в блок 7 и поступает на выход 9. 2 ил. i (Л ОО О СО to ел 00 9 fpuz.l

фиг. 2

ор И.Николайчук 1803/53

Составитель С.Музычук Техред М.Ходанич

Корр Подп

Тираж 902 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор Л.Пилипенко Подписное

| Townsend М., Hoff М., Holm Р | |||

| An NMOS microprocessor for analog signal processing | |||

| - IEEE Trans, on computer, vol | |||

| Солесос | 1922 |

|

SU29A1 |

| Устройство для цифровой обработки сигналов | 1983 |

|

SU1105899A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-23—Подача