со С

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра | 1983 |

|

SU1120348A1 |

| Анализатор спектра | 1983 |

|

SU1151987A1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Анализатор спектра | 1983 |

|

SU1195356A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1309258A1 |

| Модуль процессора цифровой фильтрации | 1986 |

|

SU1316074A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

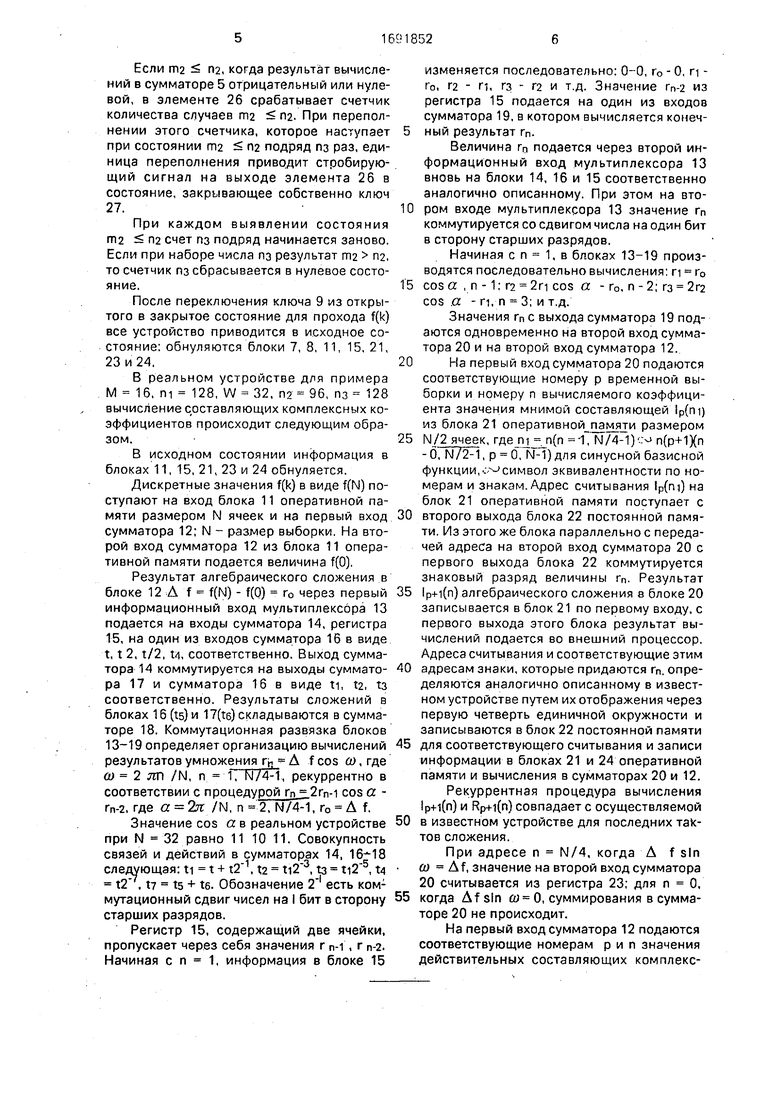

Изобретение относится к средствам цифровой вычислительной техники для спектрального-анализа сигналов с получением составляющих комплексных коэффициентов Фурье. Цель изобретения - повышение точности - достигается тем, что в устройство, содержащее первый блок 25 постоянной памяти, аналоге- цифровой преобразователь 3, восемь сумматоров 5, 12, 14, 16-20, три блока 11, 21, 24 оперативной памяти, первый мультиплексор 6, введены второй 4 и третий 13 мультиплексоры, четыре регистра 7, 8, 15, 23, второй блок 22 постоянной памяти и ключ 9. За счет возможности селекции полезного сигнала и выключения устройства из работы на неинформативных участках возрастает точность вычислений. 1 ил.

о ю

00

ел ю

Изобретение относится к средствам специализированной цифровой вычислительной техники для функционального спектрального анализа сигналов с получением составляющих комплексных коэффициентов Фурье в скользящем режиме и может быть использовано в акустике, медицине, гидролокации, в системах речевого управления, бортовой аппаратуре объектов при решении задач идентификации, распознавания, слежения, управления, передачи информации, диагностики, требующих высокой точности относительно погрешностей вычислений при обработке только полезных сигналов, низкого энергопотребления.

Цель изобретения - повышение точности анализатора спектра,

На чертеже представлена структурная схема анализатора спектра,

Анализатор спектра содержит информационный вход 1. первый выход 2, аналого-цифровой преобразователь 3, второй мультиплексор 4, второй сумматор 5, первый мультиплексор 6, первый и второй регистры 7 и 8, ключ 9, второй выход 10 устройства, второй блок 11 оперативной памяти, тоетий сумматор 12, третий мультиплексор 13, четвертый сумматор 14, четвертый регистр 15, пятый - восьмой сумматоры 16-19, первый сумматор 20, первый блок 21 оперативной памяти, второй 22 блок постоянной памяти, третий регистр 23, третий блок 24 оперативной памяти и первый блок 25 постоянной памяти. В состав ключа 9 входят элемент 26 управления и собственно ключ 27,

Анализатор спектра работает следующим образом.

В начальный момент обнуляются регистры 7 и 8, Сигнал после аналого-цифрового преобразования в преобразователе 3 в виде отдельных дискретных значений f(k) поступает на второй вход сумматора 5 через пер вый информационный вход мультиплексора 4. На управляющем входе ключа 9 установлен стробирующий уровень, запрещающий прохождение через него f(k). На первый вход сумматора 5 через второй информационный вход мультиплексора б из регистра 7 считывается и подается второе слагаемое. Результат сложения в сумматоре 5 записывается в регистр 7. Аналогичные операции производятся W раз. Конечный результат

W

m КЮ записывается в регистр 7. k 1

Регистр 7 cocTonf из двух регистров. С первым ведется работа при вычислении т, после чего значение гп пересылается во второй регистр, где сдвигается на logaW разрядов в сторону младших, а результат используется в последующих вычислениях Ш2.

После W циклов вычислений на первый вход сумматора 5 считывается и подается

величина mi, равная числу т, сдвинутому на logaW разрядов в сторону младших, W кратно степени числа 2, mi m/W - результат. Значение f(k) алгебраически складывается с mi, и результат с постоянно закомму0 тированным положительным знаковым разрядом на втором информационном входе мультиплексора 4 через этот открытый вход подается на второй вход сумматора 5. На первый вход сумматора 5 из регистра 8

5 через второй информационный вход мультиплексора 6 подается значение та. Результат второго сложения записывается в регистр 8. Аналогичные процедуры, в которых на каждое значение f(k) производится

0 два сложения повторяются М раз. Конечный

м

результат та У mi - f(k) записывается в

регистр 8.

с В следующем такте через первый информационный вход мультиплексора 6 на первый вход сумматора 5 поступает величина , считанная из блока 25 постоянной памяти. Из регистра 8 считывается и через

Q третий информационный вход мультиплексора 4 на второй вход сумматора 5 поступает значение та. Знаковый разряд алгебраической суммы та-гп из сумматора 5 подается на информационный вход ключа 9.

Если логическое значение знакового разряда равно О, что соответствует условию ГЛ2 mi, то на входе элемента 26 управления устанавливается стробирующий

Q уровень открытия собственно ключа 27, все последующие f(k) будут проходить на выход ключа 9.

Если логическое значение знакового разряда равно 1, что соответствует логиче(. скому условию ma ги, то ключ 9 свое состояние не изменяет.

В обоих случаях информация в регистре 8 обнуляется одновременно с вычислением

Ш2 - ГИ.

л После определения состояния m2 S ni проводится аналогичная процедура вычисления гп2 для следующих М дискретных значений и сравнение с гп.

Если состоянием является отношение

5 ГП2 ги, то вычисления для следующих М дискретных значений аналогичны, однако оценка производится с П2, подающимся из блока 2& постоянной памяти. После этого осуществляется операция определения последнего дискретного значения сигнала.

5

Если гп2 па, когда результат вычислений в сумматоре 5 отрицательный или нулевой, в элементе 26 срабатывает счетчик количества случаев m2 П2. При переполнении этого счетчика, которое наступает при состоянии ГП2 П2 подряд пз раз, единица переполнения приводит стробирую- щий сигнал на выходе элемента 26 в состояние, закрывающее собственно ключ 27.

При каждом выявлении состояния ГП2 П2 счет пз подряд начинается заново. Если при наборе числа пз результат т2 П2, то счетчик пз сбрасывается в нулевое состояние,

После переключения ключа 9 из открытого в закрытое состояние для прохода f(k) все устройство приводится в исходное состояние: обнуляются блоки 7, 8, 11, 15, 21, 23 и 24.

В реальном устройстве для примера М 16, m 128, W 32, П9 96, пз 128 вычисление составляющих комплексных коэффициентов происходит следующим образом.

В исходном состоянии информация в блоках 11. 15, 21, 23 и 24 обнуляется.

Дискретные значения f(k) в виде f(N) поступают на вход блока 11 оперативной памяти размером N ячеек и на первый вход сумматора 12; N - размер выборки. На второй вход сумматора 12 из блока 11 оперативной памяти подается величина f(0).

Результат алгебраического сложения в блоке 12 A f f(N) - f(0) Го через первый информационный вход мультиплексора 13 подается на входы сумматора 14, регистра 15, на один из входов сумматора 16 в виде t, t 2, t/2, t4. соответственно. Выход сумматора 14 коммутируется на выходы сумматора 17 и сумматора 16 в виде ti, t2, ts соответственно. Результаты сложений в блоках 16 (ts) и 17(te) складываются в сумматоре 18. Коммутационная развязка блоков 13-19 определяет организацию вычислений результатов умножения г A f cos и), где О) 2 лл /N, n 17 N/44, рекуррентно в соответствии с процедурой rn r.2rn-i cos a - rn-2, где а 2тг /N, n 2, N/4-1, r0 A f.

Значение cos а в реальном устройстве при N 32 равно 11 10 11. Совокупность связей и действий в сумматорах 14,

v1

следующая: ti t + t2 , t2 ti2 ,13 ti2 , t4 t2 . t ts + te. Обозначение 21 есть коммутационный сдвиг чисел на I бит в сторону старших разрядов.

Регистр 15, содержащий две ячейки, пропускает через себя значения г п-1 , г п-2. Начиная с n 1, информация в блоке 15

изменяется последовательно: 0-0, г0 - 0. п - Го, Г2 - п, гз - Г2 и т.д. Значение гп-2 из регистра 15 подается на один из входов сумматора 19, в котором вычисляется конеч- 5 ный результат ГР.

Величина гп подается через второй информационный вход мультиплексора 13 вновь на блоки 14, 16 и 15 соответственно аналогично описанному. При этом на вто0 ром входе мультиплексора 13 значение гп коммутируется со сдвигом числа на один бит в сторону старших разрядов.

Начиная с п 1, в блоках 13-19 производятся последовательно вычисления: п г0

5 cos а , п - 1; Г2 2п cos а - r0, n - 2; гз 2г2 cos а - п, п 3; и т.д.

Значения гп с выхода сумматора 19 подаются одновременно на второй вход сумматора 20 и на второй вход сумматора 12.

0 На первый вход сумматора 20 подаются соответствующие номеру р временной выборки и номеру п вычисляемого коэффициента значения мнимой составляющей Ip(ni) из блока 21 оперативной памяти размером

5 N/2 ячеек. (п l N/4-1) п(р+1Хп - б, N/2-1, р О, N-1) для синусной базисной функции,-.символ эквивалентности по номерам и знакам. Адрес считывания Ip(ni) на блок 21 оперативной памяти поступает с

0 второго выхода блока 22 постоянной памяти. Из этого же блока параллельно с передачей адреса на второй вход сумматора 20 с первого выхода блока 22 коммутируется знаковый разряд величины гп. Результат

5 1р-и(п) алгебраического сложения в блоке 20 записывается в блок 21 по первому входу, с первого выхода этого блока результат вычислений подается во внешний процессор. Адреса считывания и соответствующие этим

0 адресам знаки, которые придаются гп. определяются аналогично описанному в известном устройстве путем их отображения через первую четверть единичной окружности и записываются в блок 22 постоянной памяти

5 для соответствующего считывания и записи

информации в блоках 21 и 24 оперативной

памяти и вычисления в сумматорах 20 и 12.

Рекуррентная процедура вычисления

р-н(п) и Rp+i(n) совпадает с осуществляемой

0 в известном устройстве для последних тактов сложения.

При адресе n N/4, когда A f sin о) Af, значение на второй вход сумматора 20 считывается из регистра 23; для п О,

5 когда Afsln со 0, суммирования в сумматоре 20 не происходит.

На первый вход сумматора 12 подаются соответствующие номерам р и п значения действительных составляющих комплексных коэффициентов Rp(ri2) из блока 24 памяти размером N/2 ячеек по первому выходу, номера П2 и знаки для косинусной базисной функции определяются аналогично щ. Адрес считывания Rp(n2) задается с третьего блока 22.

Параллельно с адресом с четвертого выхода блока 22 на второй вход сумматора 12 коммутируется знаковый разряд г„ для вычисления Rp+i(ri2).

Результат алгебраического сложения в блоке 12 Rp+i() записывается в блок 24 по его информационному входу. С второго выхода этого блока результат вычислений поступает во внешний процессор. Для п О, когда Af coscu Af, , значение на второй вход сумматора 12 считывается из регистра 23, для n N/4, когда At cos CD 0, суммирования в блоке 12 не происходит. Регистр 23 построен на трехуровневых микросхемах. За счет обеспечения возможности се- лектирования полезного сигнала и выключения устройства из работы на неинформативных участках возрастает точность вычислений, экономится энергия.

Формула изобретения

Анализатор спектра, содержащий первый блок постоянной памяти, выход которого соединен с первым информационным входом первого мультиплексора, аналого- цифровой преобразователь, вход которого является информационным входом устройства, первый сумматор, первый информационный вход которого соединен с первым выходом первого блока оперативной памяти, информационный вход которого соединен с выходом первого сумматора, два блока оперативной памяти, выход первого мультиплексора соединен с первым информационным входом второго сумматора, шесть сумматоров, отличающийся тем, что, с целью повышения точности устройства, в него введены два мультиплексора, четыре регистра, второй блок постоянной памяти и ключ, управляющий вход которого соединен с выходом второго сумматора, второй информационный вход которого соединен с выходом второго мультиплексора, информационный вход ключа и первый информационный вход второго мультиплексора соединены с выходом аналого-цифрового преобразователя, выход второго сумматора

соединен с информационными входами первого и второго регистров и вторым информационным входом второго мультиплексора, третий информационный вход

которого соединен с выходом второго регистра, соединенным с вторым информационным входом первого мультиплексора, третий информационный вход которого соединен с выходом первого регистра, выход

ключа соединен с первым информационным входом второго блока оперативной памяти и первым информационным входом третьего сумматора, второй информационный вход которого соединен с выходом второго

блока оперативной памяти и выходом третьего регистра, информационный вход которого соединен с выходом третьего сумматора, соединенным с первым информационным входом третьего мультиплексора, второй информационный вход которого соединен с выходом второго блока оперативной памяти, выход третьего мультиплексора соединен с информационными входами четвертого и пятого сумматоров и

информационным входом четвертого регистра, выход четвертого сумматора соединен с информационными входами шестого и пятого сумматоров, выходы которых соединены с информационными входами седьмого

сумматора, выход которого соединен с первым информационным входом восьмого сумматбра второй информационный вход которого соединен с выходом четвертого регистра, выход восьмого сумматора, первый

выход второго блока постоянной памяти и выход третьего регистра соединены с вторым информационным входом первого сумматора, второй и третий выходы второго блока постоянной памяти соединены с адресными входами первого и третьего блоков оперативной памяти, второй выход первого блока оперативной памяти и первый выход третьего блока оперативной памяти являются первым и вторым выходами устройства,

информационный вход третьего блока оперативной памяти соединен с выходом третьего сумматора, а выход - с первым информационным входом третьего сумматора, четвертый выход второго блока постоянной памяти и выход восьмого сумматора соединены с вторым информационным входом третьего мультиплексора.

Авторы

Даты

1991-11-15—Публикация

1986-12-05—Подача