1

Изобретение относится к цифровой электронной технике и может быть использовано в качестве формирователя импульсных последовательностей в интегральных микросхемах на МДП-транзисторах.

Целью изобретения является повыи1ение надежности устройства за счет уменьшения площади интегрального конденсатора и уменьшения максимального напряжения на конденсаторе, а также за счет более быстрого разряда этого конденсатора в интервалах между импульсами.

Цель достигается путем введения в цепь заряда конденсатора дополнительного МДП- транзистора в диодном включении и введения в цепь разряда конденсатора дополнительного МДП-транзистора, работающего в режиме ключа и управляемого входным сигналом устройства.

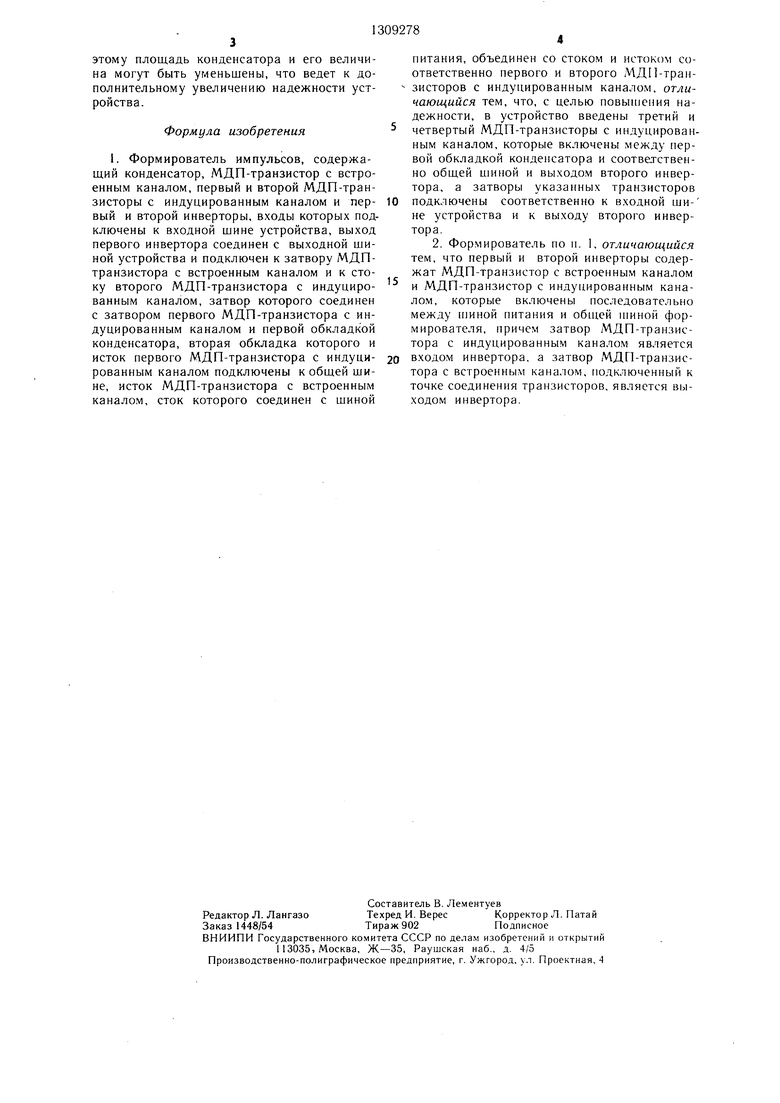

На чертеже приведена принципиальная схема формирователя импульсов.

Устройство содержит конденсатор 1, МДЦ-транзистор 2 с встроенным каналом, первый 3, второй 4, третий 5 и четвертый 6 МДП-транзисторы с индуцированным каналом, первый 7 и второй 8 инверторы, каждый из которых состоит из последовательно соединенных МДП-транзистора 9 с встроенным каналом и МДП-транзистора 10 с индуцированным каналом, которые включены между шиной 11 питания и общей шиной 12. Затвор МДП-транзистора 9 с встроенным каналом подключен к точке соединения транзисторов 9 и 10, инверторов 7 и 8 и является выходом 13 и 14 соответствующего инвертора, а затвор МДП-транзистора 10 с индуцированным каналом является входом 15 и 16 соответствующего инвертора.

Входы 15 и 16 соответственно первого 7 и второго 8 инверторов, а также затвор третьего МДП-транзистора 5 с индуцированным каналом подключены к входной шине 17, а выход 13 первого инвертора 7 соединен с выходной шиной 18 и подключен к затвору МДП-транзистора 2 с встроенным каналом и стоку второго МДП-транзистора 4 с индуцированным каналом. Выход 14 второго инвертора 8 через четвертый МДП-тран- зистор б с индуцированным каналом, затвор которого соединен с выходо.м того же инвертора, подключен к первой обкладке конденсатора 1, к которой подключены также затворы первого 3 и второго 4 и сток третьего 5 МДП-транзисторов с индуцированным каналом. Сток первого, исток второго МДП- транзисторов с индуцированным каналом и исток МДП-транзистора 2 с встроенным каналом, сток которого подключен к шине 11 питания, объединены. Истоки первого 3 и третьего 5 МДП-транзисторов а также вторая обкладка конденсатора 1 соединены с общей щиной 12.

Устройство функционирует следующим образом.

309278

2

В исходном состоянии на входную шину 17 подан единичный сигнал. На выходах 13 и 14 первого 7 и второго 8 инверторов, а также на выходной шине 18 при этом нуле- , вые сигналы. Третий МДП-транзистор 5 с индуцированным каналом открыт ц конденсатор 1 разряжен, а первый 3 и второй 4 МДП-транзисторы закрыты.

Для формирования единичного импульса на выходной шине 18 необходимо подать на

входную шину 17 нулевой сигнал на время, превышающее длительность формируемого импульса и равное, например, периоду следования.

При этом выходная шина 18 через от15 крытый МДП-транзистор 9 первого инвертора 7 быстро заряжается до напряжения источника питания, подключенного к шине 11 питания. Так формируется передний фронт выходного импульса.

Третий МДП-транзистор 5 с индуциро20 ванным каналом закрывается, и конденсатор 1 начинает заряжаться через МДП-транзистор 9 инвертора 8 и четвертый МДП- транзистор 6 с индуцированным каналом до напряжения, равного напряжению на ши25 не 11 питания за вычетом порогового напряжения четвертого МДП-транзистора 6 с индуцированным каналом, поскольку его затвор соединен со стоком.

При достижении напряжения на конденсаторе 1, равного пороговому напряжению

30 МДП-транзисторов с индуцированным каналом, первый .МДП-транзистор 3 с индуцированным каналом открывается, и напряжение на его стоке начинает уменьшаться. При дальнейшем увеличении напряжения на конденсаторе 1 и уменьшении напряжения на

35 истоке второго МДП-транзистора 4 с индуцированным каналом он открывается, и начинается формирование заднего фронта выходного импульса на выходной шине 18. Ток, протекающий через первый 3 и второй 4

Q МДП-транзисторы с индуцированным каналом, разряжает выходную шину 18 до низкого потенциала. МДП-транзистор 2 при этом подзапирается, что обеспечивает увеличение крутизны заднего фронта формируемого импульса.

45 При поступлении на входную шину 17 сигнала высокого уровня третий МДП-транзистор 5 с индуцированным каналом открывается, и конденсатор 1 быстро разряжается, что обеспечивает надежное запирание первого 3 и второго 4 МДП-транзисторов с индуцированным каналом, необходимое для подготовки формирования следующего импульса.

Введение четвертого МДП-транзистора 6 с индуцированным каналом в диодном вклю55 чении обеспечивает дополнительное сопротивление в цепи заряда конденсатора 1 и меньшее напряжение на конденсаторе, чем напряжение шины 11 питания. Благодаря

50

этому площадь конденсатора и его величина могут быть уменьшены, что ведет к дополнительному увеличению надежности устройства.

Формула изобретения

1. Формирователь импульсов, содержащий конденсатор, МДП-транзистор с встроенным каналом, первый и второй МДП-тран- зисторы с индуцированным каналом и первый и второй инверторы, входы которых подключены к входной щине устройства, выход первого инвертора соединен с выходной щи- ной устройства и подключен к затвору МДП- транзистора с встроенным каналом и к стоку второго МДП-транзистора с индуцированным каналом, затвор которого соединен с затвором первого МДП-транзистора с индуцированным каналом и первой обкладкой конденсатора, вторая обкладка которого и исток первого МДП-транзистора с индуцированным каналом подключены к общей шине, исток МДП-транзистора с встроенным каналом, сток которого соединен с шиной

питания, объединен со стоком и истоком соответственно первого и второго МДП-тран- зисторов с индуцированным каналом, отличающийся тем, что, с целью повышения надежности, в устройство введены третий и

четвертый МДП-транзисторы с индуцированным каналом, которые включены между первой обкладкой конденсатора и соответственно общей шиной и выходом второго инвертора, а затворы указанных транзисторов

подключены соответственно к входной ши- не устройства и к выходу второго инвертора.

2. Формирователь по п. 1, отличающийся тем, что первый и второй инверторы содержат МДП-транзистор с встроенным каналом и МДП-транзистор с индуцированным каналом, которые включены последовательно между питания и общей шиной формирователя, причем затвор МДП-транзистора с индуцированным каналом является

входюм инвертора, а затвор МДП-транзистора с встроенным каналом, подключенный к точке соединения транзисторов, является выходом инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения в постоянное | 1989 |

|

SU1631673A1 |

| Формирователь импульсов | 1982 |

|

SU1238230A1 |

| Преобразователь постоянного напряжения | 1986 |

|

SU1372523A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Буферное устройство | 1980 |

|

SU902258A1 |

Изобретение относится к области цифровой электронной техники. Цель изобретения - повышение надежности формирователя.. Формирователь импульсов содержит конденсатор 1, МДП-транзистор 2 с проводящим каналом, МДП-транзисторы 3 и 4 с индуцированным каналом и инверторы 7 и 8. Введение МДП-транзисторов 5 и 6 и выполнение каждого из инверторов 7 и 8 в виде МДП.-транзистора 9 с проводящим каналом и МДП-транзистора 10 с индуцированным каналом уменьшают плош,адь конденсатора 1, максимальное напряжение на нем и обеспечивают более быстрый разряд этого конденсатора в интервалах между импульсами. 1 3. п. ф-лы, 1 ил. (Л со о со ю 00

| Патент США № 4449066, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Интегральный формирователь импульсов | 1984 |

|

SU1211854A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-11—Подача