1

Изобретение относится к одновиб- раторам, формирующим импульс заданной длительности по перепаду входного сигнала, и предназначено для работы в интегральных цифровых схемах на МОП-транзисторах,

Целью изобретения является повышение стабильности длительности выходного импульса и быстродействия устройства за счет уменьшения влияния разброса параметров элементов устройства на длительность формируемого импульса и уменьшения длительности среза импульса.

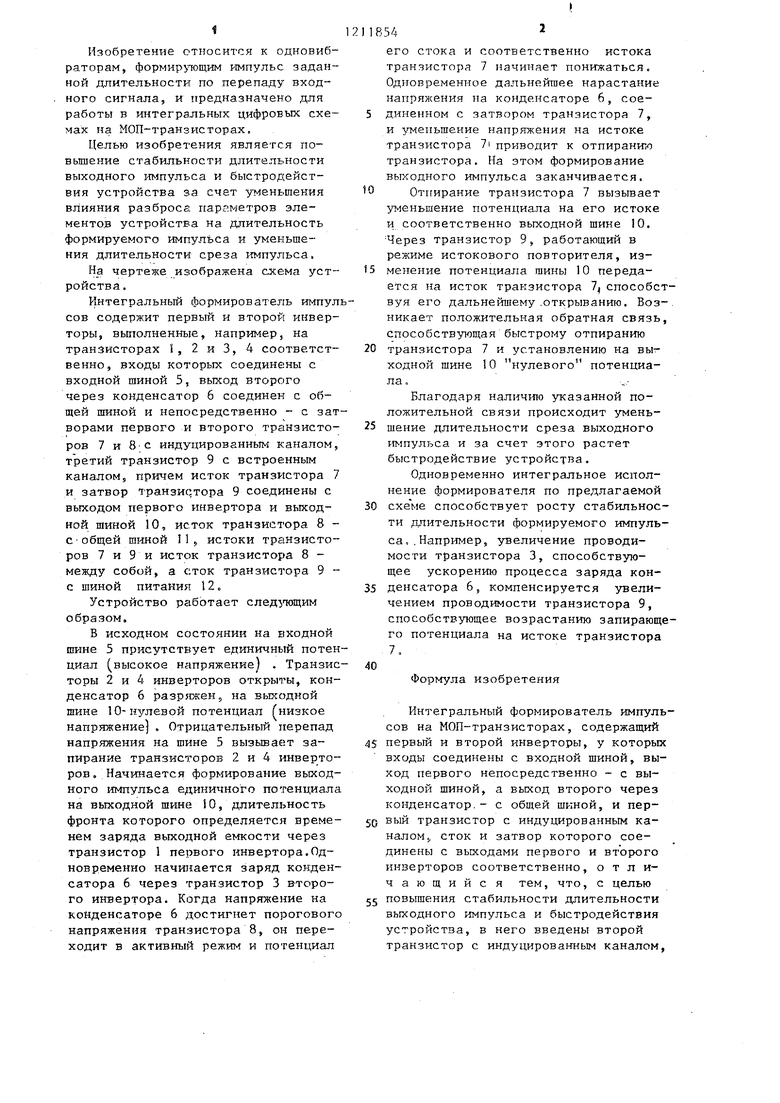

чертеже изображена схема устройства.

Интегральньга формирователь импулсов содержит первый и второй инверторы, вьшолненные, например, на транзисторах 1, 2 и 3, 4 соответственно, входы которых соединены с входной шиной 5, выход второго через конденсатор 6 соединен с общей шиной и непосредственно - с затворами первого и второго транзисторов 7 и 8 с индуцированным канапом, третий транзистор 9 с встроенным каналом, причем исток транзистора 7 и затвор транзистора 9 соединены с выходом первого инвертора и выходной шиной 10, исток транзистора 8 - с Общей шиной П, истоки транзисторов 7 и 9 и исток транзистора В - между собой, а сток транзистора 9 с шиной питания 12„

Устройство работает след тощим образом.

В исходном состоянии на входной шине 5 присутствует единичный потенциал (высокое напряжение) . Транзисторы 2 и 4 инверторов открыты, конденсатор 6 разряжен, на выходной шине 10-нулевой потенциал Гнизкое напряжение. Отрицательный перепад напряжения на шине 5 вызывает запирание транзисторов 2 и 4 инверторов. Начинается формирование выкод- ного импульса единичного потенциала на выходной шине iО, длительность фронта которого определяется временем заряда выходной емкости через транзистор 1 первого инвертора.Одновременно начинается заряд конденсатора 6 через транзистор 3 второго инвертора. Когда напряжение на конденсаторе 6 достигнет порогового напряжения транзистора 8, он переходит в активный режим и потенциал

4

его стока и соответственно истока транзистора 7 начинает понижаться. Одновременное дальнейтпее нарастание напряжения на конденсаторе 6, соединенном с затвором транзистора 7, и ллченьшение напряжения на истоке транзистора 7i приводит к отпираниэт транзистора. На этом формирование выходного импульса заканчивается.

Отпирание транзистора 7 вызывает уменьшение потенциала на его истоке и соответственно выходной шине 10. Через транзистор 9, работающий в режиме истокового повторителя, изменепие потенциала шины 10 передается на исток транзистора 7 способствуя его дальнейигему .открыванию. Воз-, никает положительная обратная связь, способствующая быстрому отпиранию

транзистора 7 и установлению на выходной шине 10 нулевого потенциала .

Благодаря наличию указанной положительной связи происходит уменьшение длительности среза выходного импульса и за счет этого растет быстродействие устройства.

Одновременно интегральное исполнение формирователя по предлагаемой

схе ме способствует росту стабильности длительности формируемого импульса, , Например, увеличение проводимости транзистора 3, способствующее ускорению процесса заряда конденсатора 6, компенсируется увеличением проводимости транзистора 9, способствующее возрастанию запирающего потенциала на истоке транзистора 7.

Формула изобретения

Интегральный формирователь импульсов на МОП-транзисторах, содержащий

первый и второй инверторы, у которых входы соединены с входной шиной, выход первого непосредственно - с выходной шиной, а вьгход второго через конденсатор.- с общей шиной, и первый транзистор с индуцированным каналом,, сток и затвор которого соединены с выходами первого и вторюго инверторов соответственно, о т л и- чающийс я тем, что, с целью

повышения стабильности длительности выходного импульса и быстродействия устройства, в него введены второй транзистор с индуцированным каналом.

31211854 .

затвор и сток которого соединены с встроенным каналом, затвор и исток затвором и истоком первого транзис- которого соединены со стоком и исто- тора соответственно, а исток - с ком первого транзистора соответствен- общей шиной, и третий транзистор с но, а сток - с шийой питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1985 |

|

SU1309278A1 |

| Устройство автоматического смещения | 1981 |

|

SU995673A1 |

| Интегральный электронный КМОП синапс | 2023 |

|

RU2808951C1 |

| Формирователь импульсов на МОП-транзисторах | 1984 |

|

SU1236604A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Стабилизатор постоянного напряжения | 1986 |

|

SU1372300A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| МДП-инвертор | 1990 |

|

SU1780184A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Динамический элемент памяти | 1988 |

|

SU1599898A1 |

Изобретение относится к одно- вибраторам, формирующим импульс заданной длительности по перепаду входного сигнала, и предназначено для работы в интегральных цифровых схемах на МОП-транзисторах. Устройство содержит два инвертора, выполненных, например, на транзисторах 1,2 и 3, 4 соответственно, входную шину 5, конденсатор 6, транзисторы 7 и 8 с индуцированным каналом, транзистор 9 с встроенным каналом, выходную шину 10 и общую шину 1 1 . Введение транзистора 8 с индуцированным каналом и транзистора 9 с встроенным каналом позволяет повысить стабильность длительности выходного импульса и быстродействие устройства за счет уменьшения влияния разброса параметров элементов устройства на длительность формируемого импульса и уменьшить длительность среза импульса. 1 ил. (Л «

| Волков С | |||

| Генераторы прямоугольных импульсов на МОП-элементах.- М.: Энергоиздат, 1981, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Сенситометр | 1922 |

|

SU1809A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-05—Подача