(5) БУФЕРНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| МДП-инвертор | 1990 |

|

SU1780184A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Формирователь импульсов | 1985 |

|

SU1309278A1 |

| Формирователь импульсов на мдптранзисторах | 1974 |

|

SU668092A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Формирователь импульса по включению напряжения питания | 1985 |

|

SU1272496A1 |

| Динамический сдвиговый регистр | 1981 |

|

SU993334A1 |

| Формирователь импульсов | 1979 |

|

SU843206A1 |

t

I Изобретение относится к импульсной и вычислительной технике и может быть использовано в качестве формирователя напряжения в цифровых схемах и для согласования уровней сигналов.

Известно буферное устройство, содержащее МДП-транзисторы с индуцированным каналом 13.

Недостаток этого устройства низкое быстродействие.

Наиболее близким к предлагаемому является буферное устройство, содержащее МДП-.транзисторы с индуцированным каналом и конденсатор 12.

Недостатком этого устройства является низкое быстродействие, обусловленное большой длительностью фронтов нарастания и спада выходного сигнала.

Цель изобретения - повышение быстродействия .

Указанная цель достигается тем, что в буферное устройство, содержащее первый, второй и МДПтранзисторы с индуцированным каналом и конденсатор, затвор первого МДП-транзистора соединен с истоком второго МДП-транзистора и через конденсатор с выходной шиной, исток

.первого МДП-транзистора подключен к стоку третьего МДП-транзистора и выходной шине, а сток первого МДПтранзистора соединен со- стоком и затвором второго ИДП-транзистора и шиной источника питания, введен четвертый МДП-транзистор,сток которого соединен с шиной смещения и затвором третьего МДП-транзистора, исток - с входной шиной и истоком третьего МДП-транзистора, а затвор с выходной шиной.

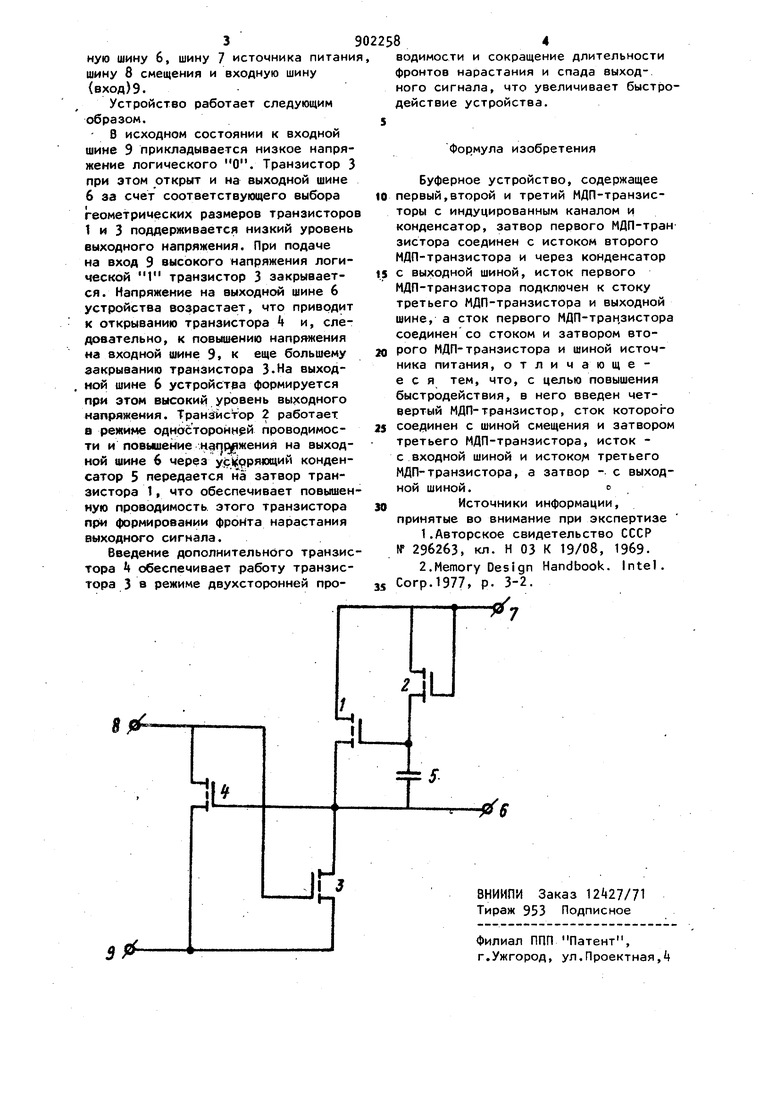

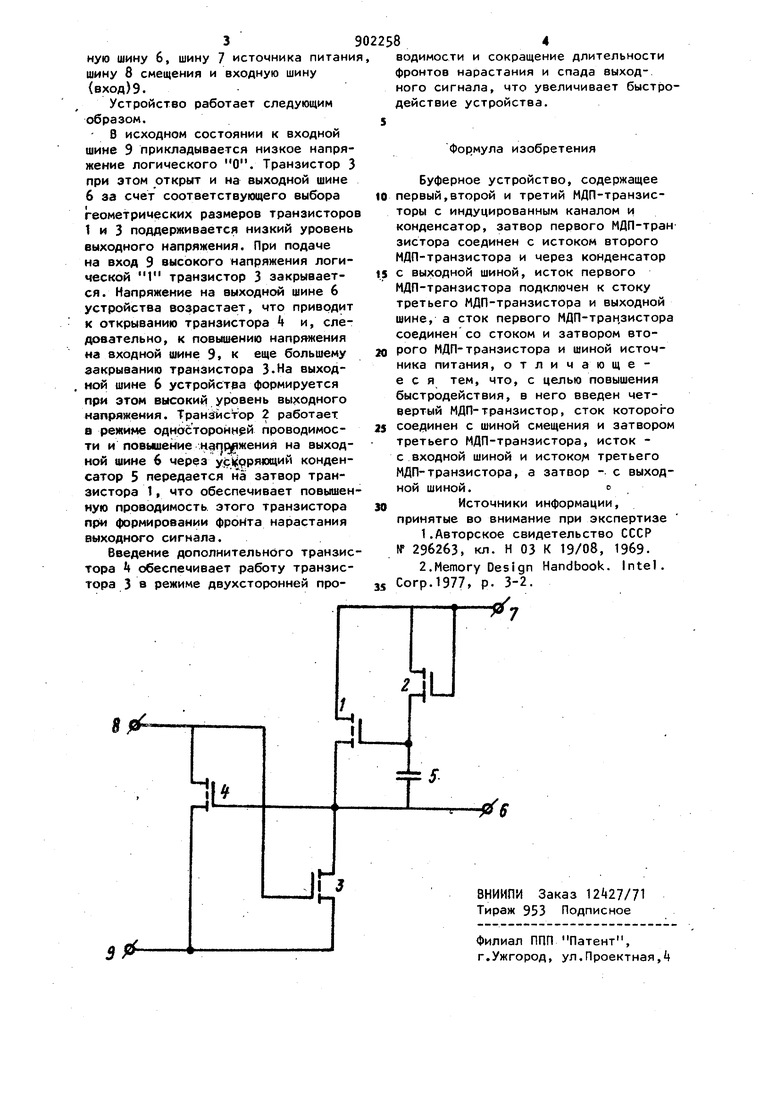

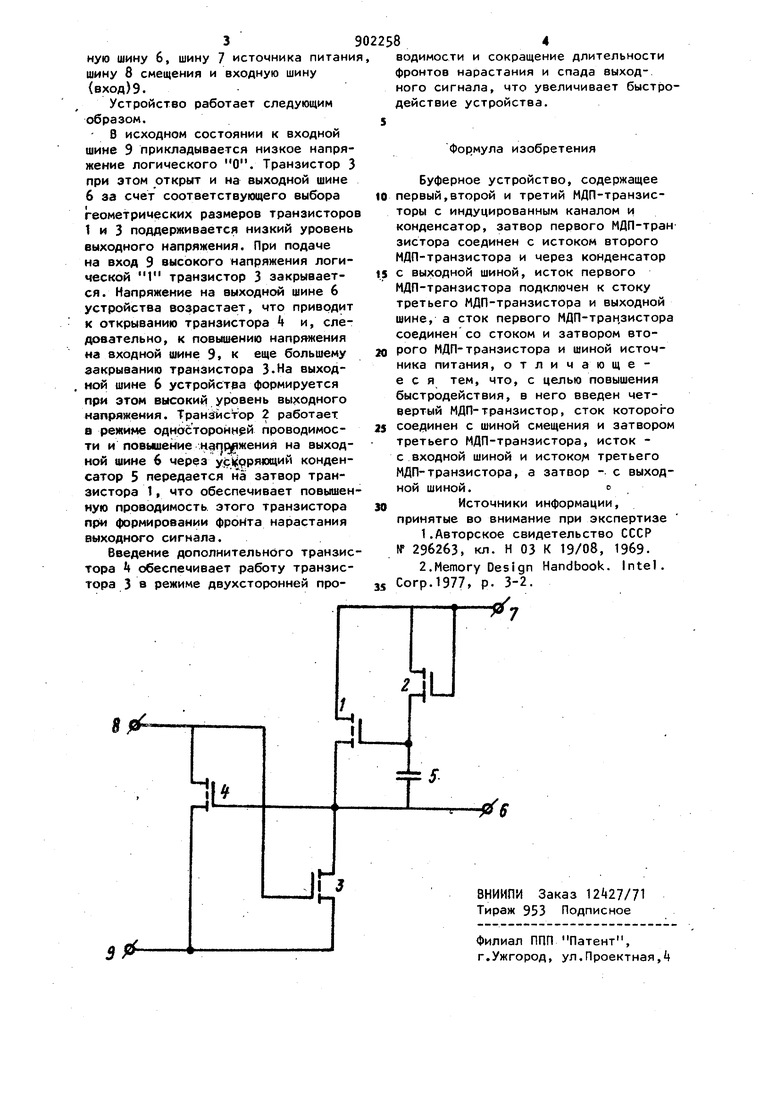

На чертеже представлена принци-. пиальная электрическая схема устройства.

Устройство содержит МДП-транзисторы 1-4 с индуцированным каналом, ускоряющий конденсатор 5. выходную шину 6, шину 7 источника питани шину 8 смещения и входную шину (вход)9.

Устройство работает следующим образом.

В исходном состоянии к входной шине 9 прикладывается низкое напряжение логического О. Транзистор 3 при этом открыт и на выходной шине 6 за счет соответствующего выбора геометрических размеров транзисторо 1 и 3 поддерживается низкий уровень выходного напряжения. При подаче на вход 9 высокого напряжения логической 1 транзистор 3 закрывается. Напряжение на выходной шине 6 устройства возрастает, что приводит к открыванию транзистора k и, следовательно, к повышению напряжения на входной шине 9 к еще большему закрыванию транзистора выходной шине 6 устройства формируется при этом высокий уровень выходного напряжения. Транзйстор 2 работает в режиме односторонней проводимоети и повышение напряжения на выходной шине 6 через у сЦрряющий конденсатор 5 передается на затвор транзистора 1, что обеспечивает повышенную проводимость, этого транзистора при формировании фронта нарастания выходного сигнала.

Введение дополнительного транзистора k обеспечивает работу транзистора 3 в режиме двухсторонней проводимости и сокращение длительности фронтов нарастания и спада выходного сигнала, что увеличивает быстродействие устройства.

Формула изобретения

Буферное устройство, содержащее первый,второй и третий МДП-транзисторы с индуцированным каналом и конденсатор, затвор первого МДП-тран зистора соединен с истоком второго МДП-транзистора и через конденсатор с выходной шиной, исток первого МДП-транзистора подключен к стоку третьего МДП-транзистора и выходной шине, а сток первого МДП-тран,зистора соединен со стоком и затвором второго МДП-транзистора и шиной источника питания, отличающееся тем, что, с целью повышения быстродействия, в него введен четвертый МДП-транзистор, сток которого соединен с шиной смещения и затвором третьего МДП-транзистора, исток с входной шиной и истоком третьего МДП-транзистора, а затвор

- с выходной шиной.

о

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-01-30—Публикация

1980-06-18—Подача