эл-та ИЛИ 8, мультиплексора 9, делителя 10, эл-та 11 задержки, счетчика 12 и эл-та ИЛИ 14. Система по

1

Изобретение относится к электросвязи и может быть использовано для передачи дискретных сообщений.

Цель изобретения - повышение помехозащищенности путем снижения взаимных помех.

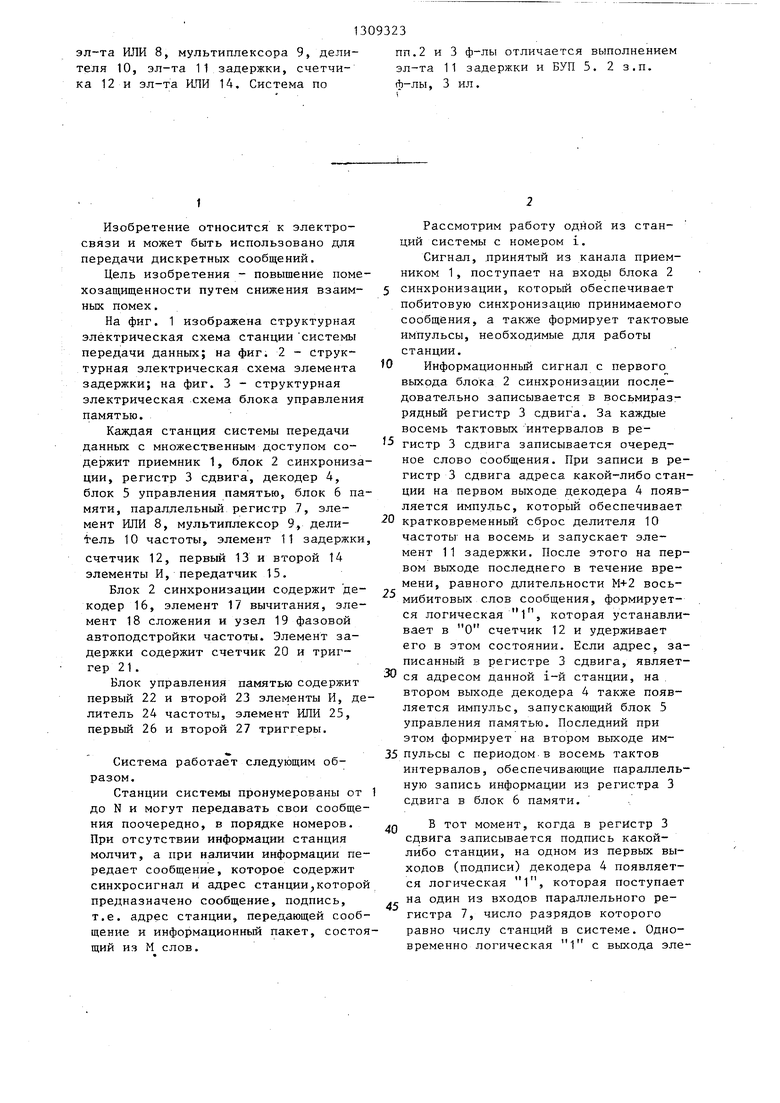

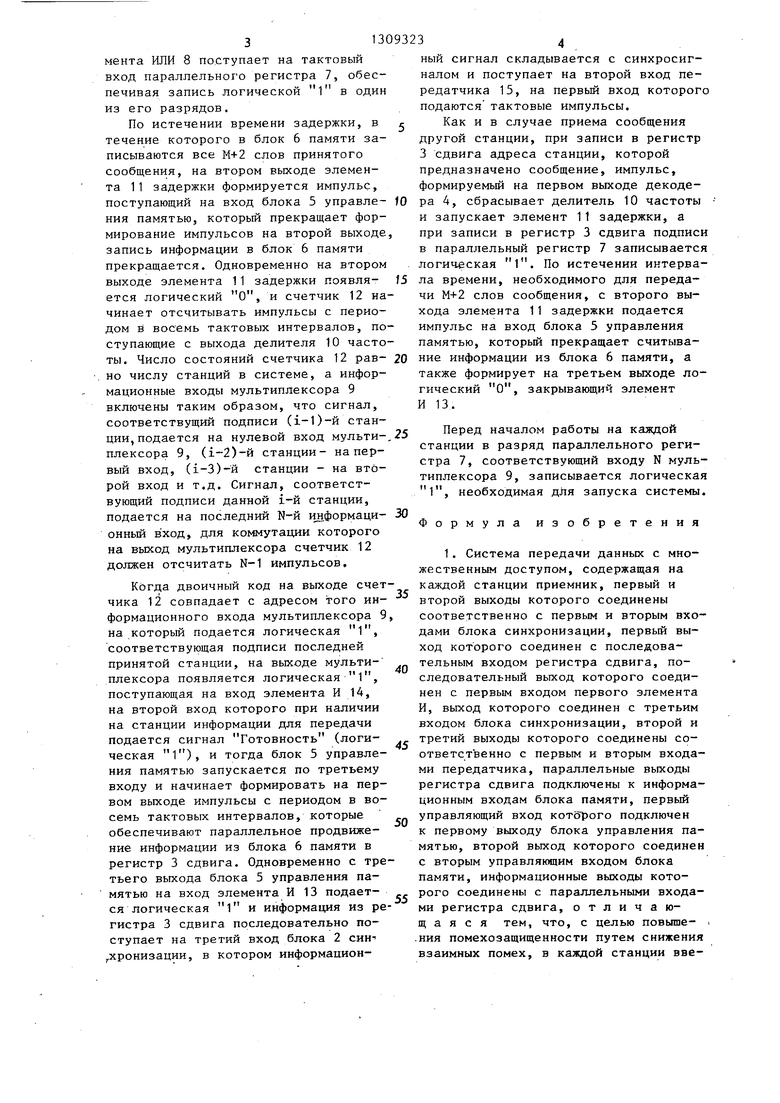

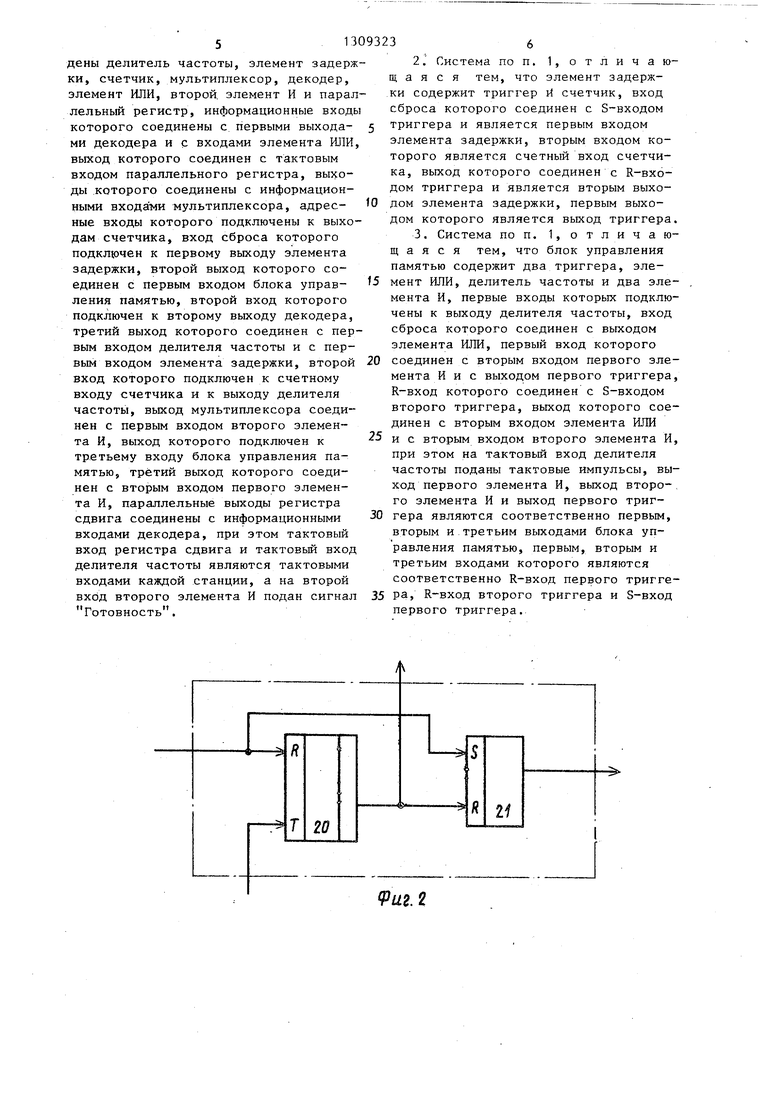

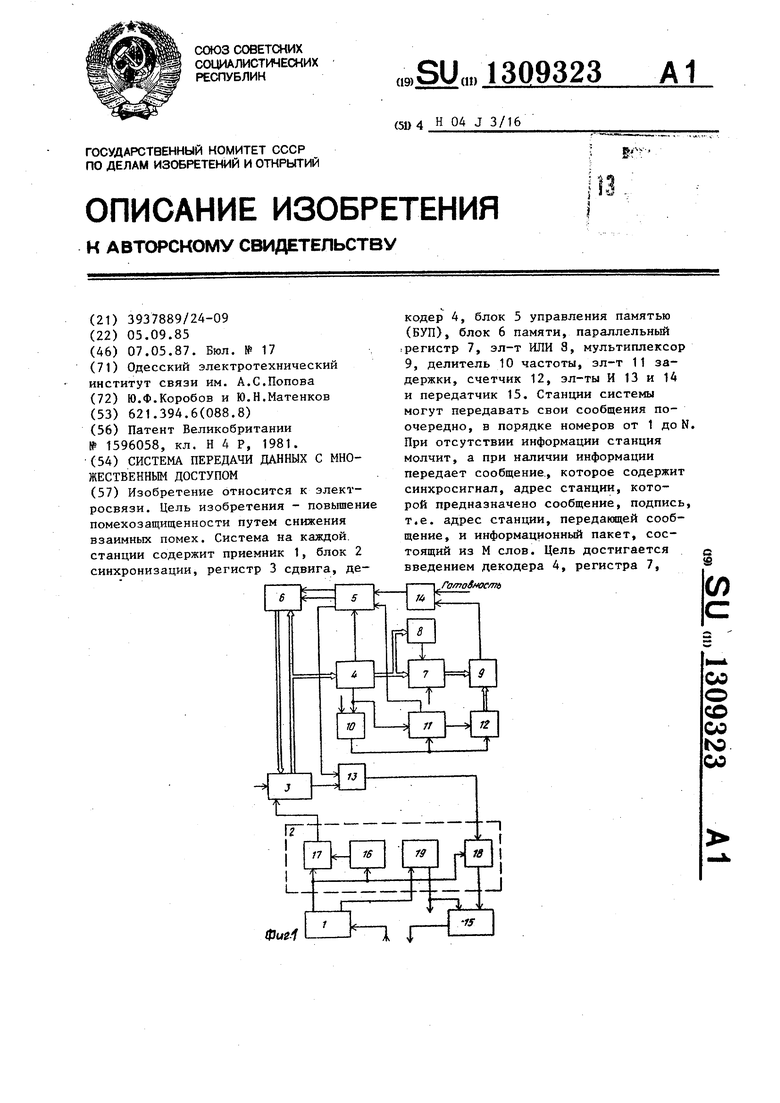

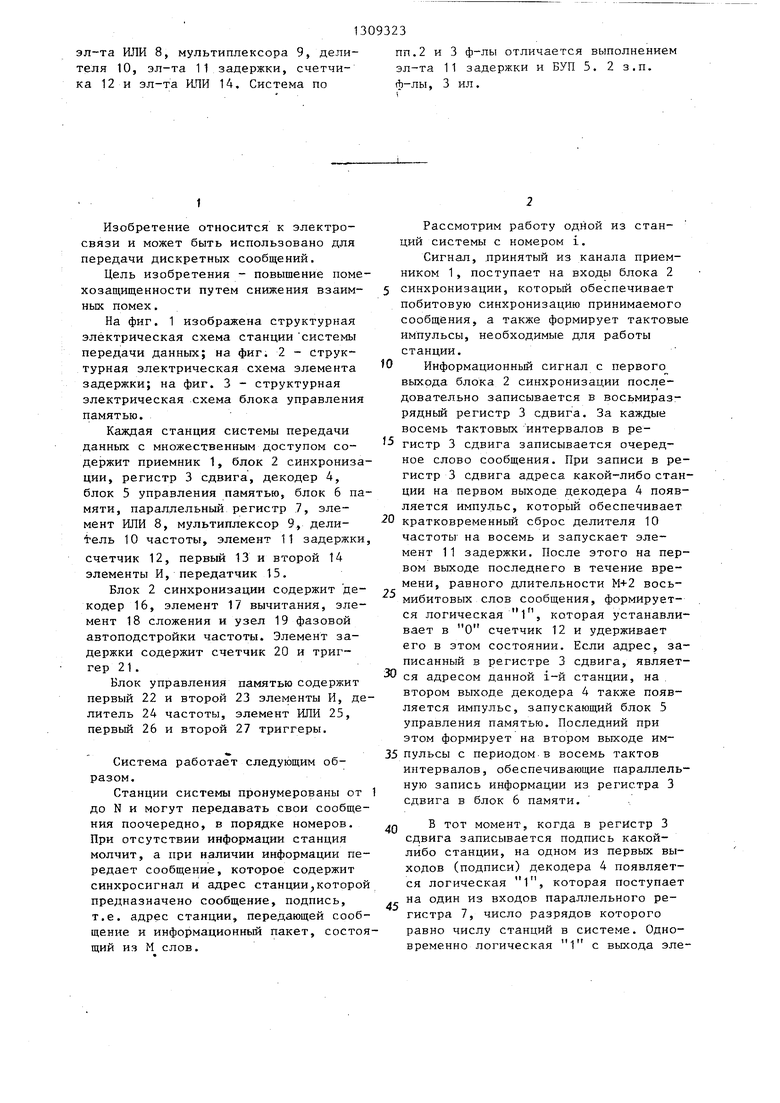

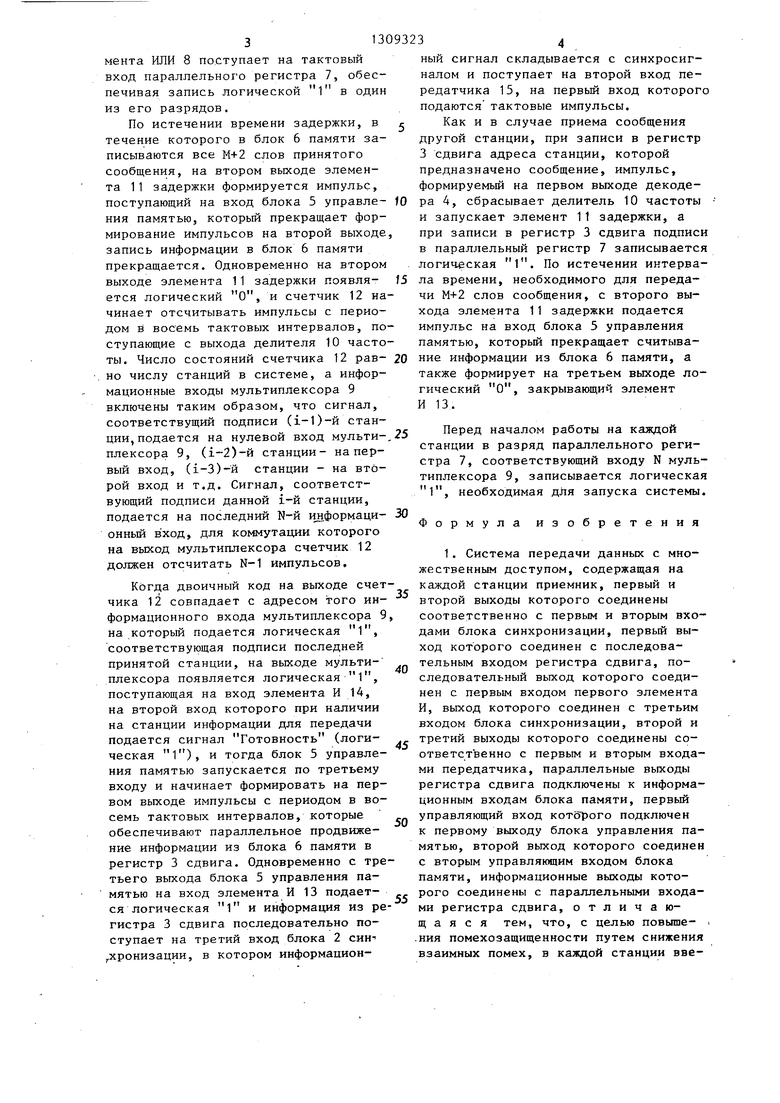

На фиг. 1 изображена структурная электрическая схема станции системы передачи данных; на фиг. 2 - структурная электрическая схема элемента задержки; на фиг. 3 - структурная электрическая схема блока управления памятью.

Каждая станция системы передачи данных с множественным доступом содержит приемник 1, блок 2 синхронизации, регистр 3 сдвига, декодер 4, блок 5 управления памятью, блок 6 памяти, параллельный регистр 7, элемент ИЛИ 8, мультиплексор 9, делитель 10 частоты, элемент 11 задержки

счетчик 12, первый 13 и второй 14 элементы И, передатчик 15.

Блок 2 синхронизации содержит декодер 16, элемент 17 вычитания, элемент 18 сложения и узел 19 фазовой автоподстройки частоты. Элемент задержки содержит счетчик 20 и триггер 21.

Блок управления памятью содержит первый 22 и второй 23 элементы И, делитель 24 частоты, элемент ИЛИ 25, первьш 26 и второй 27 триггеры.

Система работает следующим образом.

Станции системы пронумерованы от до N и могут передавать свои сообщения поочередно, в порядке номеров. При отсутствии информации станция молчит, а при наличии информации передает сообщение, которое содержит синхросигнал и адрес станции,которой предназначено сообщение, подпись, т.е. адрес станции, передающей сообщение и информационньм пакет, состоящий из М слов.

ПП.2 и 3 ф-лы отличается выполнением эл-та 11 задержки и БУП 5. 2 з.п. ф-лы, 3 ил,

Рассмотрим работу одной из станий системы с номером i.

Сигнал, лринятый из канала приемником 1, поступает на входы блока 2

синхронизации, который обеспечивает побитовую синхронизацию принимаемого сообщения, а также формирует тактовые импульсы, необходимые для работы станции.

Информационный сигнал с первого выхода блока 2 синхронизации последовательно записывается в восьмираз- рядньй регистр 3 сдвига. За каждые восемь Тактовых интервалов в регистр 3 сдвига записывается очередное слово сообщения. При записи в регистр 3 сдвига адреса какой-либо станции на первом выходе декодера 4 появляется импульс, который обеспечивает

кратковременный сброс делителя 10 частоты на восемь и запускает элемент 11 задержки. После этого на первом выходе последнего в течение времени, равного длительности М+2 восьмибитовых слов сообщения, формируется логическая l, которая устанавливает в О счетчик 12 и удерживает его в этом состоянии. Если адрес, записанный в регистре 3 сдвига, является адресом данной i-й станции, на втором выходе декодера 4 также появляется импульс, запускающий блок 5 управления памятью. Последний при этом формирует на втором выходе импульсы с периодом в восемь тактов интервалов, обеспечивающие параллельную запись информации из регистра 3 сдвига в блок 6 памяти.

В тот момент, когда в регистр 3 сдвига записывается подпись какой- либо станции, на одном из первых выходов (подписи) декодера 4 появляется логическая 1, которая поступает

на один из входов параллельного ре- -,

гистра 7, число разрядов которого

равно числу станций в системе. Одновременно логическая 1 с выхода эле

мента ИЛИ 8 поступает на тактовый вход параллельного регистра 7, обеспечивая запись логической 1 в один из его разрядов.

По истечении времени задержки, в течение которого в блок 6 памяти записываются все М+2 слов принятого сообщения, на втором выходе элемента 11 задержки формируется импульс, поступающий на вход блока 5 управле- НИН памятью, который прекращает формирование импульсов на второй выходе запись информации в блок 6 памяти прекращается. Одновременно на втором выходе элемента 11 задержки появля- ется логический О, и счетчик 12 начинает отсчитывать импульсы с периодом в восемь тактовых интервалов, поступающие с выхода делителя 10 частоты. Число состояний счетчика 12 рав- но числу станций в системе, а информационные входы мультиплексора 9 включены таким образом, что сигнал, соответствущий подписи (1-1)-й станции, подается на нулевой вход мультиплексора 9, (г-2)-й станции- на первый вход, (1-3)-й станции - на второй вход и т.д. Сигнал, соответствующий подписи данной i-й станции, подается на последний W-й информаци- онный вход, для коммутации которого на выход мультиплексора счетчик 12 должен отсчитать N-1 импульсов.

Когда двоичный код на выходе счетчика 12 совпадает с адресом того информационного входа мультиплексора 9 на который подается логическая 1, соответствующая подписи последней принятой станции, на выходе мульти- плексора появляется логическая 1, поступающая на вход элемента И 14, на второй вход которого при наличии на станции информации для передачи подается сигнал Готовность (логическая 1), и тогда блок 5 управления памятью запускается по третьему входу и начинает формировать на первом выходе импульсы с периодом в восемь тактовых интервалов, которые обеспечивают параллельное продвижение информации из блока 6 памяти в регистр 3 сдвига. Одновременно с третьего выхода блока 5 управления памятью на вход элемента И 13 подается логическая 1 и информация из регистра 3 сдвига последовательно поступает на третий вход блока 2 син- хронизации, в котором информацион

O 5 0 5 0

0

5

0

5

ный сигнал складывается с синхросигналом и поступает на второй вход передатчика 15, на первый вход которого подаются тактовые импульсы.

Как и в случае приема сообщения другой станции, при записи в регистр 3 сдвига адреса станции, которой предназначено сообщение, импульс, формируемый на первом выходе декодера 4, сбрасывает делитель 10 частоты и запускает элемент 11 задержки, а при записи в регистр 3 сдвига подписи в параллельный регистр 7 записывается логическая 1. По истечении интервала времени, необходимого для передачи М+2 слов сообщения, с второго выхода элемента 11 задержки подается импульс на вход блока 5 управления памятью, который прекращает считывание информации из блока 6 памяти, а также формирует на третьем выходе логический О, закрывакяцич элемент И 13.

Перед началом работы на каждой станции в разряд параллельного регистра 7, соответствующий входу N мультиплексора 9, записывается логическая 1, необходимая для запуска системы.

Формула изобретения

1. Система передачи данных с множественным доступом, содержащая на каждой станции приемник, первый и второй выходы которого соединены соответственно с первым и вторым входами блока синхронизации, первый выход которого соединен с последовательным входом регистра сдвига, последовательный выход которого соединен с первым входом первого элемента И, выход которого соединен с третьим входом блока синхронизации, второй и третий выходы которого соединены соответственно с первым и вторым входами передатчика, параллельные выходы регистра сдвига подключены к информационным входам блока памяти, первый управляющий вход которого подключен к первому выходу блока управления памятью, второй выход которого соединен с вторым управляющим входом блока памяти, информационные выходы которого соединены с пареьапельными входами регистра сдвига, отличающаяся тем, что, с целью повыше- . .ния помехозащищенности путем снижения взаимных помех, в каждой станции внедены делитель частоты, элемент задержки, счетчик, мультиплексор, декодер, элемент ИЛИ, второй, элемент И и параллельный регистр, информационные входы которого соединены с первыми выходами декодера и с входами элемента ШШ, выход которого соединен с тактовым входом параллельного регистра, выходы которого соединены с информацион2. Система по п. 1, отличаю щаяся тем, что элемент задерж- ,ки содержит триггер rt счетчик, вход сброса которого соединен с S-входом триггера и является первым входом элемента задержки, вторым входом которого является счетный вход счетчика, выход которого соединен с R-BXO дом триггера и является вторым выховыми входами мультиплексора, адрес- tO дом элемента задержки, первым выходом которого является выход триггер 3. Система по п. 1, отличаю Щ

вые входы которого подключены к выходам счетчика, вход сброса которого подключен к первому выходу элемента задержки, второй выход которого соединен с первым входом блока управления памятью, второй вход которого подключен к второму выходу декодера, третий выход которого соединен с первым входом делителя частоты и с первым входом элемента задержки, второй вход которого подключен к счетному входу счетчика и к выходу делителя частоты, выход мультиплексора соединен с первым входом второго элемента И, выход которого подключен к третьему входу блока управления памятью, третий выход которого соединен с вторым входом первого элемента И, параллельные выходы регистра сдвига соединены с информационными входами декодера, при этом тактовый вход регистра сдвига и тактовьй вход делителя частоты являются тактовыми входами каждой станции, а на второй вход второго элемента И подан сигнал Готовность.

20

2. Система по п. 1, отличающаяся тем, что элемент задерж- ,ки содержит триггер rt счетчик, вход сброса которого соединен с S-входом триггера и является первым входом элемента задержки, вторым входом которого является счетный вход счетчика, выход которого соединен с R-BXO- дом триггера и является вторым выходом элемента задержки, первым выходом которого является выход триггера. 3. Система по п. 1, отличаю- Щ

а я с я тем, что блок управления

памятью содержит два триггера, элемент ИЛИ, делитель частоты и два элемента И, первые входы которых подключены к выходу делителя частоты, вход сброса которого соединен с выходом элемента ИЛИ, первый вход которого соединен с вторым входом первого элемента И и с выходом первого триггера, R-вход которого соединен с S-входом второго триггера, выход которого соединен с вторым входом элемента ИЛИ и с вторым входом второго элемента И, при этом на тактовьй вход делителя частоты поданы тактовые импульсы, выход первого элемента И, выход второ-, го элемента И и выход первого триггера являются соответственно первым, вторым и третьим выходами блока уп- равления памятью, первым, вторым и третьим входами которого являются соответственно R-вход первого триггера, R-вход второго триггера и S-вход первого триггера.

2f

VU2.2

24

25

26

25

27

I U3.3

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для автоматического измерения гидрологических параметров | 1985 |

|

SU1325301A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Контроллер станции локальной сети | 1988 |

|

SU1647590A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехозащищенности путем снижения взаимных помех. Система на каждой, станции содержит приемник 1, блок 2 синхронизации, регистр 3 сдвига, декодер 4, блок 5 управления памятью (БУП), блок 6 памяти, параллельный : регистр 7, эл-т ИЛИ 8, мультиплексор 9, делитель 10 частоты, эл-т 11 задержки, счетчик 12, эл-ты И 13 и 14 и передатчик 15. Станции системы могут передавать свои сообщения поочередно, в порядке номеров от 1 до N. При отсутствии информации станция Молчит, а при наличии информации передает сообщение., которое содержит синхросигнал, адрес станции, которой предназначено сообщение, подпись, т.е. адрес станции, передающей сообщение, и информационный пакет, состоящий из М слов. Цель достигается введением декодера 4, регистра 7, i (Л со о со со to со

| Переносная лестница для транспортного средства | 1988 |

|

SU1596058A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-05-07—Публикация

1985-09-05—Подача