1131

Изобретение относится к вычислиельной технике и может быть использовано в управляющих вычислительных системах для обеспечения работы в реальном масштабе времени.

Цель изобретения - расширение функциональных возможностей за счет обеспечения непрерьшности работы таймера во время снитывания с него инормации.

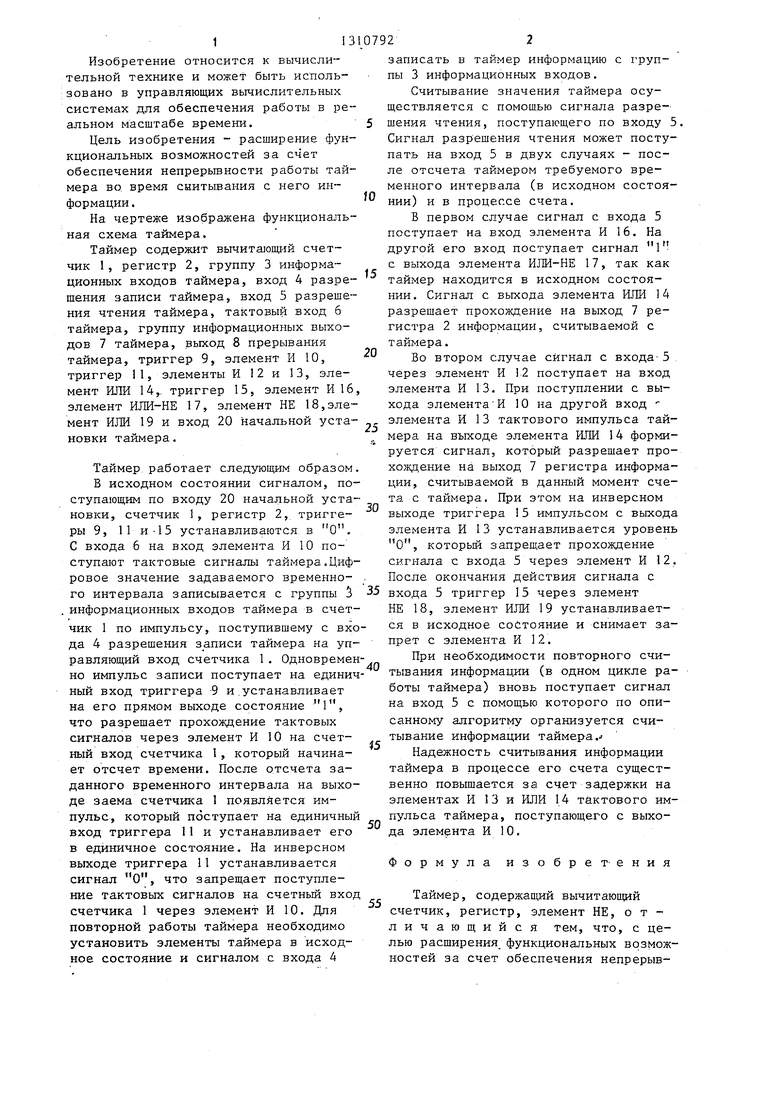

На чертеже изображена функциональная схема таймера.

Таймер содержит вычитагопц-1й счетчик 1, регистр 2, группу 3 информационных входов таймера, вход 4 разреения записи таймера, вход 5 разрешения чтения таймера, тактовый вход 6 таймера, группу информационных выхоов 7 таймера, выход 8 прерывания таймера, триггер 9, элемент И 10, триггер 11, элементы И 12 и 13, элемент шта 14,. триггер 15, элемент И 16, элемент ИЛИ-НЕ 17, элемент НЕ 18,элемент ИЛИ 19 и вход 20 начальной установки таймера.

Таймер, работает следуюш,им образом.

В исходном состоянии сигналом, поступающим по входу 20 начальной установки, счетчик 1, регистр 2, триггеры 9, 11 и-15 устанавливаются в О. С входа 6 на вход элемента И 10 поступают тактовые сигналы таймера,Цифровое значение задаваемого временного интервала записывается с группы 5 информационных входов таймера в счетчик 1 по импульсу, поступившему с входа 4 разрешения з аписи таймера на управляющий вход счетчика 1. Одновременно импульс записи поступает на единичный вход триггера -9 и .устанавливает на его прямом выходе состояние 1, что разрешает прохождение тактовых сигналов через элемент И 10 на счетный вход счетчика 1, который начинает отсчет времени. После отсчета заданного временного интервала на выходе заема счетчика 1 появляется импульс, который поступает на единичный вход триггера 11 и устанавливает его в единичное состояние. На инверсном выходе триггера 11 устанавливается сигнал О, что запрещает поступление тактовых сигналов на счетный вход счетчика 1 через элемент И 10. Для повторной работы таймера необходимо установить элементы таймера в исходное состояние и сигналом с входа 4

22

записать в таймер информацию с группы 3 информационных входов.

Считывание значения таймера осуществляется с помошью сигнала разре-- шения чтения, поступающего по входу 5, Сигнал разрешения чтения может поступать на вход 5 в двух случаях - после отсчета таймером требуемого временного интервала (в исходном состоя- нии) и в процбшсе счета.

В первом случае сигнал с входа 5 поступает на вход элемента И 16. На другой его вход поступает сигнал с выхода элемента ИЛИ-НЕ 17, так как таймер находится в исходном состоянии. Сигнал с выхода элемента ИЛИ 14 разрешает прохождение на выход 7 регистра 2 информации, считываемой с таймера.

Во втором случае сигнал с входа-5 . через элемент И 12 поступает на вход элемента И 13. При поступлении с выхода элемента И 10 на другой вход элемента И 13 тактового импульса таймера на выходе элемента ИЛИ 14 формируется сигнал, который разрешает прохождение на выход 7 регистра информации, считываемой в данный момент счета с таймера. При этом на инверсном выходе триггера 15 импульсом с выхода элемента И 13 устанавливается уровень О, который запрещает прохождение сигнала с входа 5 через элемент И 12. После окончания действия сигнала с входа 5 триггер 15 через элемент

НЕ 18, элемент ИЛИ 19 устанавливается в исходное состояние и снимает запрет с элемента И 12.

При необходимости повторного счи- тывания информации (в одном цикле работы таймера) вновь поступает сигнал на вход 5 с помощью которого по описанному алгоритму организуется считывание информации таймера.

Надежность считывания информации таймера в цроцессе его счета существенно повышается за счет задержки на элементах И 13 и ИЛИ 14 тактового импульса таймера, поступающего с выхо

да элемента И 10.

Формула изобретения

Таймер, содержаш 1й вычитающий счетчик, регистр, элемент НЕ, отличающийся тем, что, с целью расширения; функциональных возможностей за счет обеспечения непрерыв313

ности работы таймера во время считывания с него информации, в таймер введены три триггера, четыре элемента И, два элемента ИЛИ, причем группа входов задания временного интерва ла таймера соединена с группой инфор мационных входов счетчика, группа вы ходов разрядов которого соединена с группой входов элемента ИЛИ-НЕ и с группой информадионных входов регист ра, вход разрешения записи которого соединен с выходом первого элемента ИЛИ, выход заема счетчика соединен с единичным входом первого триггера и является выходом прерывания таймера, группа выходов регистра является группой информационных выходов таймера, инверсный выход первого тригге ра соединен с первым входом первого элемента И, второй вход которого является тактовым входом таймера, вход разрешения записи таймера соединен с входом разрешения записи счетчика и с единичным входом второго триггера, выход которого соединен с третьим ; входом первого элемента И, выход которого соединен со счетным входом

Составитель Е. Торопов Редактор Е. Копча Техред И.Попович

Заказ 1891/44 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5

fO

07924

счетчика и- с первым входом второго элемента И, второй вход которого соединен с выходом третьего элемента И, вход разрешения чтения таймера соединен с входом элемента НЕ, с первым входом третьего элемента И и с первым входом четвертого элемента И, второй вход которого соединён с выходом элемента ИЛИ-НЕ, вход начальной установки таймера соединен с входом установки в О счетчика, с входом установки в О регистра, с нулевым входом первого триггера, с нулевым входом второго триггера и с 5 первым входом второго элемента ИЛИ, выход которого соединен с нулевым входом третьего триггера, единичный вход которого соединен с выходом второго элемента И и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, инверсный вькод тре - тьего триггера соединен с вторым входом третьего элемента И, выход элемента НЕ соединен с вторым входом второго элемента ИЛИ.

20

25

Корректор М. Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Таймер | 1989 |

|

SU1656515A1 |

| Таймер | 1988 |

|

SU1531081A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Таймер | 1989 |

|

SU1626250A1 |

| Таймер | 1986 |

|

SU1357940A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1520599A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1381468A1 |

| Устройство для ввода-вывода информации | 1986 |

|

SU1429105A1 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных системах для обеспечения работы в реальном масштабе времени. Целью изобретения является расширение функциональных возможностей за счет обеспечения непрерывности работы таймера во время считывания с него информации. Это обусловлено тем, что тактовые импульсы таймера не запрещаются при наличии сигнала разрешения чте- ния. Поставленная цель достигается за счет введения триггеров 9, П, 15, элементов И.10, 12, 13, 16, элементов ИЛИ 14, 19. 1 ил.

| Таймер | 1981 |

|

SU1005010A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Таймер | 1983 |

|

SU1142822A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-15—Публикация

1986-01-14—Подача