Изобретение относится к вычислительной технике и может быть использовано для контроля оперативных запоминающих устройств в процессе их фу нк цио НИР ов ани я.

Цель изобретения - повышение достоверности контроля.

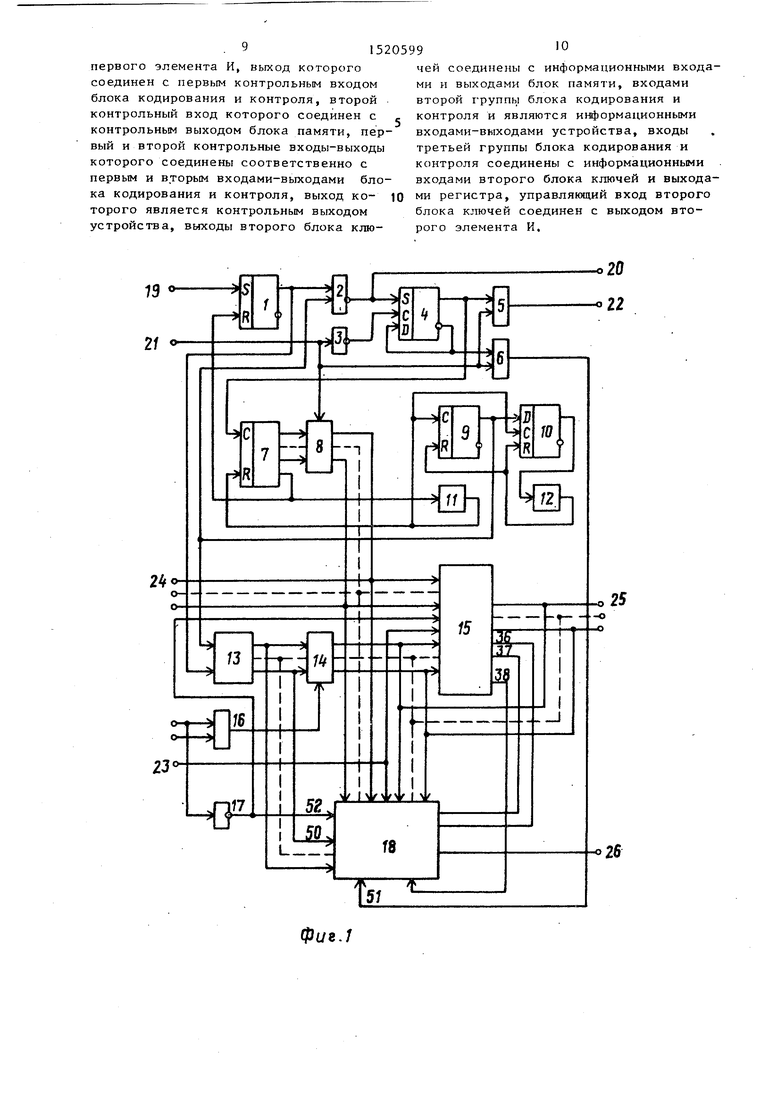

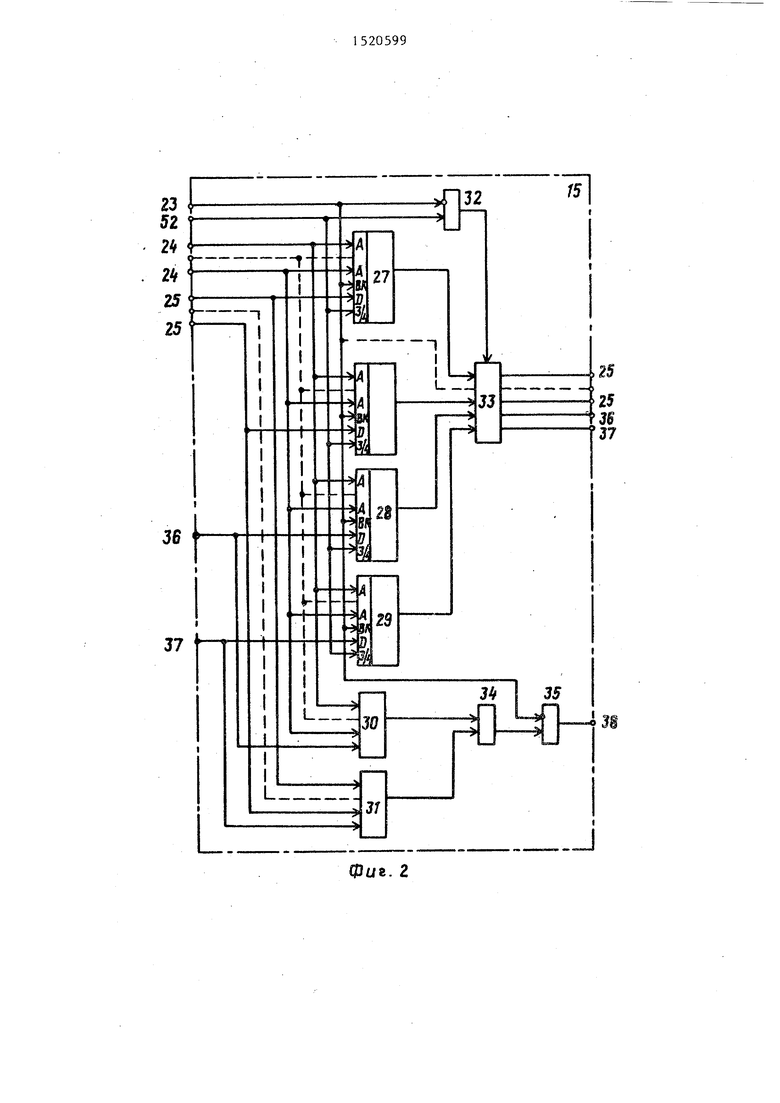

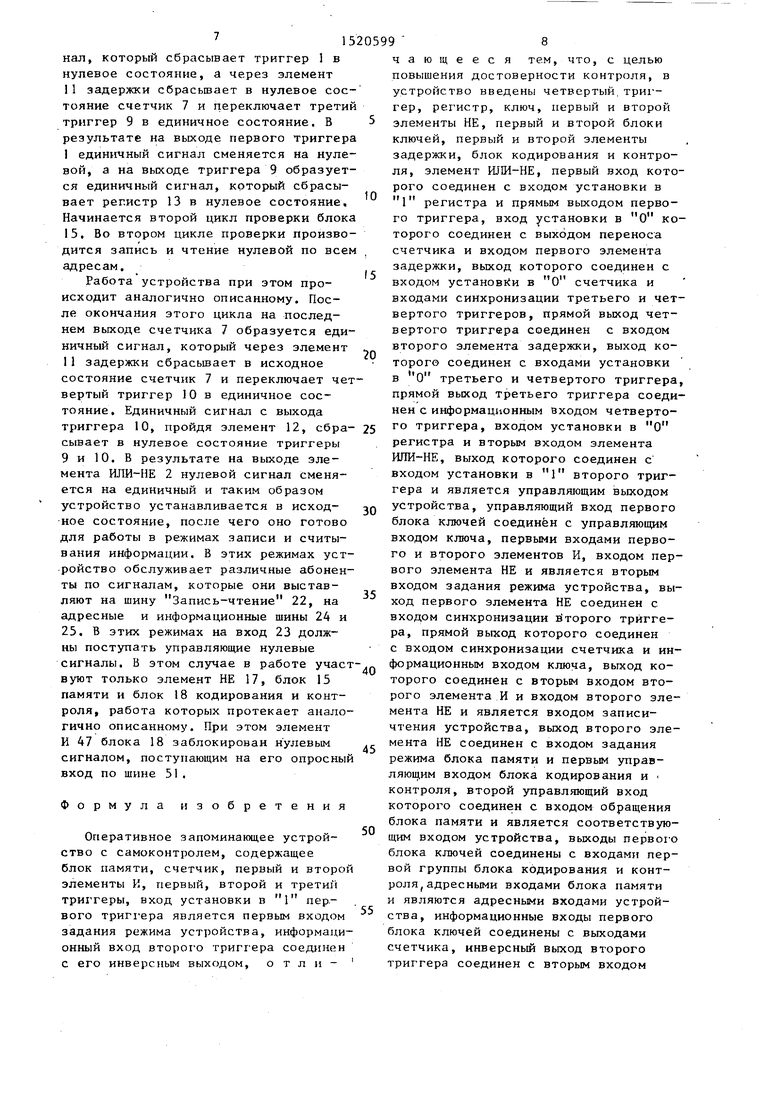

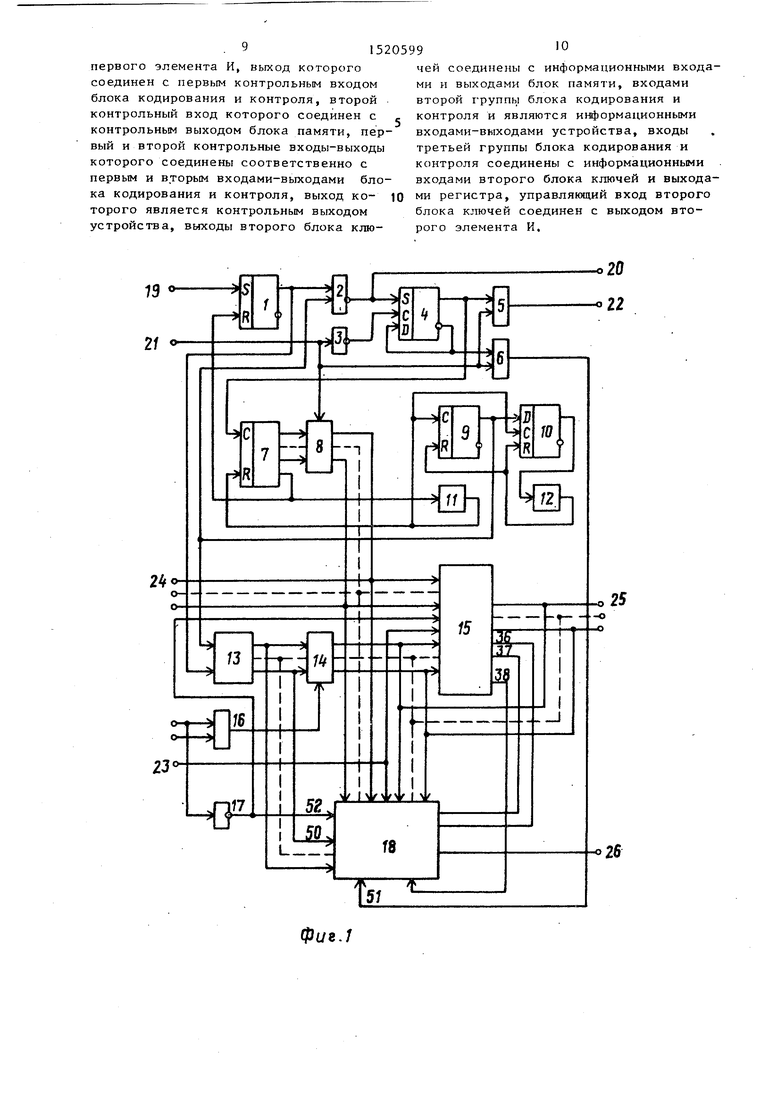

На фиг. 1 приведена функциональная схема оперативного запоминающего устройства с самоконтролем; на фиг. 2 - функциональная схема блока памяти;

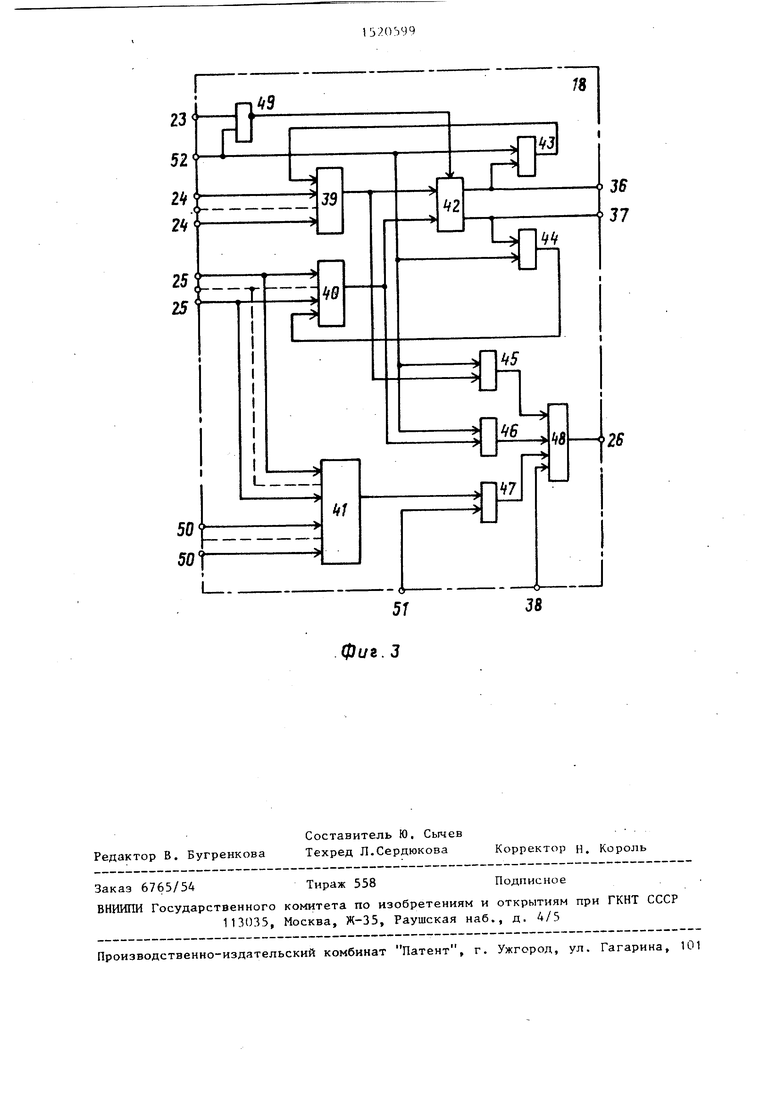

на фиг. 3 - функциональная схема блока кодирования и контроля.

Устройство содержит первый тригт гер 1, элемент ШШ-НЕ 2 ,первый элемент НЕ 3, второй триггер 4, ключ 5, первый элемент К 6, счетчик 7, первый блок ключей 8, третий триггер 9, четвертый триггер 10, элементы И и 12 задержки, регистр 13, второй блок 14 ключей, блок 15 памяти, второй элемент И 16, второй элемент НЕ 17, блок 18 кодиро

гюния и контроля, первый у1грар5ляш|цин вход 19, первый управляющий выход 20, второй управляющий вход 21, управляющую шину Запись-чтение 22, третий управляющий вход 23, адресные тины 24 информационные шины 25, контрольньй выход 26.

Блок 15 памяти содержит элементы 27-29 памяти, блоки 30 и 31 свертки по модулю два, первый элемент И 32, блок ключей 33, элемент ИЛИ 34, второ элемент. И, 35, первую контролыпую тину 36, вторую контрольную шину 37, контрольный выход 38.

Блок 18 кодирования и контроля содержит блоки 39 и 40 свертки по модулю два, схему 41 сравнения, блок 42 ключей, элементы И 43-47, элементы ИЛИ 48, элемент ИЛИ-НЕ 49, третью группу входов 50, контрольный 51 и управляющий 52 входы.

Устройство работает следующим образом.

В исходном состоянии все элемен- ты памяти устройства кроме триггера 4 находятся в нулевом состоянии (цепь начальной установки не показана). На выходе 20 присутствует единичный сигнал. На пгинах 22, 24, 25, 36 и 37 иг 1еется третье (разомкнутое) состояние. На остальных входах и выходах устройства действуют нулевые сигналы

Предлагаемое устройство может работать в трех режимах: в режиме проверки блока 15 памяти, в режиме запи- си информации и в режиме считывания информации по сигналам от внеиших абонентов.

При появлении ошибок происходит , проверка блока 15 памяти. В этом случае на управляющий вход 19 поступает сигнал в виде положительного импульса, который переключает триггер 1 в единичное состояние. Начинается первый цикл проверки блока 15 памяти. На выходе триггера 1 образуется единичный си1 Нс1л, который, воздействуя на вход установки в единицу регистра 13, устанавливает все его разряды в единичное состояние. Кроме того, в результате воздействия указанного сигнала на выходе элемента ИЛИ-НЕ 2 единичный си1 1 ал сменяется на нулев( и на первый управ.11як)щий выход 20 устройства коммутируется нулевой сигнал Этот нулевой сигнал осуществляет запрос нп разрешение использования блока 15 памяти. Одновременно пупр

0

5

5

- -

40

50

noi i сигнал, де 1 г1 яукиции ил ныходе 20, запре1ц чет работу ннетти-о: ябонент ов, KOTops.ie. не мог ут обращаться к данному блоку памяти до тех пор, пока не г1рои К1Йдет его проверка. Г ответ на указанный управляющий сигнлл запроса на управ;тяю1ций вход. 21 уст))ойства поступают единичные импульсы разрешения обращения к блоку 15. Эти импульсы поступают на управляющие входы блока ключей В и ключа 5, на первый вход элемента И 6 и через элемергт НЕ 3 - на С-вход второго триггера 4. Последний изменяет свое состояние по окончании каждого из этих импульсов, а после окончания очередных двух указанных импульсов триггер 4 заносит в счетчик 7 -i-l. При единичном состоянии триг гера 4 и наличии разрешающего сигнала на входе 21 на управляющую шину 22 через ключ 5 коммутируется единичный сигнал Запись-чтение (З/ч), а при нулевом состоянии триггера 4 и наличии разрешающего сигнала на входе 21 на шину 22 коммутируется нулевой,сигнал. В ответ на сигналы запросов по использован ™ данного блока памяти на управляющий вход 23 поступают нулевые сигналы, необходимые для работы блока 15 и блока 18 кодирования и контроля. При наличии на шинах 21 и 22 единичных сигналов, а на входе 23 нулевого сигнала происходит запись информации в блок 15. При наличии на пшне 2 единичного сигнала, а на шинах 22 и 23 нулевых сигналов происходит чтение информации из блока 15. Поскольку вначале счетчик 7 находится в нулевом состоянии, а на выходе элемента И 16 при записи образуется единичный сигнал, то на выходы первого блока ключей 8 коммутируется нулевой адресный код, а на выходы второго блока ключей 14 - единичный информационный код, В результате происходит запись единиц по нулевому адресу в элементы 27 памяти блока, 15. Количество элементов 27 памяти должно быть равно количеству информационных шин, по которым идет двусторонний обмен между блоком памяти и абонентами. После смены на шине 22 единичного сигнала на нулевой происходит чтение информации из элементов 27-29 памяти блока 15 но нулевому адресу. В этом случае на выходе элемента И 16 образуется нулевой сигнал, который запрещает работу

блока 14 ключей. Таким образом, при записи информации на управляющие входы ВК (выбор кристалла) и Запись- чтение элементов 27-29 памяти должны поступать нулевые сигналы, а при чтении информации на ВК должен быть нулевой сигнал, а на З/ч - единичный сигнал. Блок ключей 33 работает только при чтении информации. В этом случае на выходе элемента И 32 образуется единичный сигнал, который разрешает производить считывание информации на шины 25-27.

После обращений к блоку 13 по нулевому адресу в счетчик 7 запишется код адреса 00... 1, по которому ijpo- изойдет обращение к блоку 15 по описанному выше принципу. Таким образом, каждый раз после записи единиц по одному адресу производится считывание из блока памяти по этому же адресу и сравнение считанного с тем, что записьшалось. Это сравнение производится с помощью схемы 41 сравнения в блоке 18 кодирования и контроля и при несовпадении считанного шины 25) с тем, что записывалось (шины 50) на ее выходе образуется единичный сигнал ошибки, который через элемент К 47 и элемент Ш Ш 48 коммутируется на контрольный выход 26 устройства. При этом при чтении на выходе первогх) элемента И 6 образуются единичные импульсы, которые поступают на вход 51 блока 18 кодирования и контроля для опроса схемы 4 сравнения.

Блок 18 кодирования и койтроля осуществляет также кодирование и контроль адресных и информационнь х шин. Для кодирования по нечетности каждая адресная шина 24 подключена на соответствующий вход блока 39 свертки по модулю два. При четной сумме единиц на его входах на его выходе формируется логический О, а при нечетной сумме входных единиц на его выходе образуется логическая 1. Аналогично происходит кодироание информации по шинам 25 данных с помощью блока 40 свертки по модулю ва. Поскольку при записи информации на управляющих входах 23 и 52 присутствуют нулевые сигналы, то в этом лучае на выходе элементов ИЛИ-НЕ 9. образуется единичный сигнал, котоый и разрешит прохождение кодированных сигналов через блок ключей 42

o

5

0

5

на шины 36 и 37. Далее эти кодирова.н- ные сигналы поступают на D-входы элементов 28 и 29 памяти блока 15 и записываются в их ячейки в соответствии с адресными кодами, действующими на шинах 24.

Кроме того, блок 15 осуществляет контроль информации как при ее записи так и при ее чтении. Схема контроля включает в себя блоки 30 и 31 сверки по модулю два, элемент ИЛИ 34 и элемент И 35. С помощью блока 30 происходит контроль адресного кода, а с помощью блока 31 - контроль информационного кода. Эти блоки суммируют по модулю два адресные и информационные коды и сравнивают результат с контрольными разрядами 36 и 37. При наличии ошибок на выходе элемента ИЛИ 34 образуется единичный сигнал, который при наличии управляющего нулевого сигнала на входе 23 коммутируется через элемент И 35 на выход 38 и далее через элемент ИЛИ 48 в блоке 18 кодирования и контроля на контрольный выход 26 устройства.

Блок кодирования и контроля кроме описанных выше функций выполняет и 0 контроль по нечетн ости считанной из блока 15 информации. Этот контроль осуществляется на тех же блоках 39 и 40 сверток по модулю дв-а, с помощью которых происходит и кодирование ин- 5 формации. В этом случае на входе 52 присутствует единичный сигнал Чтение, а на выходе элемента ИПК-НЕ 49 - нулевой сигнал, из-за чего блок ключей 42 закрыт (на его выходе тре- 0 тье состояние). В то же время блок . ключей ЗЭ1 в блоке 15 открыт, вслед- ствие чего на информационных 25 и контрольных шинах 36 и 37 появляются информационные и контрольные сигналы 5 Контрольные сигналы через элементы И 43 и 44 поступают на соответствующие (опросные) входы блоков 39 и 40 сверток по модулю два, где происходит их сравнение с адресным и информаци- 0 -онным кодами, присутствующими на шинах 24 и 25, В случае ошибок на выходах блоков 39 и 40 образуются единичные сигналы, которые через элементы И 45 и 46 и элемент ИЛИ 48 комму- 5 тируются на контрольный выход 26 устройства.

После записи-чтения единиц по всем адресам блока 15 на выходе переноса счетчика 7 появляется единичный CHI-

нал, который сбрасывает триггер 1 в нулевое состояние, а через элемент 11 задержки сбрасывает в нулевое соетояние счетчик 7 и переключает третий триггер 9 в единичное состояние. В результате на выходе первого триггера

Iединичный сигнал сменяется на нулевой, а на выходе триггера 9 образуется единичный сигнал, который сбрасывает регистр 13 в нулевое состояние. Начинается второй цикл проверки блока 15. Во втором цикле проверки производится запись и чтение нулевой по всем адресам.

Работа устройства при этом происходит аналогично описанному. После окончания этого цикла на последнем выходе счетчика 7 образуется единичный сигнал, который через элемент

I1задержки сбрасьшает в исходное состояние счетчик 7 и переключает четвертый триггер 10 в единичное состояние. Единичный сигнал с выхода триггера 10, пройдя элемент 12, сбра- сывает в нулевое состояние триггеры

9 и 10. В результате на выходе элемента ИЛИ-НЕ 2 нулевой сигнал сменяется на единичный и таким образом устройство устанавливается в исходное состояние, после чего оно готово для работы в режимах записи и считывания информации. В этих режимах устройство обслуживает различные абоненты по сигналам, которые они выставляют на шину Запись-чтение 22, на адресные и информационные шины 24 и 25. В этих режимах на вход 23 должны поступать управляющие нулевые сигналы. В этом случае в работе участвуют только элемент НЕ 17, блок 15 памяти и блок 18 кодирования и контроля, работа которых протекает аналогично описанному. При этом элемент И 47 блока 18 заблокирован нулевым сигналом, поступающим на его опросный вход по шине 51.

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее блок памяти, счетчик, первый и второй элементы И, первый, второй и третий триггеры, вход установки в 1 первого триггера является первым входом задания режима устройства, информационный вход второго триггера соединен с его инверсным выходом, о т л и -

0

5

0

5

0

5

0

5

0

5

чающееся тем, что, с целью повышения достоверности контроля, в устройство введены четвертый, трих-- гер, регистр, ключ, первый и второй элементы НЕ, первый и второй блоки ключей, первый и второй элементы задержки, блок кодирования и контроля, элемент ИЛИ-НЕ, первый вход которого соединен с входом установки в 1 регистра и прямым выходом первого триггера, вход установки в О которого соединен с выходом переноса счетчика и входом первого элемента задержки, выход которого соединен с входом установки в О счетчика и входами синхронизации третьего и четвертого триггеров, прямой выход четвертого триггера соединен с входом второго элемента задержки, выход которого соединен с входами установки в о третьего и четвертого триггера, прямой выход третьего триггера соединен с информационным входом четвертого триггера, входом установки в О регистра и вторым входом элемента ИЛИ-НЕ, выход которого соединен с входом установки в 1 второго триггера и является управляющим выходом устройства, управляющий вход первого блока ключей соединён с управляющим входом ключа, первыми входами первого и второго элементов И, входом первого элемента НЕ и является вторым входом задания режима устройства, выход первого элемента НЕ соединен с входом синхронизации йторого триггера, прямой выход которого соединен с входом синхронизации счетчика и информационным входом ключа, выход которого соединен с вторым входом второго элемента И и входом второго элемента НЕ и является входом записи- чтения устройства, выход второго элемента НЕ соединен с входом задания режима блока памяти и первым управляющим входом блока кодирования и контроля, второй управляющий вход которого соединен с входом обращения блока памяти и является соответствующим входом устройства, выходы первого блока ключей соединены с входами первой группы блока кодирования и контроля, адресными входами блока памяти и являются адресными входами устройства, информационные входы первого блока ключей соединены с выходами счетчика, инверсный выход второго триггера соединен с вторым входом

первого элемента И, вьгход которого соединен с первым контрольным входом блока кодирования и контроля, второй контрольный вход которого соединен с контрольным выходом блока памяти, первый и второй контрольные входы-выходы которого соединены соответственно с первым и вторым входами-выходами блока кодирования и контроля, выход ко- торого является контрольным выходом устройства, выходы второго блока ключей соединены с информационными входами и выходами блок памяти, входами второй группы блока кодирования и контроля и являются информационными входами-выходами устройства, входы третьей группы блока кодирования и контроля соединены с информационными входами второго блока ключей и выходами регистра, управляющий вход второго блока ключей соединен с выходом второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации | 1986 |

|

SU1429105A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Устройство для контроля трассировки и воспроизведения информации о прокладке кабельной трассы | 1984 |

|

SU1238106A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ НЕИСПРАВНОСТЕЙ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1992 |

|

RU2030784C1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения состоит в повышении достоверности контроля. Устройство содержит четыре триггера, элемент ИЛИ-НЕ, два элемента НЕ, ключ, два элемента И, счетчик, два блока ключей, два элемента задержки, регистр, блок ОЗУ и блок кодирования и контроля. Устройство позволяет производить контроль ОЗУ контрольными кодами. Этот контроль осуществляется в два цикла. В первом цикле по каждому адресу ОЗУ происходит запись "1" по всем разрядам. Причем каждый раз после записи "1" по одному адресу производится считывание из ОЗУ по этому же адресу и сравнение с тем, что записывалось, и при несовпадении считанного с тем, что записывалось, вырабатывается сигнал ошибки. Во втором цикле производится запись и чтение "О" с последующим сравнением по тем же адресам. Кроме того, производится кодирование адресных и информационных кодов с последующим контролем их прохождения по соответствующим шинам и контролем хранимой информации. По окончании указанных проверок начинается работа по обслуживанию внешних абонентов по сигналам, которые они выставляют на общие шины. В этом случае каждый из абонентов, получив разрешение от ЭВМ, может произвести запись или считывание информации. 3 ил.

Фиг.

Фиг. 2

| Устройство для контроля блоков памяти | 1984 |

|

SU1226533A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1140180A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| i | |||

Авторы

Даты

1989-11-07—Публикация

1988-04-06—Подача