Изобретение относится к измерительной и вычислительной технике, устройствам запоминания и может быть использовано как совместно, при построении высокопроизводительных систем сбора и обработки аналоговых данных с использованием мультиплицированной структуры и ЭВМ, так и отдельно, при построении многоканальных систем и буферных накопителей.

Цель изобретения -- повышение быстродействия многоканального устройства для ввода аналоговых данных за счет организации параллельной записи информации в несколько ячеек памяти.

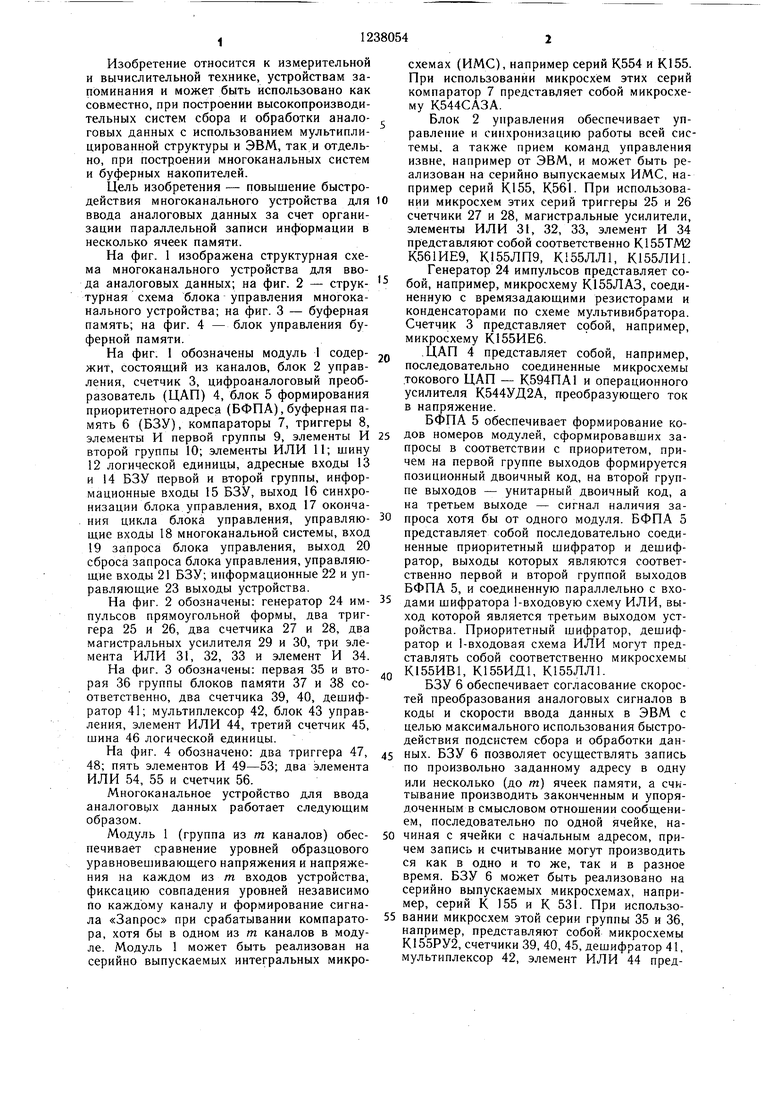

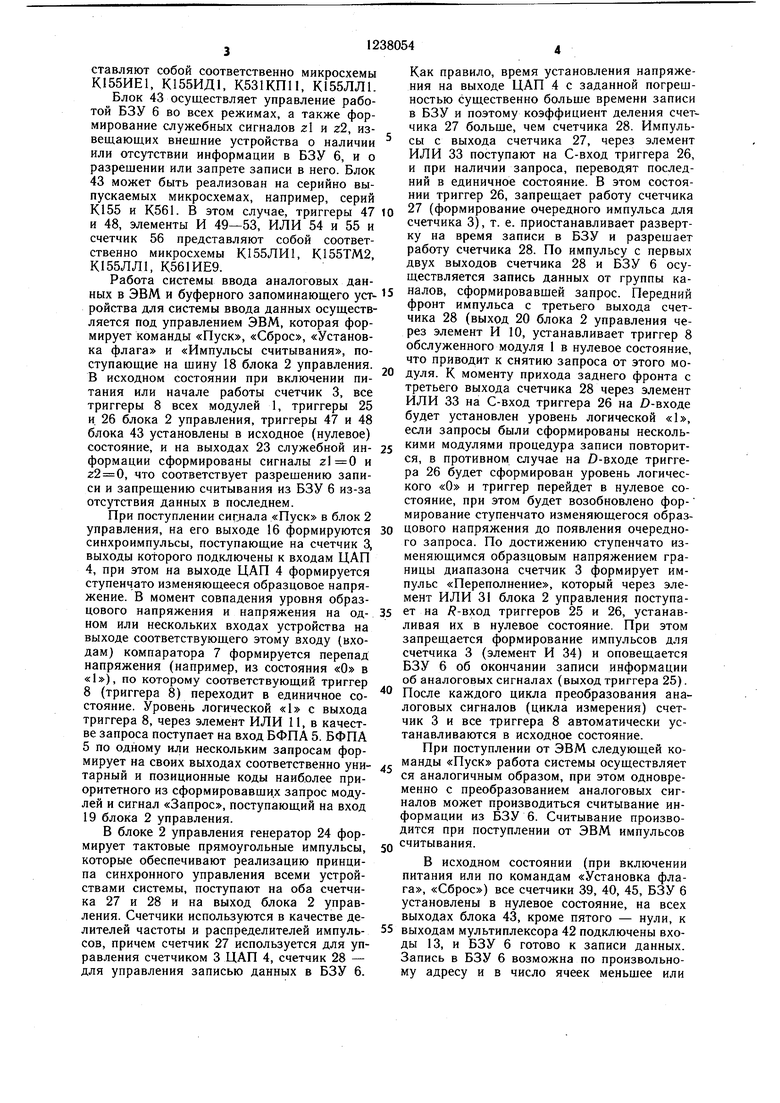

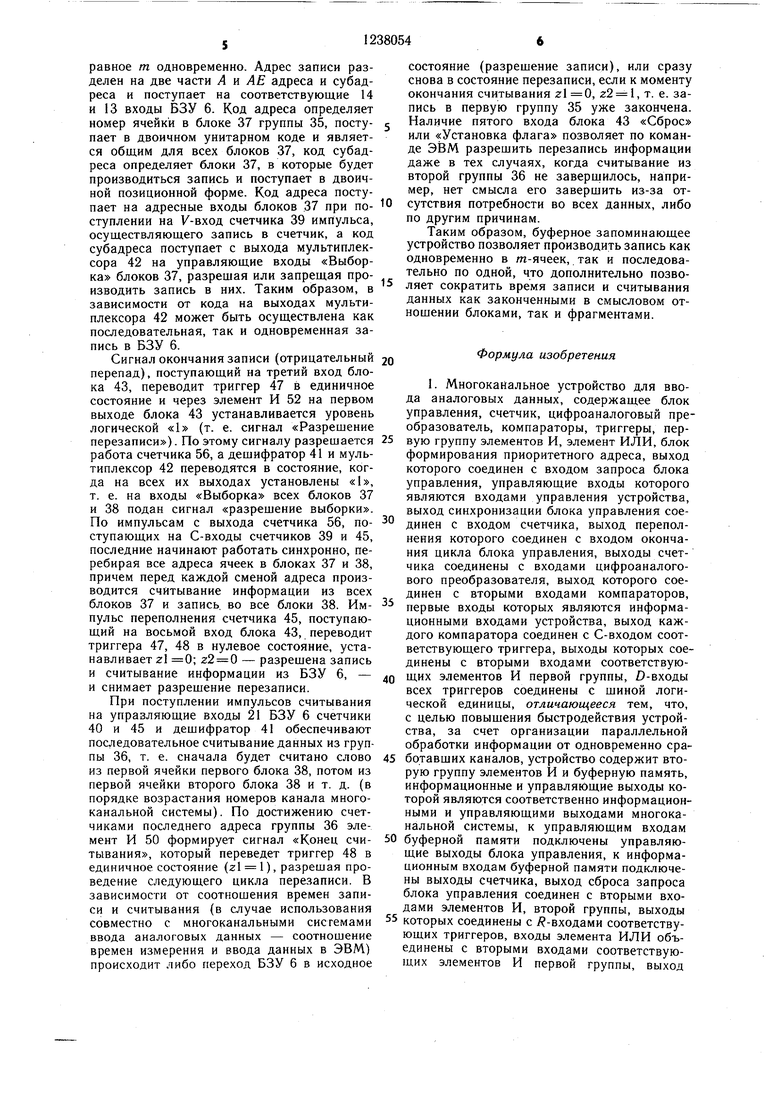

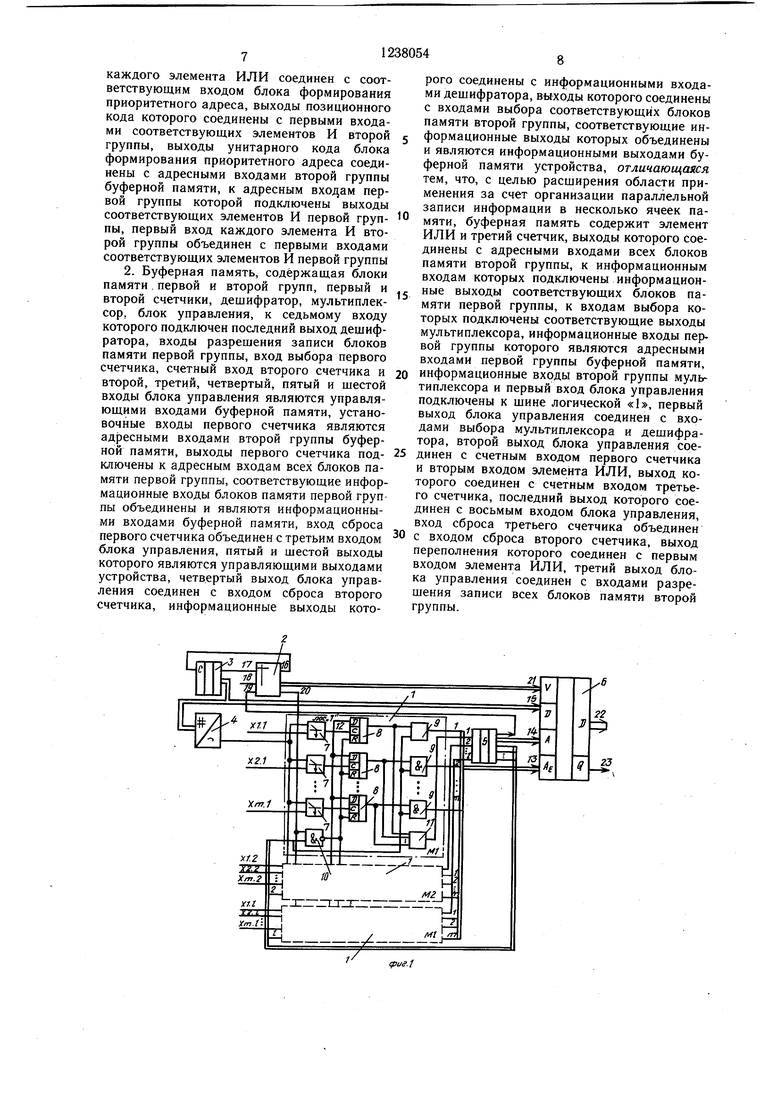

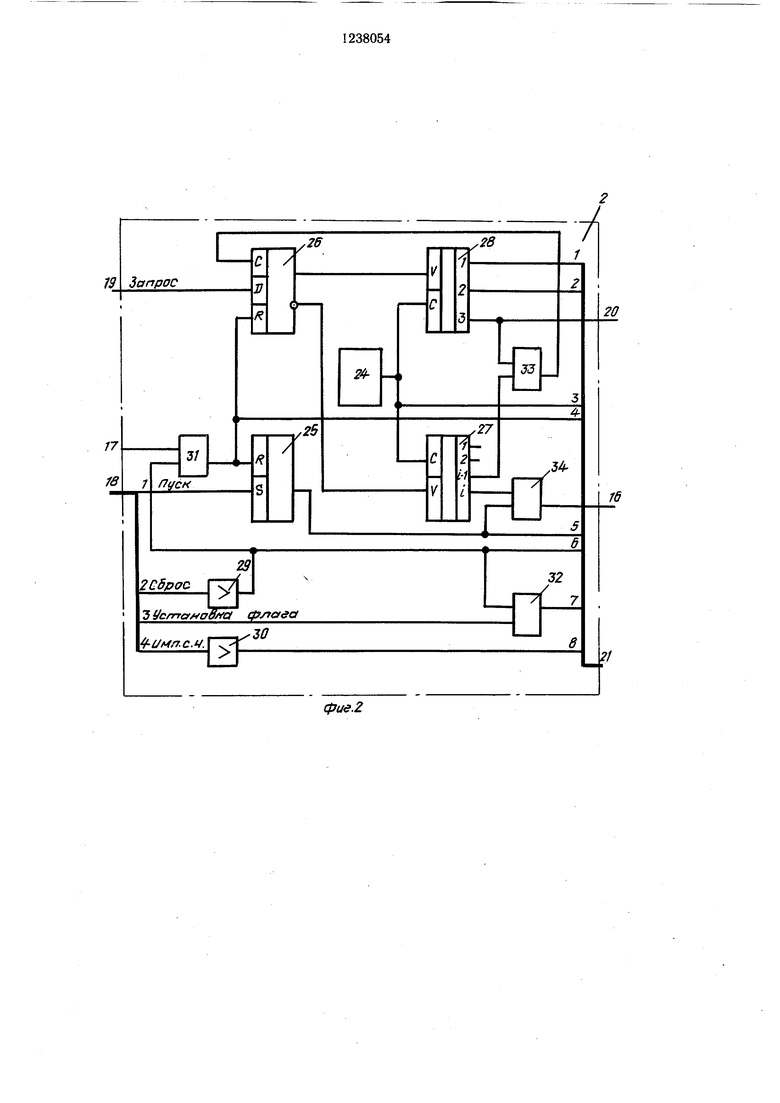

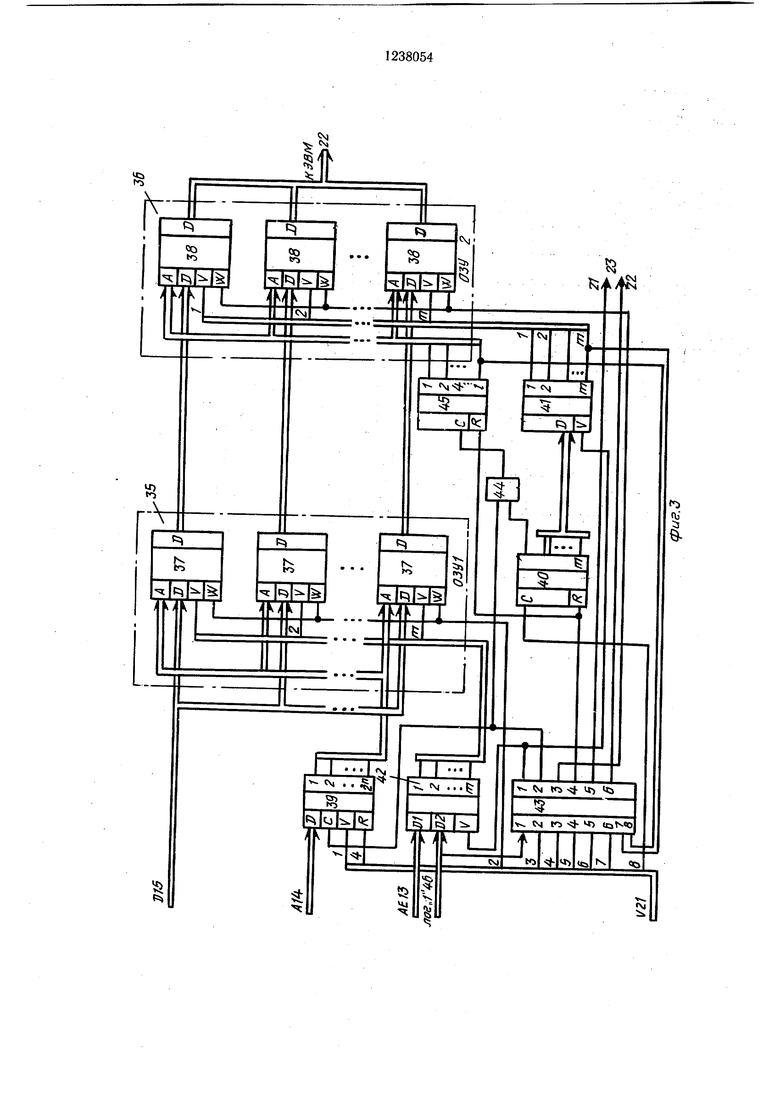

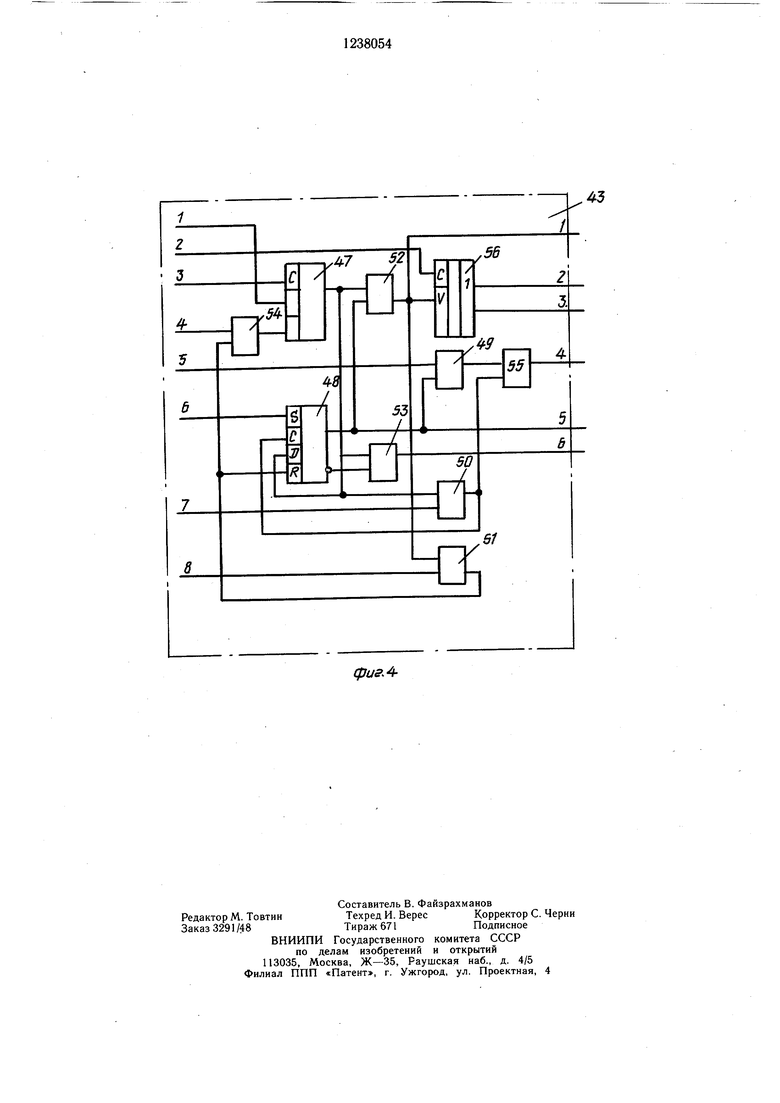

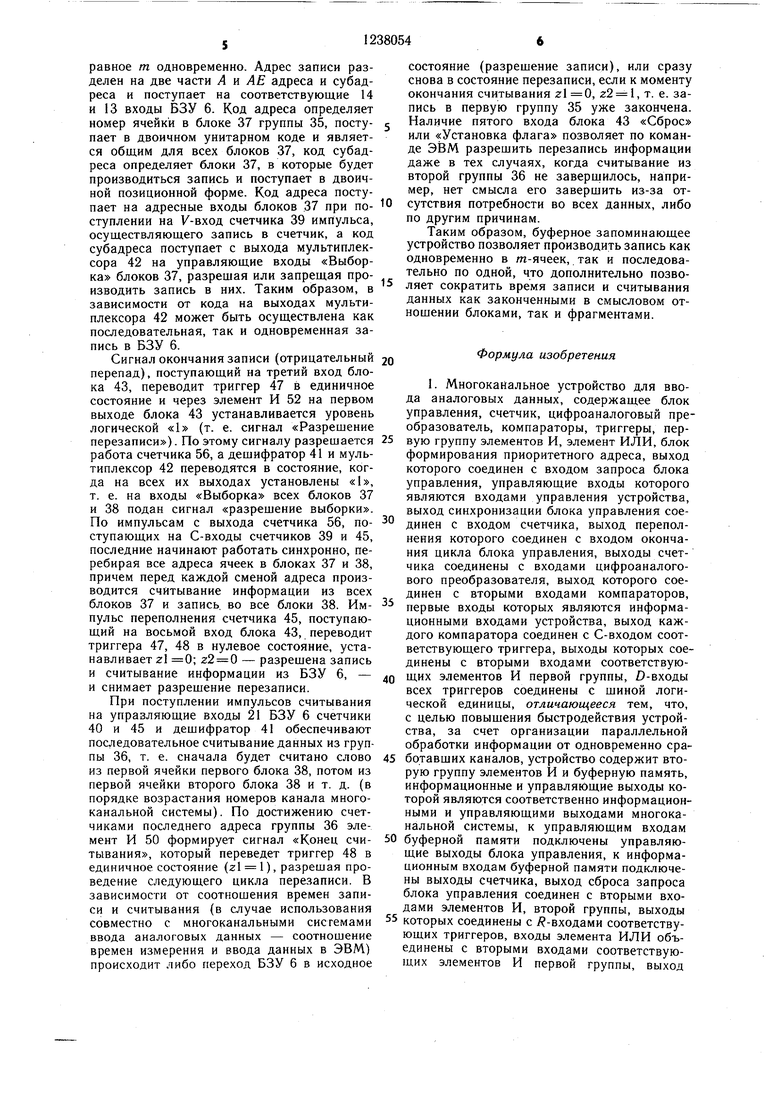

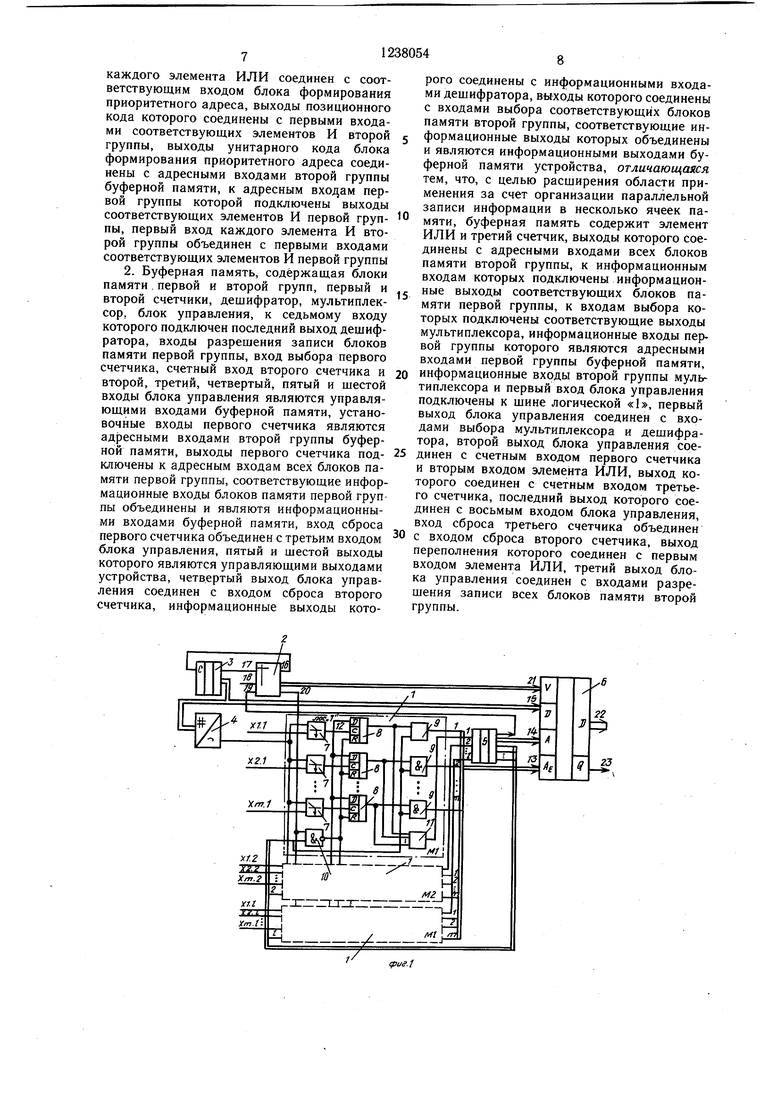

На фиг. 1 изображена структурная схема многоканального устройства для ввода аналоговых данных; на фиг. 2 - структурная схема блока управления многоканального устройства; на фиг. 3 - буферная память; на фиг. 4 - блок управления буферной памяти.

На фиг. 1 обозначены модуль 1 содержит, состоящий из каналов, блок 2 управления, счетчик 3, цифроаналоговый преобразователь (ЦАП) 4, блок 5 формирования приоритетного адреса (БФПА), буферная память 6 (БЗУ), компараторы 7, триггеры 8, элементы И первой группы 9, элементы И второй группы 10; элементы ИЛИ 11; шину 12 логической единицы, адресные входы 13 и 14 БЗУ первой и второй группы, информационные входы 15 БЗУ, выход 16 синхронизации блока управления, вход 17 окончания цикла блока управления, управляющие входы 18 многоканальной системы, вход 19 запроса блока управления, выход 20 сброса запроса блока управления, управляющие входы 21 БЗУ; информационные 22 и управляющие 23 выходы устройства.

На фиг. 2 обозначены: генератор 24 импульсов прямоугольной формы, два триггера 25 и 26, два счетчика 27 и 28, два магистральных усилителя 29 и 30, три элемента ИЛИ 31, 32, 33 и элемент И 34.

На фиг. 3 обозначены: первая 35 и вторая 36 группы блоков памяти 37 и 38 соответственно, два счетчика 39, 40, дещиф- ратор 41; мультиплексор 42, блок 43 управления, элемент ИЛИ 44, третий счетчик 45, шина 46 логической единицы.

На фиг. 4 обозначено: два триггера 47, 48; пять элементов И 49-53; два элемента ИЛИ 54, 55 и счетчик 56.

Многоканальное устройство для ввода аналоговых данных работает следующим образом.

Модуль 1 (группа из т каналов) обеспечивает сравнение уровней образцового уравновешивающего напряжения и напряжения на каждом из т входов устройства, фиксацию совпадения уровней независимо По каждому каналу и формирование сигнала «Запрос при срабатывании компаратора, хотя бы в одном из т каналов в модуле. Модуль 1 может быть реализован на серийно выпускаемых интегральных микросхемах (ИМС), например серий К554 и К155. При использовании микросхем этих серий компаратор 7 представляет собой микросхему К544САЗА.

Блок 2 управления обеспечивает управление и синхронизацию работы всей системы, а также прием команд управления извне, например от ЭВМ, и может быть реализован на серийно выпускаемых ИМС, например серий К155, К561. При использова- НИИ микросхем этих серий триггеры 25 и 26 счетчики 27 и 28, магистральные усилители, элементы ИЛИ 31, 32, 33, элемент И 34 представляют собой соответственно К155ТМ2 К561ИЕ9, К155ЛП9, К155ЛЛ1, К155ЛИ1. Генератор 24 импульсов представляет со- бой, например, микросхему К155ЛАЗ, соединенную с времязадающими резисторами и конденсаторами по схеме мультивибратора. Счетчик 3 представляет собой, например, микросхему К155ИЕ6.

0 .ЦАП 4 представляет собой, например, последовательно соединенные микросхемы токового ЦАП - К594ПА1 и операционного усилителя К544УД2А, преобразующего ток в напряжение.

БФПА 5 обеспечивает формирование ко- 5 дов номеров модулей, сформировавших запросы в соответствии с приоритетом, причем на первой группе выходов формируется позиционный двоичный код, на второй группе выходов - унитарный двоичный код, а на третьем выходе - сигнал наличия за- 0 проса хотя бы от одного модуля. БФПА 5 представляет собой последовательно соединенные приоритетный шифратор и дещиф- ратор, выходы которых являются соответственно первой и второй группой выходов БФПА 5, и соединенную параллельно с вхо- 5 дами шифратора 1-входовую схему ИЛИ, выход которой является третьим выходом устройства. Приоритетный шифратор, дешифратор и -входовая схема ИЛИ могут представлять собой соответственно микросхемы 0 К155ИВ1, К155ИД1, К155ЛЛ1.

БЗУ 6 обеспечивает согласование скоростей преобразования аналоговых сигналов в коды и скорости ввода данных в ЭВМ с целью максимального использования быстродействия подсистем сбора и обработки дан- 5 ных. БЗУ 6 позволяет осуществлять запись по произвольно заданному адресу в одну

или несколько (до т} ячеек памяти, а считывание производить законченным и упорядоченным в смысловом отношении сообщением, последовательно по одной ячейке, на50 чиная с ячейки с начальным адресом, причем запись и считывание могут производить ся как в одно и то же, так и в разное время. БЗУ 6 может быть реализовано на серийно выпускаемых микросхемах, например, серий К 155 и К 531. При использо55 вании микросхем этой серии группы 35 и 36, например, представляют собой микросхемь К155РУ2, счетчики 39, 40, 45, дешифратор 41, мультиплексор 42, элемент ИЛИ 44 представляют собой соответственно микросхемы К155ИЕ1, К155ИД1, К531КП11, К155ЛЛ1.

Блок 43 осуществляет управление работой БЗУ 6 во всех режимах, а также формирование служебных сигналов zl и 22, извещающих внещние устройства о наличии или отсутствии информации в БЗУ 6, и о разрешении или запрете записи в него. Блок 43 может быть реализован на серийно выпускаемых микросхемах, например, серий К155 и К561. В этом случае, триггеры 47 и 48, элементы И 49-53, ИЛИ 54 и 55 и счетчик 56 представляют собой соответственно микросхемы К155ЛИ1, К155ТМ2, К155ЛЛ1, К561ИЕ9.

Работа системы ввода аналоговых данных в ЭВМ и буферного запоминающего уст- ройства для системы ввода данных осуществляется под управлением ЭВМ, которая формирует команды «Пуск, «Сброс, «Установка флага и «Импульсы считывания, поступающие на щину 18 блока 2 управления. В исходном состоянии при включении питания или начале работы счетчик 3, все триггеры 8 всех модулей 1, триггеры 25 и. 26 блока 2 управления, триггеры 47 и 48 блока 43 установлены в исходное (нулевое) состояние, и на выходах 23 служебной ин- формации сформированы сигналы и г2 0, что соответствует разрешению записи и запрещению считывания из БЗУ 6 из-за отсутствия данных в последнем.

При поступлении сигнала «Пуск в блок 2 управления, на его выходе 16 формируются синхроимпульсы, поступающие на счетчик 3, выходы которого подключены к входам ЦАП 4, при этом на выходе ЦАП 4 формируется ступенчато изменяющееся образцовое напряжение. В момент совпадения уровня образцового напряжения и напряжения на од- ном или нескольких входах устройства на выходе соответствующего этому входу (входам) компаратора 7 формируется перепад напряжения (например, из состояния «О в «1), по которому соответствующий триггер 8 (триггера 8) переходит в единичное состояние. Уровень логической «1 с выхода триггера 8, через элемент ИЛИ 11, в качестве запроса поступает на вход БФПА 5. БФПА 5 по одному или нескольким запросам формирует на своих выходах соответственно уни- тарный и позиционные коды наиболее приоритетного из сформировавших запрос модулей и сигнал «Запрос, поступающий на вход 19 блока 2 управления.

В блоке 2 управления генератор 24 формирует тактовые прямоугольные импульсы, которые обеспечивают реализацию принципа синхронного управления всеми устройствами системы, поступают на оба счетчика 27 и 28 и на выход блока 2 управления. Счетчики используются в качестве делителей частоты и распределителей импуль- сов, причем счетчик 27 используется для управления счетчиком 3 ЦАП 4, счетчик 28 - для управления записью данных в БЗУ 6.

Как правило, время установления напряжения на выходе ЦАП 4 с заданной погрешностью существенно больше времени записи в БЗУ и поэтому коэффициент деления счетчика 27 больше, чем счетчика 28. Импульсы с выхода счетчика 27, через элемент ИЛИ 33 поступают на С-вход триггера 26, и при наличии запроса, переводят последний в единичное состояние. В этом состоянии триггер 26, запрещает работу счетчика 27 (формирование очередного импульса для счетчика 3), т. е. приостанавливает развертку на время записи в БЗУ и разрешает работу счетчика 28. По импульсу с первых двух выходов счетчика 28 и БЗУ 6 осуществляется запись данных от группы каналов, сформировавшей запрос. Передний фронт импульса с третьего выхода счетчика 28 (выход 20 блока 2 управления через элемент И 10, устанавливает триггер 8 обслуженного модуля 1 в нулевое состояние, что приводит к снятию запроса от этого модуля. К моменту прихода заднего фронта с третьего выхода счетчика 28 через элемент ИЛИ 33 на С-вход триггера 26 на Д-входе будет установлен уровень логической «1, если запросы были сформированы несколькими модулями процедура записи повторится, в противном случае на )-входе триггера 26 будет сформирован уровень логического «О и триггер перейдет в нулевое состояние, при этом будет возобновлено фор- мирование ступенчато изменяющегося образцового напряжения до появления очередного запроса. По достижению ступенчато изменяющимся образцовым напряжением границы диапазона счетчик 3 формирует импульс «Переполнение, который через элемент ИЛИ 31 блока 2 управления поступает на / -вход триггеров 25 и 26, устанавливая их в нулевое состояние. При этом запрещается формирование импульсов для счетчика 3 (элемент И 34) и оповещается БЗУ 6 об окончании записи информации об аналоговых сигналах (выход триггера 25). После каждого цикла преобразования аналоговых сигналов (цикла измерения) счетчик 3 и все триггера 8 автоматически устанавливаются в исходное состояние.

При поступлении от ЭВМ следующей команды «Пуск работа системы осуществляет ся аналогичным образом, при этом одновременно с преобразованием аналоговых сигналов может производиться считывание информации из БЗУ 6. Считывание производится при поступлении от ЭВМ импульсов считывания.

В исходном состоянии (при включении питания или по командам «Установка флага, «Сброс) все счетчики 39, 40, 45, БЗУ 6 установлены в нулевое состояние, на всех выходах блока 43, кроме пятого - нули, к выходам мультиплексора 42 подключены входы 13, и БЗУ 6 готово к записи данных. Запись в БЗУ 6 возможна по произвольному адресу и в число ячеек меньшее или

равное т одновременно. Адрес записи разделен на две части А и АЕ адреса и субадреса и поступает на соответствующие 14 и 13 входы БЗУ 6. Код адреса определяет номер ячейки в блоке 37 группы 35, поступает в двоичном унитарном коде и является общим для всех блоков 37, код субадреса определяет блоки 37, в которые будет производиться запись и поступает в двоичной позиционной форме. Код адреса поступает на адресные входы блоков 37 при поступлении на У-вход счетчика 39 импульса, осуществляющего запись в счетчик, а код субадреса поступает с выхода мультиплексора 42 на управляющие входы «Выборка блоков 37, разрешая или запрещая производить запись в них. Таким образом, в зависимости от кода на выходах мультиплексора 42 может быть осуществлена как последовательная, так и одновременная запись в БЗУ 6.

Сигнал окончания записи (отрицательный перепад), поступающий на третий вход блока 43, переводит триггер 47 в единичное состояние и через элемент И 52 на первом выходе блока 43 устанавливается уровень логической «1 (т. е. сигнал «Разрещение перезаписи). Поэтому сигналу разрешается работа счетчика 56, а дешифратор 41 и мультиплексор 42 переводятся в состояние, когда на всех их выходах установлены «1, т. е. на входы «Выборка всех блоков 37 и 38 подан сигнал «разрешение выборки. По импульсам с выхода счетчика 56, поступающих на С-входы счетчиков 39 и 45, последние начинают работать синхронно, перебирая все адреса ячеек в блоках 37 и 38, причем перед каждой сменой адреса производится считывание информации из всех блоков 37 и запись, во все блоки 38. Импульс переполнения счетчика 45, поступающий на восьмой вход блока 43, переводит триггера 47, 48 в нулевое состояние, устанавливает z 0; z2 0 - разрешена запись и считывание информации из БЗУ 6, - и снимает разрешение перезаписи.

При поступлении импульсов считывания на управляющие входы 21 БЗУ 6 счетчики 40 и 45 и дешифратор 41 обеспечивают последовательное считывание данных из группы 36, т. е. сначала будет считано слово из первой ячейки первого блока 38, потом из первой ячейки второго блока 38 и т. д. (в порядке возрастания номеров канала многоканальной системы). По достижению счетчиками последнего адреса группы 36 элемент И 50 формирует сигнал «Конец считывания, который переведет триггер 48 в единичное состояние (г 1), разрешая проведение следующего цикла перезаписи. В зависимости от соотношения времен записи и считывания (в случае использования совместно с многоканальными системами ввода аналоговых данных - соотношение времен измерения и ввода данных в ЭВМ) происходит либо переход БЗУ 6 в исходное

состояние (разрешение записи), или сразу снова в состояние перезаписи, если к моменту окончания считывания г О, 22 1, т. е. запись в первую группу 35 уже закончена.

Наличие пятого входа блока 43 «Сброс или «Установка флага позволяет по команде ЭВМ разрешить перезапись информации даже в тех случаях, когда считывание из второй группы 36 не завершилось, например, нет смысла его завершить из-за отсутствия потребности во всех данных, либо по другим причинам.

Таким образом, буферное запоминающее устройство позволяет производить запись как одновременно в /п-ячеек, так и последовательно по одной, что дополнительно позволяет сократить время записи и считывания данных как законченными в смысловом отношении блоками, так и фрагментами.

20

Формула изобретения

0

1. Многоканальное устройство для ввода аналоговых данных, содержащее блок управления, счетчик, цифроаналоговый преобразователь, компараторы, триггеры, первую группу элементов И, элемент ИЛИ, блок формирования приоритетного адреса, выход которого соединен с входом запроса блока управления, управляющие входы которого являются входами управления устройства, выход синхронизации блока управления соединен с входом счетчика, выход переполнения которого соединен с входом окончания цикла блока управления, выходы счетчика соединены с входами цифроаналого- вого преобразователя, выход которого соединен с вторыми входами компараторов, первые входы которых являются информационными входами устройства, выход каждого компаратора соединен с С-входом соответствующего триггера, выходы которых соединены с вторыми входами соответствую0 щих элементов И первой группы, D-входы всех триггеров соединены с шиной логической единицы, отличающееся тем, что, с целью повыщения быстродействия устройства, за счет организации параллельной обработки информации от одновременно ера5 ботавщих каналов, устройство содержит вторую группу элементов И и буферную память, информационные и управляющие выходы которой являются соответственно информационными и управляющими выходами многоканальной системы, к управляющим входам

0 буферной памяти подключены управляющие выходы блока управления, к информационным входам буферной памяти подключены выходы счетчика, выход сброса запроса блока управления соединен с вторыми входами элементов И, второй группы, выходы

5 которых соединены с / -входами соответствующих триггеров, входы элемента ИЛИ объединены с вторыми входами соответствующих элементов И первой группы, выход

каждого элемента ИЛИ соединен с соответствующим входом блока формирования приоритетного адреса, выходы позиционного кода которого соединены с первыми входами соответствующих элементов И второй группы, выходы унитарного кода блока формирования приоритетного адреса соединены с адресными входами второй группы буферной памяти, к адресным входам первой группы которой подключены выходы соответствующих элементов И первой группы, первый вход каждого элемента И второй группы объединен с первыми входами соответствующих элементов И первой группы 2. Буферная память, содержащая блоки памяти.первой и второй групп, первый и второй счетчики, дешифратор, мультиплексор, блок управления, к седьмому входу которого подключен последний выход дещиф- ратора, входы разрешения записи блоков памяти первой группы, вход выбора первого счетчика, счетный вход второго счетчика и второй, третий, четвертый, пятый и шестой входы блока управления являются управляющими входами буферной памяти, установочные входы первого счетчика являются адресными входами второй группы буферной памяти, выходы первого счетчика подключены к адресным входам всех блоков памяти первой группы, соответствующие информационные входы блоков памяти первой группы объединены и являютя информационными входами буферной памяти, вход сброса первого счетчика объединен с третьим входом блока управления, пятый и шестой выходы которого являются управляющими выходами устройства, четвертый выход блока управления соединен с входом сброса второго счетчика, информационные выходы кото

рого соединены с информационными входами дешифратора, выходы которого соединены с входами выбора соответствующих блоков памяти второй группы, соответствующие информационные выходы которых объединены и являются информационными выходами буферной памяти устройства, отличающаяся тем, что, с целью расширения области применения за счет организации параллельной записи информации в несколько ячеек памяти, буферная память содержит элемент ИЛИ и третий счетчик, выходы которого соединены с адресными входами всех блоков памяти второй группы, к информационным входам которых подключены информацион- с ные выходы соответствующих блоков памяти первой группы, к входам выбора которых подключены соответствующие выходы мультиплексора, информационные входы первой группы которого являются адресными входами первой группы буферной памяти, 0 информационные входы второй группы мультиплексора и первый вход блока управления подключены к шине логической «I, первый выход блока управления соединен с входами выбора мультиплексора и дешифратора, второй выход блока управления сое- 5 динен с счетным входом первого счетчика и вторым входом элемента ИЛИ, выход которого соединен с счетным входом третьего счетчика, последний выход которого соединен с восьмым входом блока управления, вход сброса третьего счетчика объединен 0 с входом сброса второго счетчика, выход переполнения которого соединен с первым входом элемента ИЛИ, третий выход блока управления соединен с входами разрешения записи всех блоков памяти второй группы.

(puS-1

фиг.А

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Многоканальное устройство для ввода аналоговых данных | 1985 |

|

SU1273911A1 |

| Устройство для многоканальной регистрации сейсмических сигналов | 1988 |

|

SU1509773A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583980A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

Изобретение относится к измерительной и вычислительной технике и может быть ис-пользовано в высокопроизводительных системах сбора и обработки аналоговых данных. Цель изобретения - повышение быстродействия многоканального устройства для ввода аналоговых данных и расширение области применения буферной памяти. Введение в многоканальное устройство буферной памяти, имеющей дополнительные адресные входы, позволяет организовать параллельную обработку информации от одновременно сработавших каналов преобразования данных. Буферная память содержит два ОЗУ ряд управляющих блоков и может работать в трех режимах; одновременное занесение информации от нескольких сработавших каналов в первое ОЗУ, перезапись информации из первого ОЗУ во второе, считывание информации из второго ОЗУ. 2 с. п. ф-лы, sg 4 ил. (/ IN:) оо 00 сд

| Устройство для ввода информации о параметрах объекта в электронную вычислительную машину | 1975 |

|

SU526882A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальная система ввода аналоговой информации | 1973 |

|

SU450157A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Буферное запоминающее устройство | 1980 |

|

SU942139A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-06-15—Публикация

1984-07-06—Подача