Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных ЭВМ, имеющих систему виртуальной или многоуровневой памяти, для построения сверхоперативного запоминающего устройства (СОЗУ).

Цель изобретения - повыщение надежности сверхоперативного запоминающего устройства.

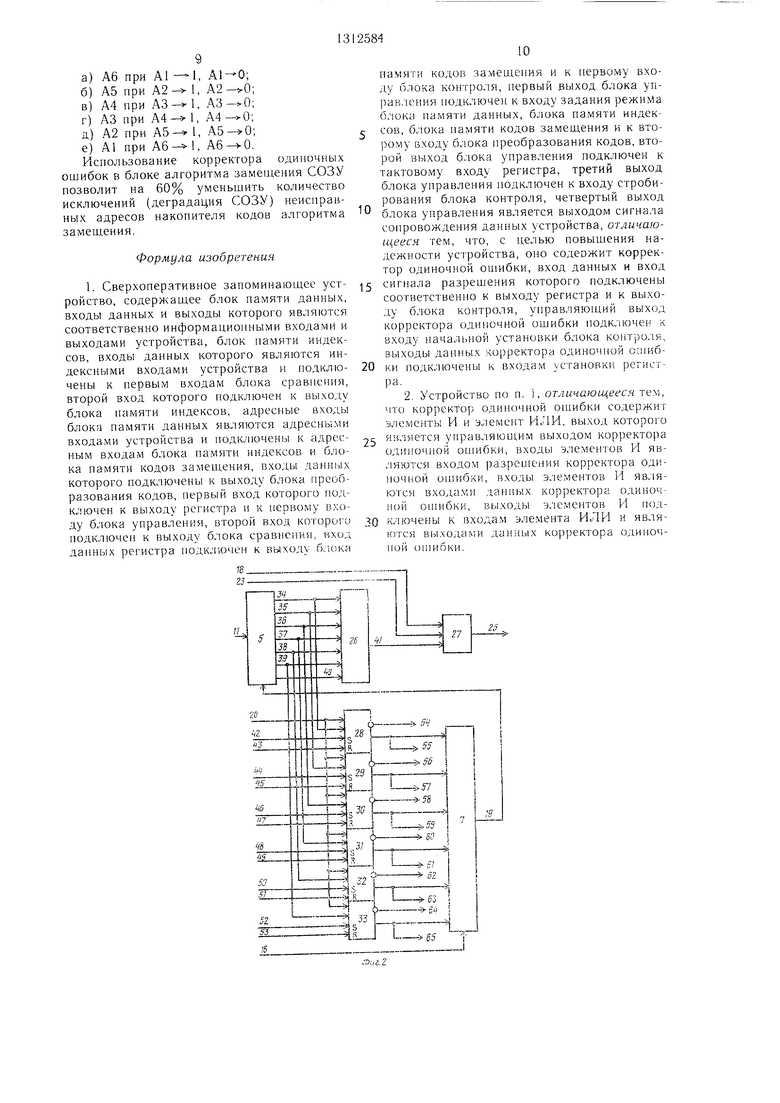

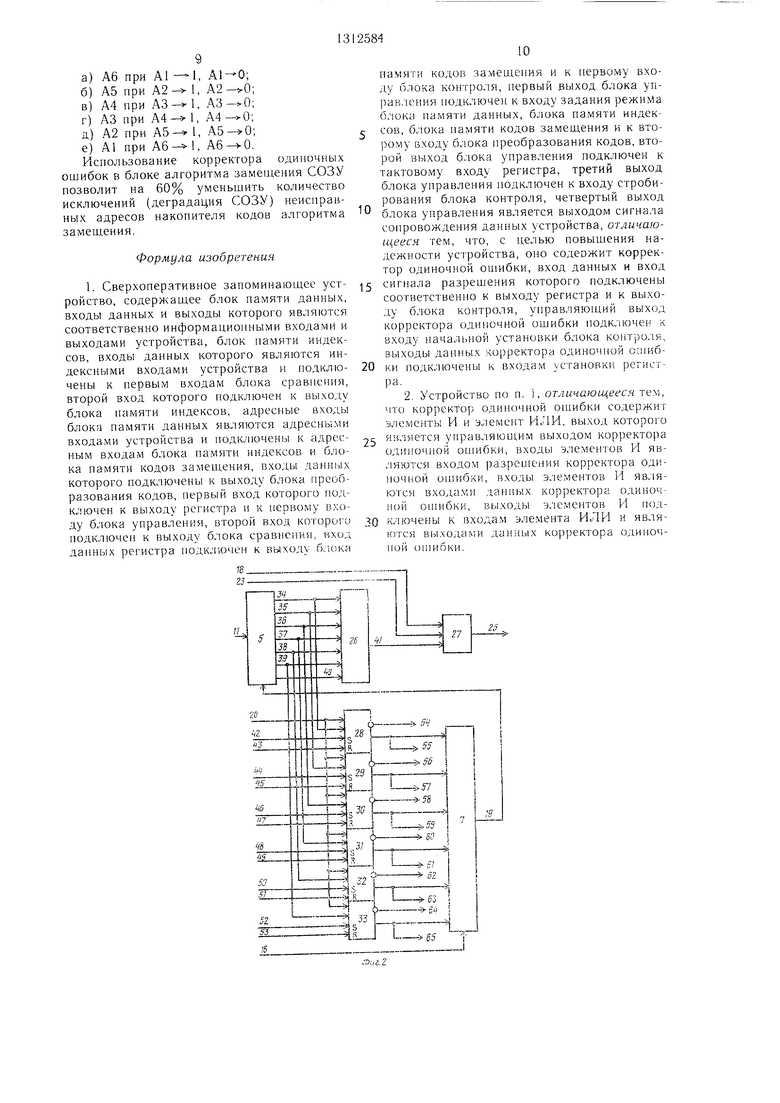

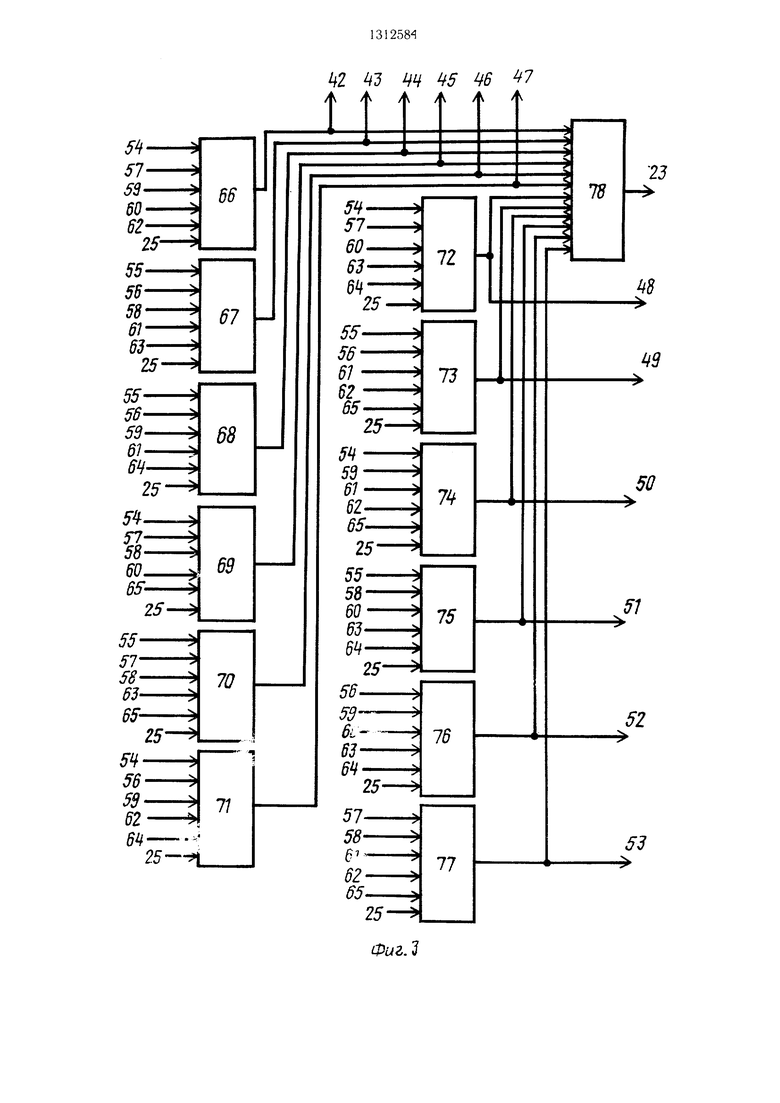

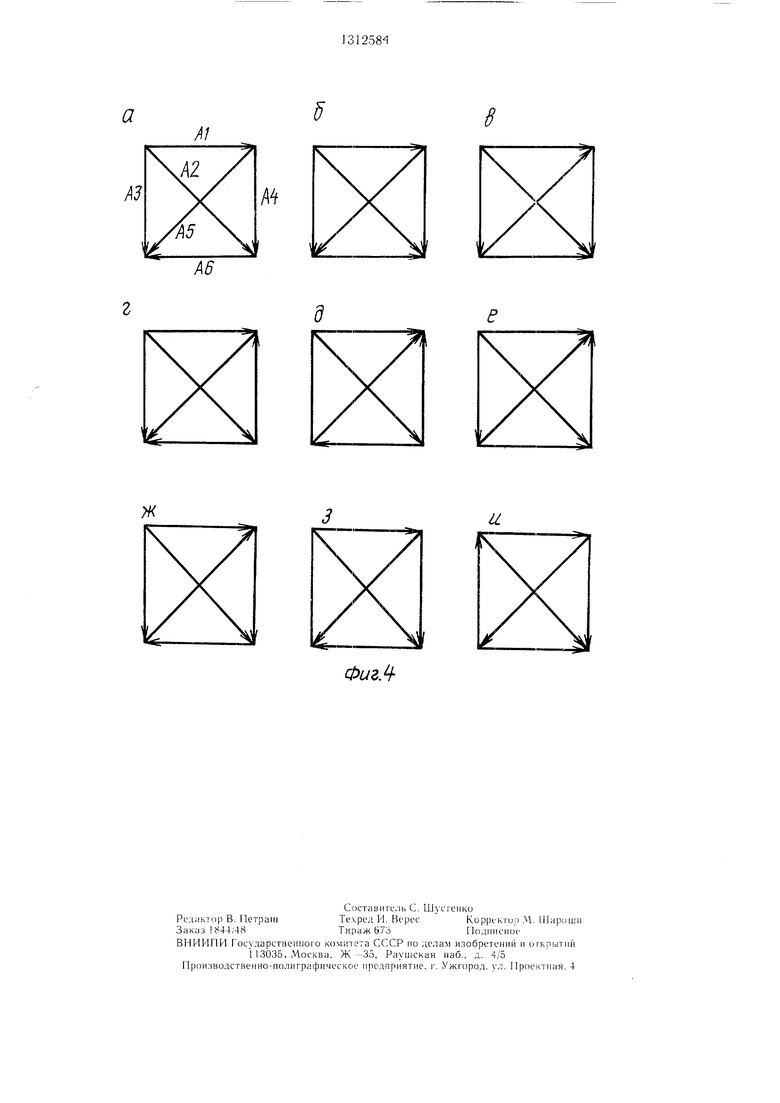

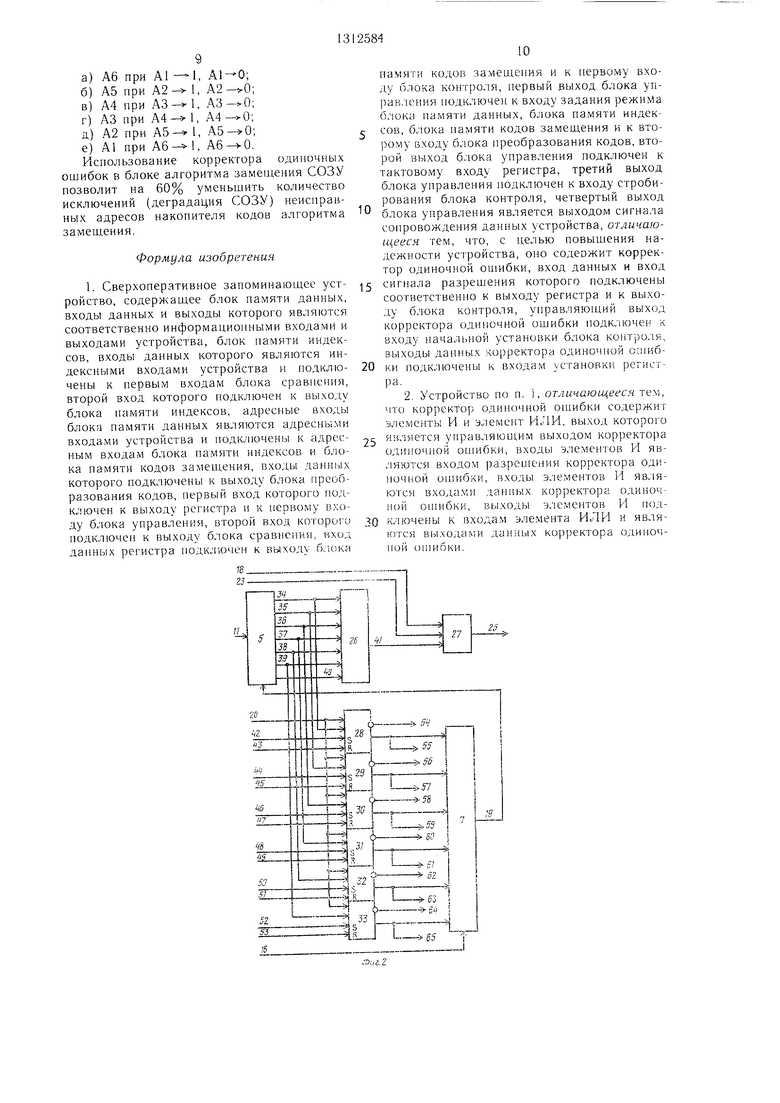

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема блока памяти кодов замещения, блока контроля регистра и блока преобразования; на фиг. 3 - функциональная схема корректора одиночных ощибок; на фиг. 4 - графики возможных вариантов характеристики активностей информации для четырех отделений СОЗУ.

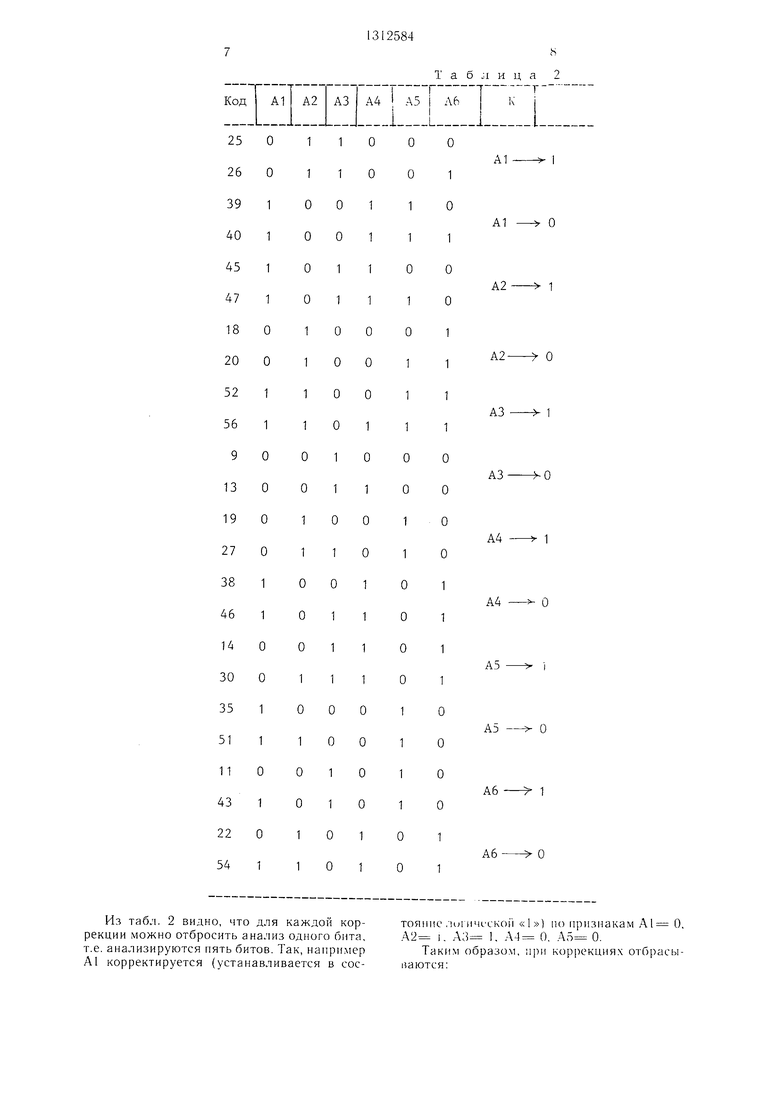

Устройство содержит блок 1 памяти, блок 2 сравнения индексов адреса, блок 3 управления, блок 4 памяти индексов, блок 5 памяти кодов замещения, регистр б, блок 7 преобразования кодов, блок 8 контроля, корректор 9 одиночных ощибок, информационные входы 10, адресные входы 11, индексные входы 12, информационные выходы 13, выходы 14 блока 4, вход 15 управления, выход 16 блока 3, выходы 17, выход 18 блока 3 управления, информационные входы 19 блока 5, вход 20 синхросигнала регистра 6, выход 21 блока 5, выход 22 регистра 6, вход 23 сброса блока 8 контроля, входы 24 коррекции разрядов регистра 6, выход 25 блока 8, сумматор 26 по модулю два, триггер 27, триггеры 28-33, выходы 34-40 блока 5, выход 41 сумматора 26, выходы 42-53 регистра 6, выходы 54-65 триггеров 23-33, элементы И 66--77, элемент ИЛИ 78.

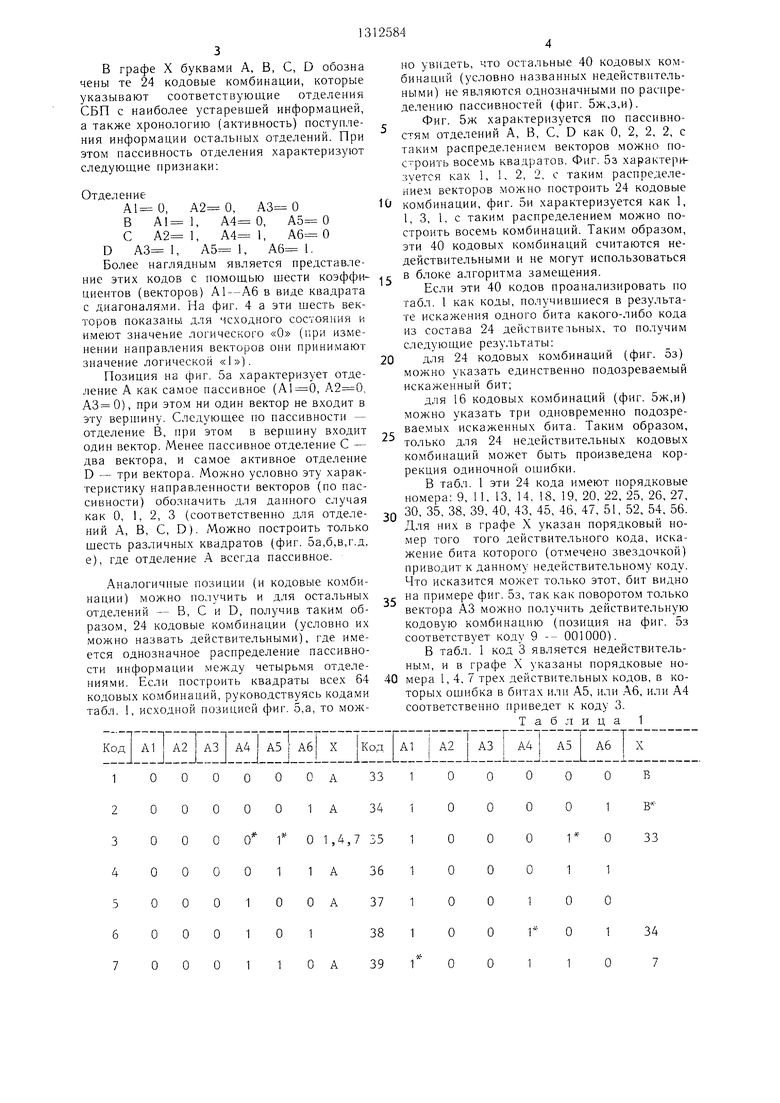

В табл. 1 приведены порядковые номера всех 64 двоичных кодовых комбинаций щестиразрядного кода алгоритма замещения AI-Аб - первые - шестые биты кода алгоритма замещения; обозначение - искаженный бит (три звездочки - три подозреваемых искаженных бита); А, В, С, D - первые - четвертые отделения буферной памяти; в графе X указаны те отделения, которые данный код алгоритма замеи1,ения характеризует как отделения с самой уста- ревщей информацией (пассивные), кроме того, в той же графе (для строк некоторых кодов) указаны но1)ядковые номера тех кодов, искажение одного бита которых приводит к даипому коду.

Устройство работает следуюш,им образом. На входы 11 поступает код адреса от процессора для чтения или записи информации в блок 1 и для чтения или записи индексной части адреса в блок 4. На вход 10 поступают данные, выбранные из оперативной намяти ЭВМ для записи их в блок 1. На вход 12 поступает индексная часть адреса для записи в блок 4 или для сравнения с индексом, прочитанным из блока 4 и пе7

25

реданным в блок 2 сравнения. В последнем случае определяется нахождение требуемых данных в блоке 1.

Если в режиме чтения выясняется, что

с данные находятся в блоке 1, то блок 3 управления по выходу 16 вырабатывает управляющие сигналы для передачи данных в процессор на выход 13. В режиме записи в блоке 3 управления (используя выбранный nolv данному адресу код алгоритма замеще10 ния - выход 22) вырабатываются управляющие сигналы по выходу 16, указывающие одно из четырех (А, В, C,D) отделений блока 1, где должна записываться новая информация, а в блоке 7 преобразования

г формируется новое значение кода алгоритма замещения и записывается по данному адресу в блоке 5.

Блок 3 управления структурно состоит из узла формирования сигнала разрешения выборки следующей микрокоманды в процес20 соре, узла формирования сигналов записи и чтения с накопителей буферной и индексной 1 амяти, узла формирования сигнала выбора одного из четырех отделений буферной памяти, узла формирования сигнала управления блоком контроля четности кодов алгоритма замен1ения к узла формирования синхросигнала занесения кода в приемный регистр кодов алгоритма замещения.

При обрап,ениях процессора к памяти по соответствующему адресу (вход 11) и по

..„ сигналу входа 16 выбирается код алгоритма замещения из блока 5. Этот код по сигналу входа 20 синхросигнала заносится в триггеры 28-33, а на сумматоре по модулю два проверяется на четность, и, если обнаруживается ощибка, она заносится в триггер

дс 27 по входу 41 сигналом выхода 18, который задержан относительно сигнала по входу 20 на время заверщения установки триггеров 28-33. Выход 25 дает разрещение на срабатывание элементов И 66-77, на входы которых поданы прямые и обратные

40 выходы триггеров 54-65 в заданных сочетаниях, характеризую1цих те ошибочные коды алгори гма замещения, для которых возможна коррекция одиночной ошибки. Один из этих элементов Н может выдать сигнал на коррекцию (выходы 42-53), а также по выходу 23 элемент И 78 выдает сигнал ну сброс триггера 27. Носле коррекции по си; налу выхода 16 разрешается в блоке 7 формирование новых значений битов кода алгоритма замещения с учетом старых значеCQ НИИ (выход 22). Новое значение кода алгоритма замещения через вход 19 записывается в блок 5 памяти кодов замещения.

Корректор 9 одиночных шестиразрядного кода алгоритма замещения (фиг. 3) построен исходя из закономер55 постей (особенностей), выявленных в данном предложепии при анализе 64 кодовых ком- бипаций (табл. 1) порядковыми номерами 1 - 64.

45

В графе X буквами А, В, С, D обозна чены те 24 кодовые комбинации, которые указывают соответствующие отделения СБП с наиболее устаревшей информацией, а также хронологию (активность) поступления информации остальных отделений. При этом пассивность отделения характеризуют следующие признаки:

Отделение

, А2 О, А3 О

В А1 1, А4 О, А5 О

С А2 1, А4 1, А6 О

D А3 1, А5 , А6 1.

Более наглядным является представление этих кодов с помощью щести коэффициентов (векторов) А1-Аб в виде квадрата с диагоналями. На фиг. 4 а эти щесть векторов показаны для мсходного состояния и имеют значение логического «О (при изменении направления векторов они принимают значение логической «I).

Позиция на фиг. 5а характеризует отделение А как самое пассивное (, ), при этом ни один вектор не входит в эту вершину. Следующее по пассивности - отделение В, при этом в вершину входит один вектор. Менее пассивное отделение С - два вектора, и самое активное отделение D - три вектора. Можно условно эту характеристику направленности векторов (по пассивности) обозначить для данного случая как О, 1, 2, 3 (соответственно для отделений А, В, С, D). Можно построить только щесть различных квадратов (фиг. 5а,б,в,г.д, е), где отделение А всегда пассивное.

Аналогичные позиции (и кодовые комбинации) можно получить и для остальных отделений - В, С и D, получив таким образом, 24 кодовые комбинации (условно их можно назвать действительными), где имеется однозначное распределение пассивности информации между четырьмя отделениями. Если построить квадраты всех 64 кодовых ко.мбинаций, руководствуясь кодами табл. 1, исходной позицией фиг. 5,а, то можО О О О О О А

О О 1 А 34

О f О 1,4,7 35

01 1А36

1О ОА37 10138 1 1 ОА39

0

но увидеть, что остальные 40 кодовых комбинаций (условно названных недействительными) не являются однозначными по распределению пассивностей (фиг. 5ж,з,и).

Фиг. 5ж характеризуется по пассивно- стям отделений А, В, С, D как О, 2, 2, 2, с таким распределением векторов можно построить восемь квадратов. Фиг. 5з характеризуется как 1, 1, 2, 2, с таким распределением векторов можно построить 24 кодовые

t) комбинации, фиг. 5и характеризуется как 1, 1, 3, 1, с таким распределением можно построить восемь комбинаций. Таким образом, эти 40 кодовых комбинаций считаются недействительными и не могут использоваться

г в блоке алгоритма замещения.

Если эти 40 кодов проанализировать но табл. 1 как коды, получившиеся в результате искажения одного бита какого-либо кода из состава 24 действительных, то получим следующие результаты:

для 24 кодовых комбинаций (фиг. 5з) можно указать единственно подозреваемый искаженный бит;

для 16 кодовых комбинаций (фиг. 5ж,и) можно указать три одновременно подозреваемых искаженных бита. Таким образом, только для 24 не;хействительных кодовых комбинаций может быть произведена коррекция одиночной ошибки.

В табл. 1 эти 24 кода имеют порядковые номера: 9, 11, 13, 14. 18, 19, 20, 22, 25, 26, 27,

Q 30, 35, 38, 39, 40, 43, 45, 46, 47, 51, 52, 54, 56. Для них в графе X указан порядковый номер того того действительного кода, искажение бита которого (отмечено звездочкой) приводит к данному недействительному коду. Что исказится может только этот, бит видно

г на примере фиг. 5з, так как поворотом только вектора A3 можно получить действительную кодовую комбинацию (позиция на фиг. 5з соответствует коду 9 -- 001000).

В табл. 1 код 3 является недействительным, и в графе X указаны порядковые но0 мера 1, 4, 7 трех действительных кодов, в которых ошибка в битах или .А.5, или А6, или А4 соответственно приведет к коду 3.

Таблица 1

5

33 1

33

34

7

Таким образом, выявлена возможность построения корректора одиночной oujHdKH д;1я 24 кодовых комбинаций, т.е. в 60% еду- чаев исключается необходимость деградации (ЮЗУ В15ИДУ одиночных оншбок накопите.чя кодов а.чгорцтма замещения.

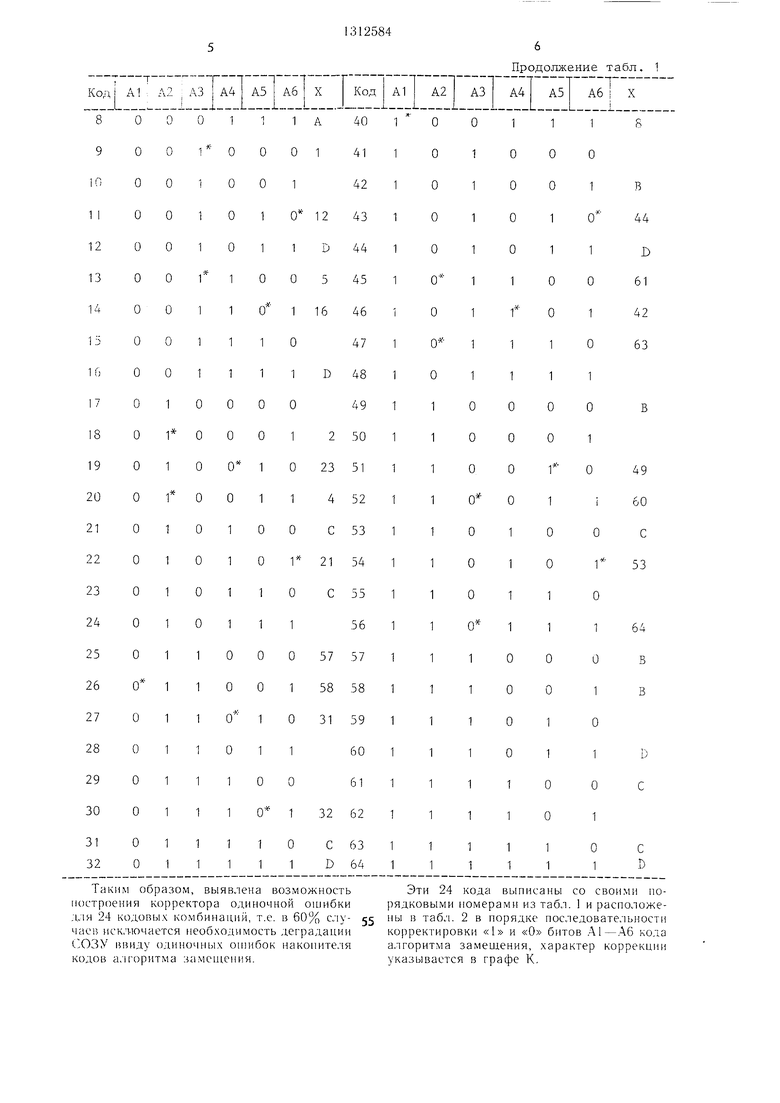

Эти 24 кода вынисаны со своими порядковыми номерами из табл. 1 и расноложе- ны в табл. 2 в норядке носледовательноети корректировки «1 и «О битов .1-А6 кода алгоритма замещения, характер коррекции указывается в графе К.

О

О

1

1

1 1

О О 1 1

О

О

О

О 1

1

О О 1 1 О 1 О 1

11О

11О

ОО1

ОО1

О11

011

1ОО 1ОО 1ОО 1О1

О 1 О 1

1ОО

11О

ОО1

О11

О11

111

000

1оо

о1

о1

о о

1 о 1

1 о

Из табл. 2 видно, что для каждой коррекции можно отбросить анализ одного бита, т.е. анализируются пять битов. Так, например А1 корректируется (устанавливается в сосТаблиц

о о 1 1

о 1

о 1 1 1

о

о 1 1

о

о

о

о

1

1

1

1

о

о

о

1

о

1

о

о

1

1

1

1

о

о

о

о

1

1

1

1

о

о

о

о

1

1

А1

А1

А2

А2АЗ

A3

А4

А4

А5

А5 -

А6

А6- О

тояние лея ичсской «1) 110 признакам А1 О, А2 I. А3 1. А4 О, А5 0.

Таким образом, при коррекция.х отбрасываются:

а)А6 при А1 б)А5 при А2в)А4 при A3 -

г)A3 при А4 -

д)А2 при А5е)А1 при А6 - Использование

9 1,

10

А1-0; А2 . корректора

ошибок в блоке алгоритма замещения СОЗУ позволит на 60% уменьшить количество исключений (деградация СОЗУ) неисправных адресов накопителя кодов алгоритма замеш,ения.

Формула изобретения

1. Сверхоперативное запоминаюшее устройство, содержащее блок памяти данных, входы данных и выходы которого являются соответственно информационными входами и выходами устройства, блок памяти индексов, входы данных которого являются индексными входами устройства и подключены к первым входам блока сравнения, второй вход которого подключен к выходу блока памяти индексов, адресные входы блока памяти данных являются адресными входами устройства и нодключены к адресным входам блока памяти индексов и блока памяти кодов замеи1,ения, входы данн1 1х которого нодключены к выходу блока преобразования кодов, первый вход которого подключен к выходу регистра и к нервому входу блока управления, второй вход KOTOpoi O подключен к выходу блока сравнения, вход данных регистра подключен к выходу 6.;i()Ka

10

памяти кодог замешения и к первому входу блока контроля, первый БЬ1ход блока управления подключен к входу задания режима блока памяти данных, блока памяти индек сов, блока памяти кодов замеш,епия и к второму входу блока преобразования кодов, вто- одиночныхрой выход блока управления подключен к

тактовому входу регистра, третий выход блока управления подключен к входу строби- рования блока контроля, четвертый выход блока унравления является выходом сигнала сопровождения данных устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит корректор одиночной ошибки, вход данных и вход

15 сигнала разрешения которого подключены соот1)етственпо к выходу регистра и к выходу блока контроля, управляющий выход корректора одиночной ошибки иодключе к входу начальной установки блока KOHTJJO.IH, выходы данных корректора одиночной о:ниб20 ки подк;иочены к входам установки, регистра.

2. Устройство по п. i, отличающееся тем, что корректор одиночной ошибки содержит элементы И и элемент ИЛИ, выход которого

25 ,ляется управляюушм выходом корректора одиночной оншбки, входы элементов И являются входом разреи1епия корректора одиночной оп1ибки, входы элементов 1-1 яв;|я- ются входами данных корректора одиночной ошибки, выходы элементов И под30 ключены к входам элемента ИЛИ и являются выходами данных корректора одиночной ()1НИбкИ.

10

42 3 ЦЦ 45 46 7

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адреса замещаемого блока памяти | 1990 |

|

SU1777142A1 |

| Устройство обработки данных процессора | 1988 |

|

SU1647584A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| СПОСОБ И УСТРОЙСТВО ПОСТРОЕНИЯ ПРОРЕЖЕННОГО ПОЛЯРНОГО КОДА | 2014 |

|

RU2665233C1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| ОПРЕДЕЛЕНИЕ ДЛИНЫ ГРУППЫ СИМВОЛЬНЫХ ДАННЫХ, СОДЕРЖАЩЕЙ СИМВОЛ ОКОНЧАНИЯ | 2013 |

|

RU2621000C2 |

| Способ сжатия данных | 2016 |

|

RU2628199C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения запоминающих устройств высокопроизводительных ЭВМ, имеющих систему отрицательной или многоуровней памяти. Цель изобретения - повышение надежности устройства. Сверхоперативное запоминающее устройство содержит блок 1 памяти данных, блок 2 сравнения, блок 3 управления, блок 4 памяти индексов, блок 5 памяти кодов замещения, регистр 6, блок 7 преобразования кодов, блок 8 контроля, корректор 9 одиночной оищбки, информационные 10, адресные II и индексные 12 входы, выходы 13. В соответствии с адресом на входе 11 в блоки 1 и блок 4 записываются данные с входа 10 и индекс с входа 12 или считываются на выход 13 и на из входов блока 2. Блок 2 определяет нахождение требуемых данных в блоке 1 и иницни|п - ет блок 3 на формирование управляющих сигналов для выдачи данных на выхо.ч 13. При записи данные в соответствии с кодом, хранимым в б. юке 5 (алгоритмом замен1е- ния), записываются по адресу в блок 1, а блок 7 формирует новое значение кода алгоритма и записывает его в блок 5. Б.чок 8 осу1Г1ест 5ляет контроль по модулю два информации, считываемой из блока 5, и вырабатывает curna. i разре1иения работы корректора 9, исправляющего 11Н(}зормацию, хранящуюся в регистре 6. 1 з.н. ф-лы, 4 нл. (О сл

ц.

Фиг,

| Гидроударник | 1986 |

|

SU1370219A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СПОСОБ ВПАИВАНИЯ СТЕКЛЯННОЙ ТРУБКИ ДЛЯ ОТВОДА ВОЗДУХА ИЛИ ИНОГО ГАЗА, ОТКАЧИВАЕМОГО ИЗ КОЛБ ЭЛЕКТРИЧЕСКИХ ЛАМП НАКАЛИВАНИЯ И КАТОДНЫХ | 1924 |

|

SU1046A1 |

| Техническое описание блока управления памятью. | |||

Авторы

Даты

1987-05-23—Публикация

1985-08-06—Подача