1

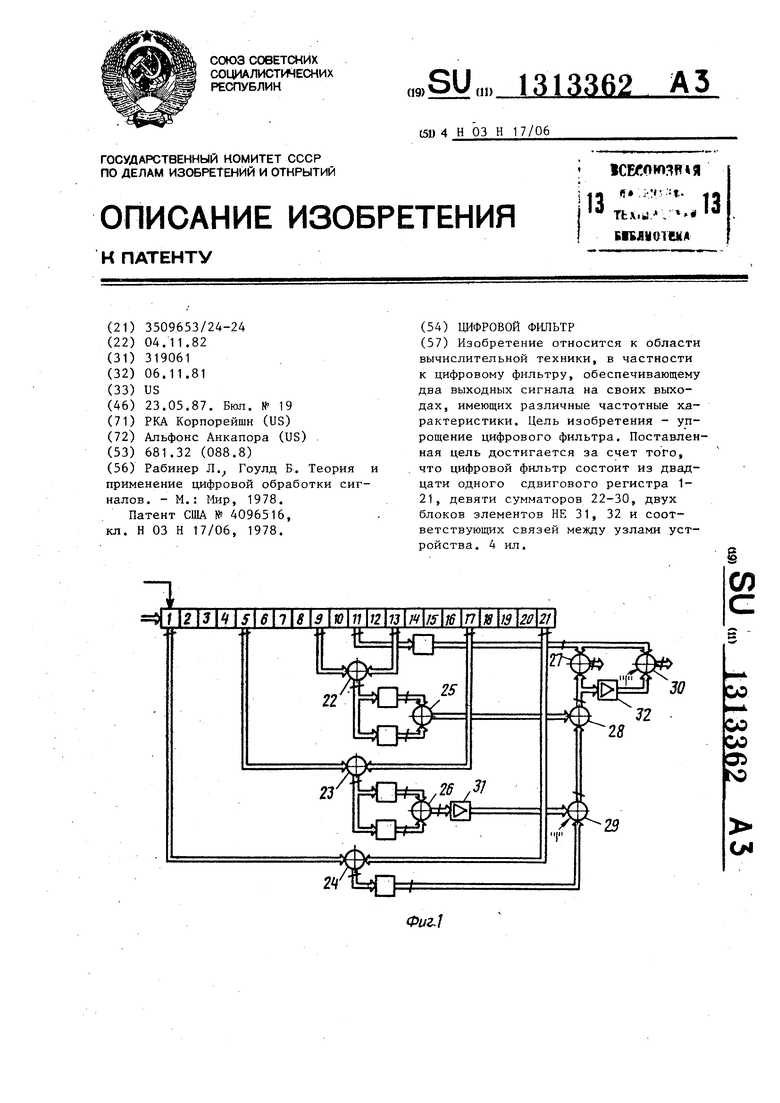

Изобретение относится к вычислительной технике, в частности к цифровому фильтру, обеспечивающему два выходных сигнала на своих выходах, проявляющих различные частотные характеристики по отношению к входному сигналу.

Цель изобретения - упрощение фильтра.

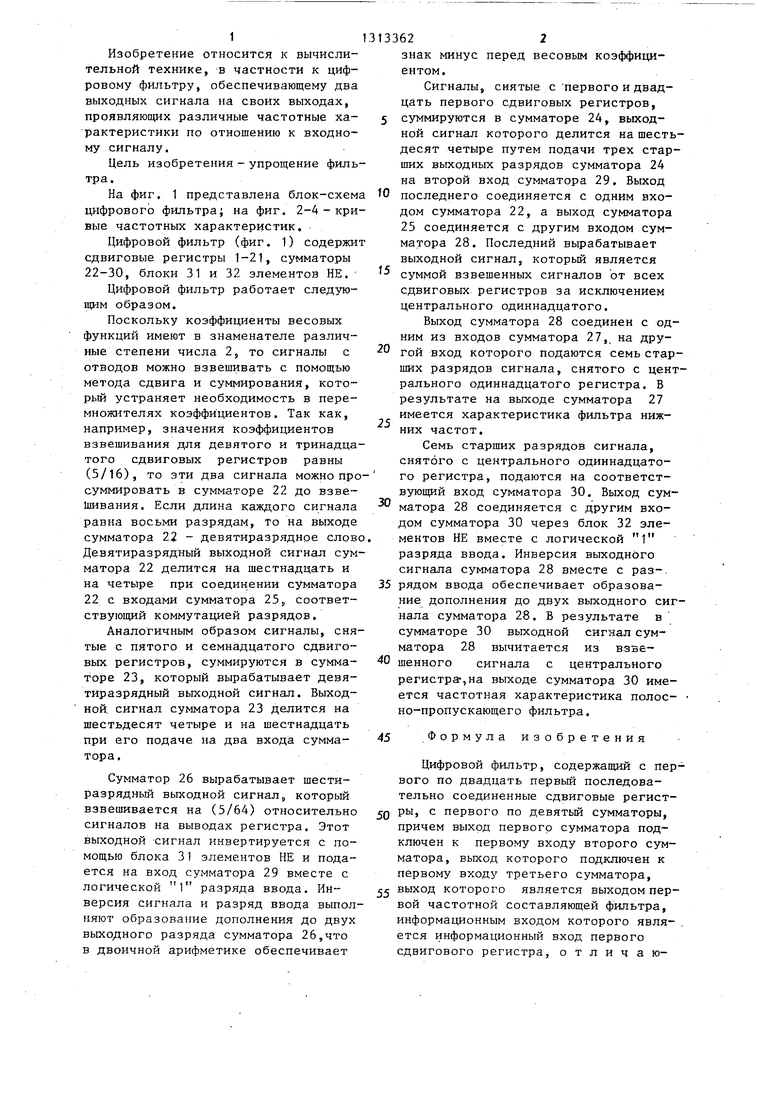

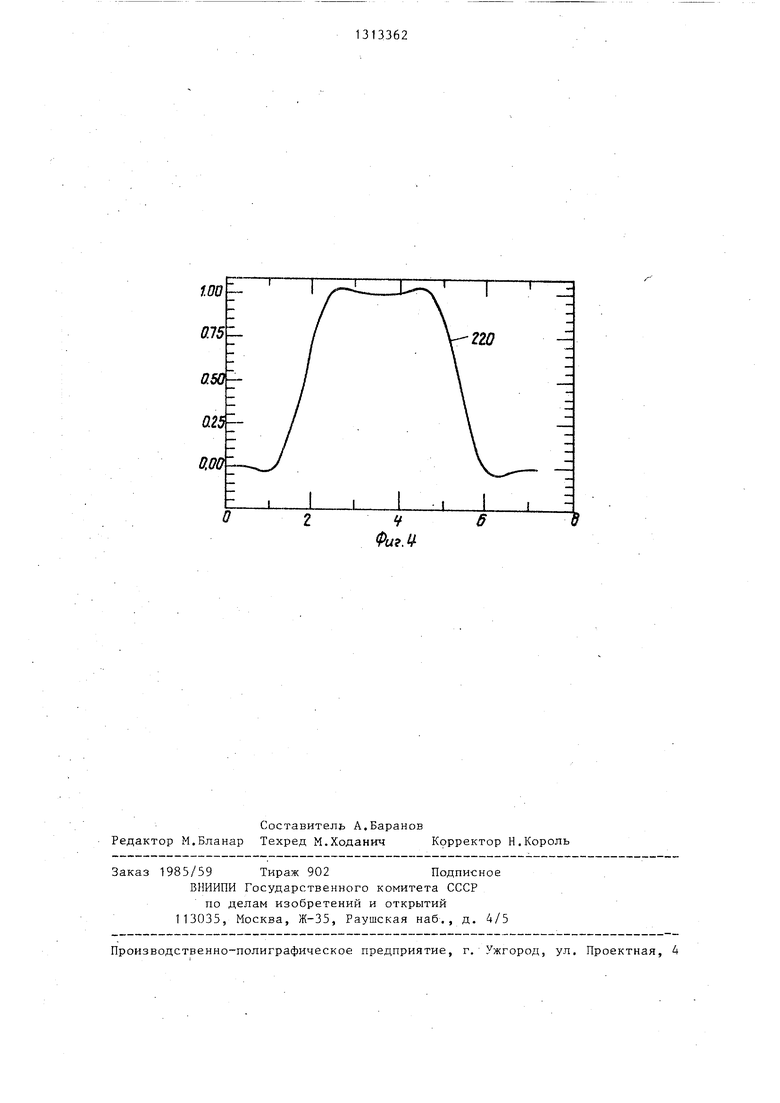

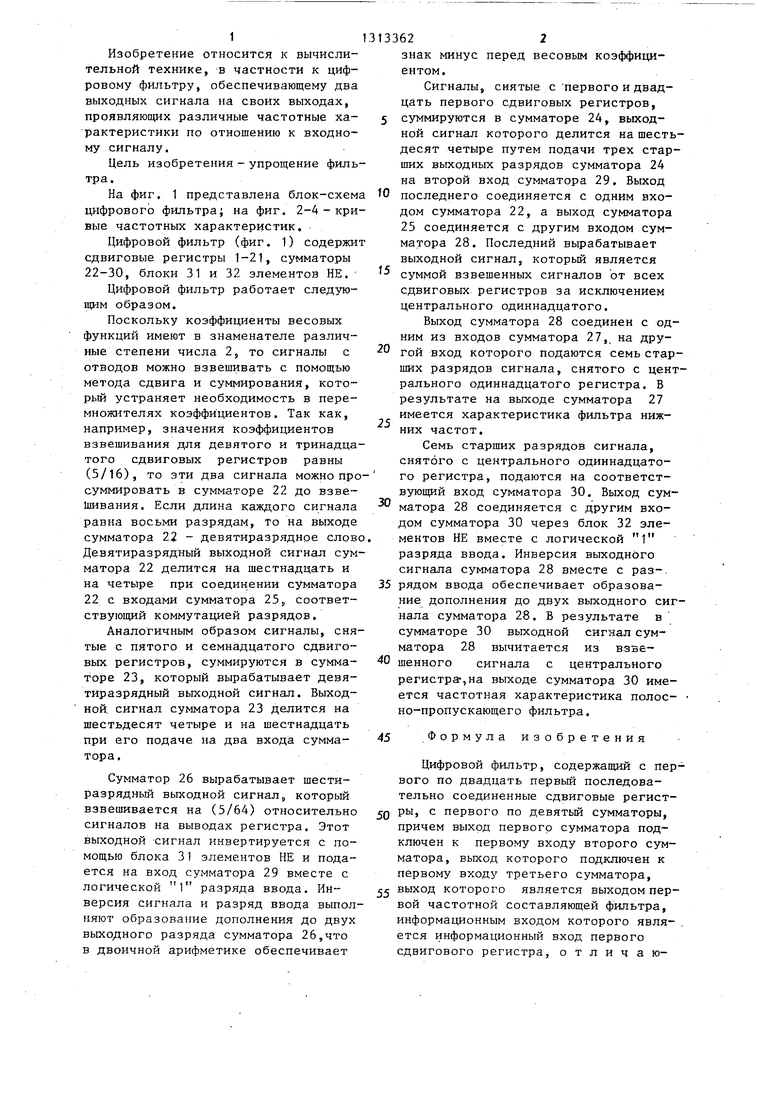

На фиг, 1 представлена блок-схем цифрового фильтра; на фиг, 2-4 - кривые частотных характеристик.

Цифровой фильтр (фиг, 1) содержи сдвиговые регистры 1--21, сумматоры 22-30, блоки 31 и 32 элементов НЕ,

Цифровой фильтр работает следующим образом.

Поскольку коэффициенты весовых функций имеют в знаменателе различные степени числа 2, то сигналы с отводов можно взвешивать с помощью метода сдвига и суммирования, кото- устраняет необходимость в перемножителях коэффициентов. Так как, например, значения коэффициентов взвешивания для девятого и тринадцатого сдвиговых регистров равны (5/16), то эти два сигнала можно про суммировать в сумматоре 22 до взвешивания. Если длина каждого сигнала равна восьми разрядам, то на выходе сумматора 22 - девятиразрядное слов Девятиразрядный выходной сигнал сумматора 22 делится на шестнадцать и на четыре при соединении сумматора 22 с входами сумматора 25,, соответствующий коммутацией разрядов,

Аналогичным образом сигналы, снятые с пятого и семнадцатого сдвиговых регистров, суммируются в сумматоре 23, который вырабатывает девятиразрядный выходной сигнал. Выходной, сигнал сумматора 23 делится на шестьдесят четыре и на шестнадцать при его подаче на два входа сумматора.

Сумматор 26 вырабатывает шестиразрядный выходной сигналj который взвешивается на (5/64) относительно сигналов на выводах регистра. Этот выходной -сигнал инвертируется с помощью блока 31 элементов НЕ и подается на вход сумматора 29 вместе с логической 1 разряда ввода. Инверсия сигнала и разряд ввода выполняют образование дополнения до двух выходного разряда сумматора 26,что в двоичной арифметике обеспечивает

622

знак минус перед весовым коэффициентом.

Сигналы, снятые с первого и двадцать первого сдвиговых регистров,

суммируются в сумматоре 24, выходной сигнал которого делится на шестьдесят четыре путем подачи трех старших выходных разрядов сумматора 24 на второй вход сумматора 29, Выход

последнего соединяется с одним входом сумматора 22, а выход сумматора 25 соединяется с другим входом сумматора 28, Последний вырабатывает выходной сигнал, который является

суммой взвешенньпс сигналов от всех сдвиговых регистров за исключением центрального одиннадцатого.

Выход сумматора 28 соединен с одним из входов сумматора 27,. на другой вход которого подаются семь старших разрядов сигнала, снятого с центрального одиннадцатого регистра, В результате на выходе сумматора 27 имеется характеристика фильтра нижних частот.

Семь старших разрядов сигнала, снятого с центрального одиннадцатого регистра, подаются на соответствующий вход сумматора 30, Выход сумматора 28 соединяется с другим входом сумматора 30 через блок 32 элементов НЕ вместе с логической 1 разряда ввода. Инверсия выходного сигнала сумматора 28 вместе с раз-.

рядом ввода обеспечивает образование дополнения до двух выходного сигнала сумматора 28, В результате в сумматоре 30 выходной сигнал сумматора 28 вычитается из взве

шенного сигнала с центрального регистра-,на выходе сумматора 30 имеется частотная характеристика полос- но-пропускающего фильтра.

45

Формула изобретения

Цифровой фильтр, содержащий с первого по двадцать первый последовательно соединенные сдвиговые регист Q ры, с первого по девятьм сумматоры, причем выход первого сумматора подключен к первому входу второго сумматора, выход которого подключен к первому входу третьего сумматора,

.j выход которого является выходом первой частотной составляющей фильтра, информационным входом которого является информационный вход первого сдвигового регистра, отличаю313

щ и и с я тем, что, с целью упрощения, он содержит первый и второй блоки элементов НЕ, причем выходы девятого и тринадцатого сдвиговых регистров подключены соответственно к первому и второму входам четвертого сумматора, выходы i-ro(,M; M- разрядность) и j-ro (,M) разрядов которого подключены соответственно к (1-4)-му разряду первого входа и (j-2)-My разряду второго входа пятого сумматора, выход которого подключен к второму входу второго сумматора, выход которого подключен к входу первого блока элементов НЕ,выход которого подключен к первому входу шестого сумматора, выход которого является-выходом второй частотной составляющей фильтра, выходы пятого и семнадцатого сдвиговых регистров

362 .4

подключены соответственно к первому и второму входам седьмого сумматора, выходы К-го () и i-ro разрядов которого подключены соответственно к

5 (К-б)-му разряду первого входа и (1-А)-му разряду второго входа восьмого сумматора, выход которого подключен к входу второго блока элементов НЕ, выход которого подключен к

10 первому входу первого сумматора,

(К-б)-й разряд второго входа которого подключен к выходу К-го разряда девятого сумматора, первый и второй входы которого подключены к выходам

15 соответственно первого и двадцать первого сдвиговых регистров, выход 1-го (,М) разряда одиннадцатого сдвигового регистра подключен к (1-1)-м разрядам вторых входов треть0 его ч шестого сумматоров.

0,

О

| название | год | авторы | номер документа |

|---|---|---|---|

| Строчный преобразователь для устройства воспроизведения изображения | 1977 |

|

SU1037848A3 |

| Устройство для записи на видеопластинку | 1980 |

|

SU1103813A3 |

| УСТРОЙСТВО СОВМЕСТНОГО КОДИРОВАНИЯ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497180C1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Цифровой телевизионный приемник | 1983 |

|

SU1321384A3 |

| Устройство для деления 48-разрядных чисел | 1984 |

|

SU1239712A1 |

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Демодулятор взаимоортогональных синусоидальных сигналов с фазоразностной модуляцией | 1985 |

|

SU1277423A1 |

| Параллельное вычислительное устройство для решения разностных уравнений задач теории поля | 1975 |

|

SU742945A1 |

Изобретение относится к области вычислительной техники, в частности к цифровому фильтру, обеспечивающему два выходных сигнала на своих выходах, имеющих различные частотные характеристики. Цель изобретения - упрощение цифрового фильтра. Поставленная цель достигается за счет того, что цифровой фильтр состоит из двадцати одного сдвигового регистра 1- 21, девяти сумматоров 22-30, двух блоков элементов НЕ 31, 32 и соответствующих связей между узлами устройства. 4 ил. n Слд CO СлЭ s CH

| Рабинер Л | |||

| Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| - М.: Мир, 1978 | |||

| Патент США № 4096516, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| L si / ms | |||

Авторы

Даты

1987-05-23—Публикация

1982-11-04—Подача