Изобретение относится к технике организации интервальных вычислений в формате с плавающей запятой и направлено на повышение точности оценивания интервальных границ при заданной разрядности кода, хранимого в памяти ЭВМ. Предполагается, что промежуточные вычисления могут выполняться с большей разрядностью, чем разрядность чисел сохраняемых в памяти ЭВМ. Предлагаемое устройство использует 64 разряда для совместного кодирования двух границ арифметического интервала.

Известны метод и аппаратура для представления арифметических интервалов в вычислительной системе (US 6658443 B1, 02.12.2003).

Система выполняет вычислительные операции по правилам интервальной арифметики, получая результат вычислений в виде интервала. Результирующий интервал представлен первым числом в формате с плавающей запятой, являющимся первой границей интервала и вторым числом в формате с плавающей запятой, являющимся второй границей интервала. Оба числа, представляющие границы интервала, независимо записываются в память компьютера.

Сущность технического решения проявляется в ситуациях, когда интервалы становятся очень большими, то есть когда значимость результата в значительной степени является утерянной.

Недостатком системы является низкая точность метода, провоцирующая ситуацию получения больших интервалов, представляющих результаты расчетов.

Известна вычислительная система для интервальных вычислений, наиболее близкая по своей технической сущности к предлагаемому изобретению и выбранная в качестве прототипа (RU 2006929 С1, 30.01.1994).

Данная вычислительная система содержит первый и второй модули памяти для хранения чисел, являющихся верхней и нижней границами интервалов, два арифметических устройства для вычисления верхних и нижних границ интервалов, группу мультиплексоров, осуществляющих передачу выбираемых из памяти в арифметические блоки и передачу записываемых из арифметических блоков в память кодов интервалов.

В процессе вычислений из двух модулей памяти одновременно извлекается верхняя и нижняя границы первого интервала, затем одновременно извлекаются верхняя и нижняя границы второго интервала. Считанные из памяти числа надлежащим образом передаются к операционным блокам, осуществляющим вычисления по правилам интервальной арифметики. Получившийся в результате вычислений интервал записывается в память в виде двух чисел, представленных в формате с плавающей запятой.

Недостаток устройства, выбранного в качестве прототипа - малая разрядность мантисс верхней и нижней граней, запоминаемых в памяти, что приводит к быстрому увеличению интервалов при вычислениях, что, в свою очередь, приводит к чрезмерно пессимистическим оценкам точности результатов вычислений.

Технический результат изобретения - увеличение точности результатов интервальных вычислений в формате с плавающей запятой при сохранении суммарной разрядности сохраняемого в памяти кода верхней и нижней границ интервала, при условии, что промежуточные вычисления выполняются над числами с увеличенной разрядностью. Технический результат достигается за счет совместного кодирования запоминаемых в памяти значений верхней и нижней границ интервала результата вычислений, при этом для задания мантиссы чисел, не подвергавшихся округлению, используется 42 разряда (в прототипе всего 23 разряда). Предлагаемое устройство при совместном кодировании близких чисел позволяет сохранить информацию о большем числе разрядов мантиссы. Повышенная точность границ интервала обеспечивается до тех пор, пока одна из границ не превысит по абсолютному значению другую границу в 32 раза. Таким образом, всегда, когда результаты вычислений можно еще считать достоверными, предлагаемое устройство способствует обеспечению большей точности оценивания результатов вычислений.

Технический результат достигается тем, что предлагаемое устройство совместного кодирования границ при интервальных вычислениях содержит первый D-триггер, RS-триггер и первый регистр, информационный вход, вход установки и вход сброса которых подключены к первому управляющему входу устройства, второй регистр и регистр сдвига, вход разрешения синхросигнала и вход загрузки которых подключены к второму управляющему входу устройства, второй триггер, вход разрешения записи которого подключен к третьему управляющему входу устройства, а выход является старшим шестьдесят четвертым разрядом информационного выхода устройства, регистр мультиплексор, первый информационный вход которого подключен к пятидесяти младшим разрядам первого информационного входа устройства, пятьдесят первый разряд которого соединен с информационным входом второго триггера, младшие сорок два разряда второго информационного входа устройства соединены с параллельным информационным входом регистра сдвига, при этом разряды с сорок третьего по пятьдесят первый второго информационного входа устройства соединены с информационным входом второго регистра, входы синхронизации всех триггеров и регистров подключены к входу синхронизации устройства; выход первого регистра соединен с адресными входами первого, второго, третьего блоков ПЗУ и первым входом первого блока сравнения, восемь младших разрядов выхода второго регистра соединены с входом вычитаемого первого вычитателя и с входами первого элемента «ИЛИ», выход которого соединен с последовательным входом сдвигового регистра; выход регистра мультиплексора соединен с первым входом первого сумматора, при этом восемь старших разрядов упомянутого выхода соединены с входом уменьшаемого первого вычитателя и являются разрядами, с пятьдесят шестого по шестьдесят третий, информационного выхода устройства; второй вход первого сумматора, как и инверсные входы первой группы элементов «И» подключены к шестнадцати старшим разрядам двадцатипятиразрядного выхода первого блока ПЗУ, а инверсные входы второй группы элементов «И» подключены к пятнадцати старшим разрядам выхода первого блока ПЗУ, выход второй группы элементов «И» подключен к пятнадцати младшим разрядам второго информационного входа регистра мультиплексора, сорок второй разряд входа регистра мультиплексора обнулен, а разряды с шестнадцатого по сорок первый и разряды с сорок третьего по пятидесятый упомянутого входа подключены к разрядам с семнадцатого по сорок второй и разрядам с сорок третьего по пятидесятый выхода первого сумматора, при этом разряды с семнадцатого по сорок второй выхода первого сумматора являются разрядами с тридцатого по пятьдесят пятый информационного выхода устройства; старшие двадцать пять разрядов управляющего входа группы однобитных мультиплексоров подключены к выходу блока ПЗУ, а выход группы мультиплексоров является разрядами со второго по двадцать девятый информационного выхода устройства, выход первого вычитателя соединен с первым входом второго блока сравнения и входом уменьшаемого второго вычитателя, на вход вычитаемого которого заведено константное значение «3», при этом на второй вход второго блока сравнения заведено константное значение «1»; входы первого элемента суммирования по модулю два подключены к выходу второго D-триггера и к старшему разряду выхода второго регистра; вход уменьшаемого третьего вычитателя подключен к сорока двум младшим разрядам выхода первого сумматора, при этом шестнадцать младших разрядов входа вычитаемого подключены к выходу первой группы элементов «И», а двадцать шесть старших разрядов упомянутого входа подключены к старшим разрядам выхода регистра сдвига, выход третьего вычитателя соединен с сорока двумя младшими разрядам входа приоритетного шифратора, при этом сорок один младший разряд выхода третьего вычитателя соединен с информационным входом сдвигателя, пятиразрядный управляющий вход которого подключен к выходу второго блока ПЗУ, а двадцатипятиразрядный выход соединен с первым информационным входом первого мультиплексора, при этом выход приоритетного шифратора соединен с информационным входом первого регистра и вторым входом первого блока сравнения; выход «равно» второго блока сравнения соединен с входом первого элемента «И», другой вход которого подключен к инверсному выходу второго элемента «ИЛИ», и входом второго элемента «И», другой вход которого подключен к сорок второму разряду выхода регистра мультиплексора, при этом входы второго элемента «ИЛИ» подключены к выходу первого элемента суммирования по модулю два и сорок второму разряду выхода регистра мультиплексора; выход «больше» второго блока сравнения соединен с входом третьего элемента «ИЛИ», другие входы которого подключены к выходам второго и третьего элементов «И», выход соединен с сорок четвертым разрядом входа приоритетного шифратора, первым и вторым разрядами управляющего входа группы мультиплексоров, а инверсный выход является первым разрядом информационного выхода устройства; выход «меньше» второго блока сравнения соединен с входом четвертого элемента «И» и с инверсным входом третьего элемента «И», другие входы которых подключены к выходу первого элемента суммирования по модулю два 27; устройство также содержит второй элемент суммирования по модулю два, входы которого подключены к сорок третьим разрядам выходов регистра мультиплексора и первого сумматора, пятый элемент «И», входы которого подключены к выходам первого элемента «И» и первого D-триггера, шестой элемент «И», входы которого подключены к выходам RS-триггера и второго элемента суммирования по модулю два, четвертый элемент «ИЛИ», входы которого подключены к выходам третьего элемента «ИЛИ» и четвертого элемента «И», а выход соединен с управляющим входом первого мультиплексора и третьим разрядом управляющего входа группы мультиплексоров, седьмой элемент «И», входы которого подключены к выходу шестого элемента «И» и к инверсному выходу четвертого элемента «ИЛИ», пятый элемент «ИЛИ», входы которого подключены к третьему управляющему входу устройства и к выходу шестого элемента «И», а выход соединен с входом разрешения синхросигнала регистра мультиплексора, шестой элемент «ИЛИ», один вход которого подключен к второму управляющему входу устройства, два других входа подключены к выходам пятого и седьмого элементов «И», а выход соединен с входом разрешения синхросигнала регистра сдвига и входом седьмого элемента «ИЛИ», другие входы которого подключены к первому управляющему входу устройства, выходу первого D-триггера, выходу «не равно» первого блока сравнения, при этом инверсный вход подключен к выходу RS-триггера, а инверсный выход соединен с входом сброса RS-триггера и является выходом готовности устройства, четвертый вычитатель, чей вход уменьшаемого подключен к выходу второго вычитателя, а на вход вычитаемого заведено константное значение «3», восьмой и девятый элементы «ИЛИ», входы которых подключены к восьмиразрядным выходам второго и четвертого вычитателей соответственно, инверсные входы и вход десятого элемента «ИЛИ» подключены к выходу восьмого элемента «ИЛИ», инверсному выходу займа второго вычитателя и выходу четвертого элемента «И», а выход десятого элемента «ИЛИ» соединен с входом одиннадцатого элемента «ИЛИ», входом восьмого элемента «И», инверсным входом девятого элемента «И» и инверсным входом обнуления выхода второго мультиплексора; выход восьмого элемента «И» соединен с управляющим входом третьего мультиплексора и первым входом десятого элемента «И», а инверсный вход восьмого элемента «И», как и инверсный вход обнуления выхода третьего мультиплексора, подключен к выходу четвертого элемента «И»; инверсные входы одиннадцатого элемента «ИЛИ» подключены к выходу девятого элемента «ИЛИ» и инверсному выходу займа четвертого вычитателя, а выход и инверсный выход одиннадцатого элемента «ИЛИ» соединены с входом девятого элемента «И» и управляющим входом четвертого мультиплексора; первый информационный вход третьего мультиплексора подключен к семнадцатому разряду выхода регистра сдвига, а второй информационный вход подключен к второму разряду выхода первого вычитателя, причем первый разряд упомянутого выхода соединен с вторым входом десятого элемента «И»; первый информационный вход второго мультиплексора подключен к восемнадцатому и девятнадцатому разрядам выхода регистра сдвига, второй информационный вход подключен к первому и второму разрядам выхода второго вычитателя, а управляющий вход второго мультиплексора подключен к выходу девятого элемента «И»; первый информационный вход четвертого мультиплексора подключен к разрядам с двадцатого по двадцать седьмой выхода регистра сдвига, а второй информационный вход подключен к восьмиразрядному выходу четвертого вычитателя; третья группа элементов «И», первые входы которых подключены к выходу четвертого элемента «И», а вторые входы подключены к выходу десятого элемента «И» и выходу третьего мультиплексора; при этом первые два разряда второго информационного входа первого мультиплексора подключены к выходу второго мультиплексора, разряды с третьего по десятый подключены к выходу четвертого мультиплексора, а разряды с одиннадцатого по двадцать пятый упомянутого входа подключены к разрядам с двадцать восьмого по сорок второй выхода регистра сдвига, разряды с первого по двенадцатый первого информационного входа группы мультиплексоров подключены к выходу третьего блока ПЗУ, а разряды с тринадцатого по двадцать восьмой подключены к шестнадцати младшим разрядам выхода первого сумматора; первый разряд второго информационного входа группы мультиплексоров подключен к выходу первого элемента суммирования по модулю два, второй и третий разряды подключены к выходу третьей группы элементов «И», а разряды с четвертого по двадцать восьмой подключены к выходу первого мультиплексора.

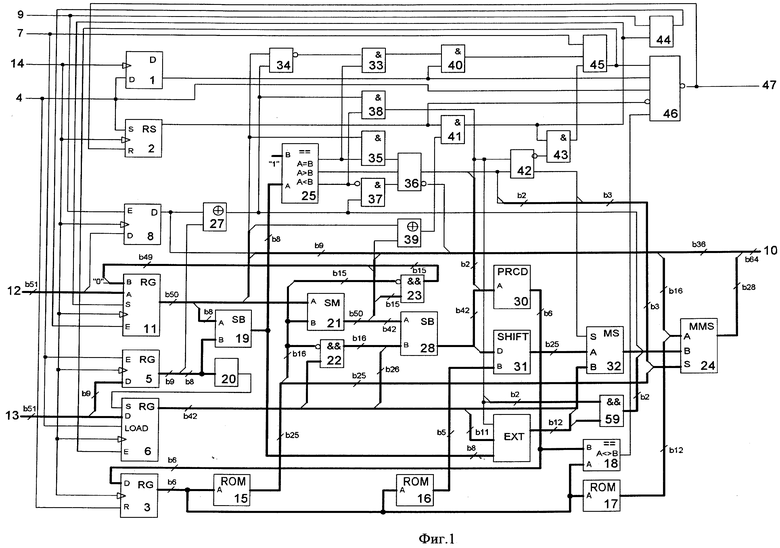

На фиг.1 приведена схема предлагаемого устройства совместного кодирования границ при интервальных вычислениях.

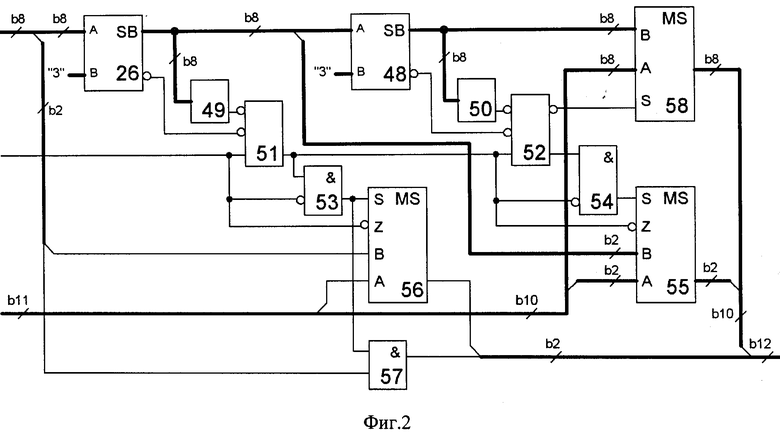

На фиг.2 раскрыта функциональная схема блока ЕХТ, являющегося частью схемы, представленной на фиг.1.

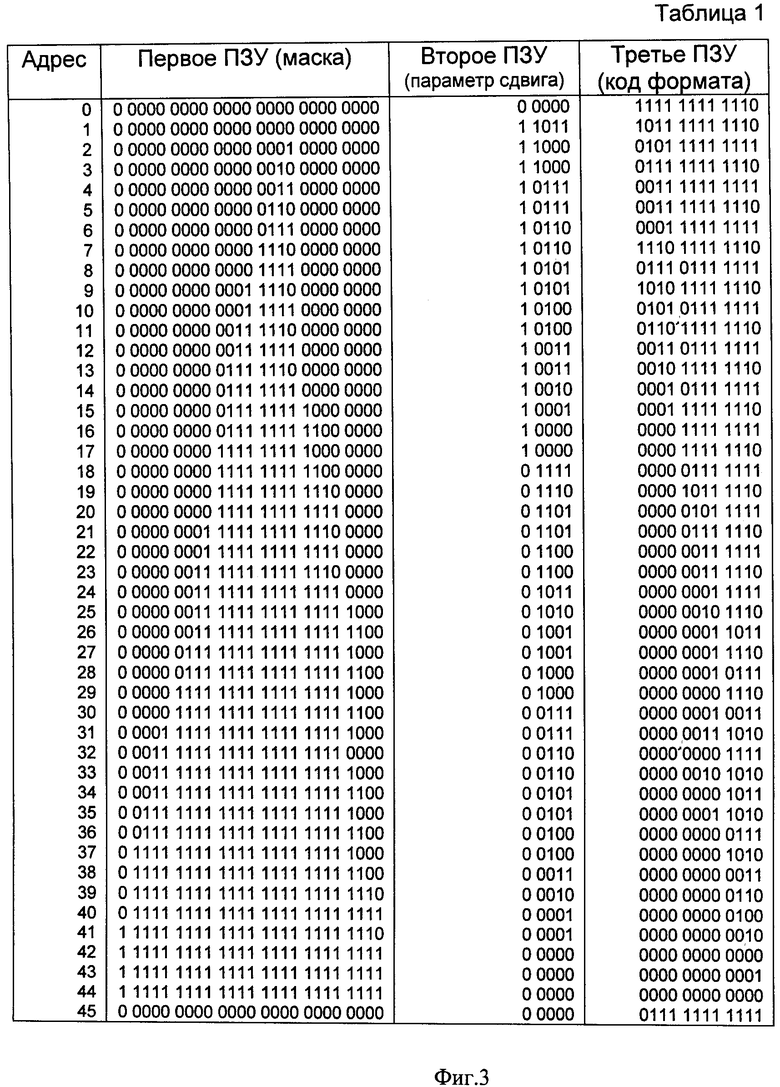

На фиг.3 представлена таблица, отражающая содержимое ПЗУ предлагаемого устройства.

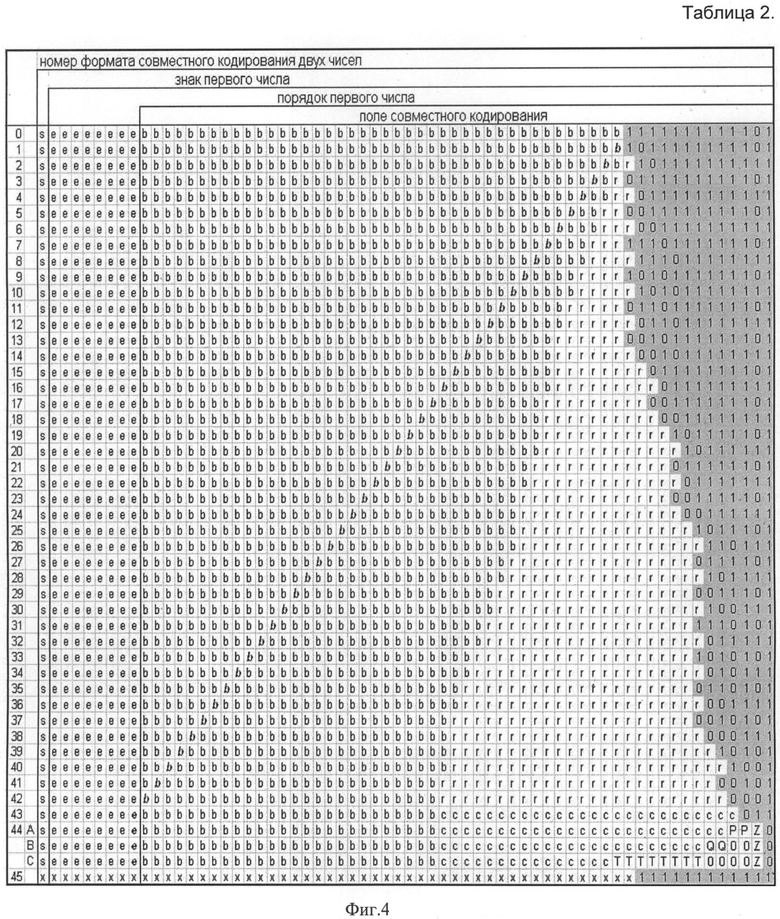

На фиг.4 приведена таблица, иллюстрирующая используемые форматы кодирования.

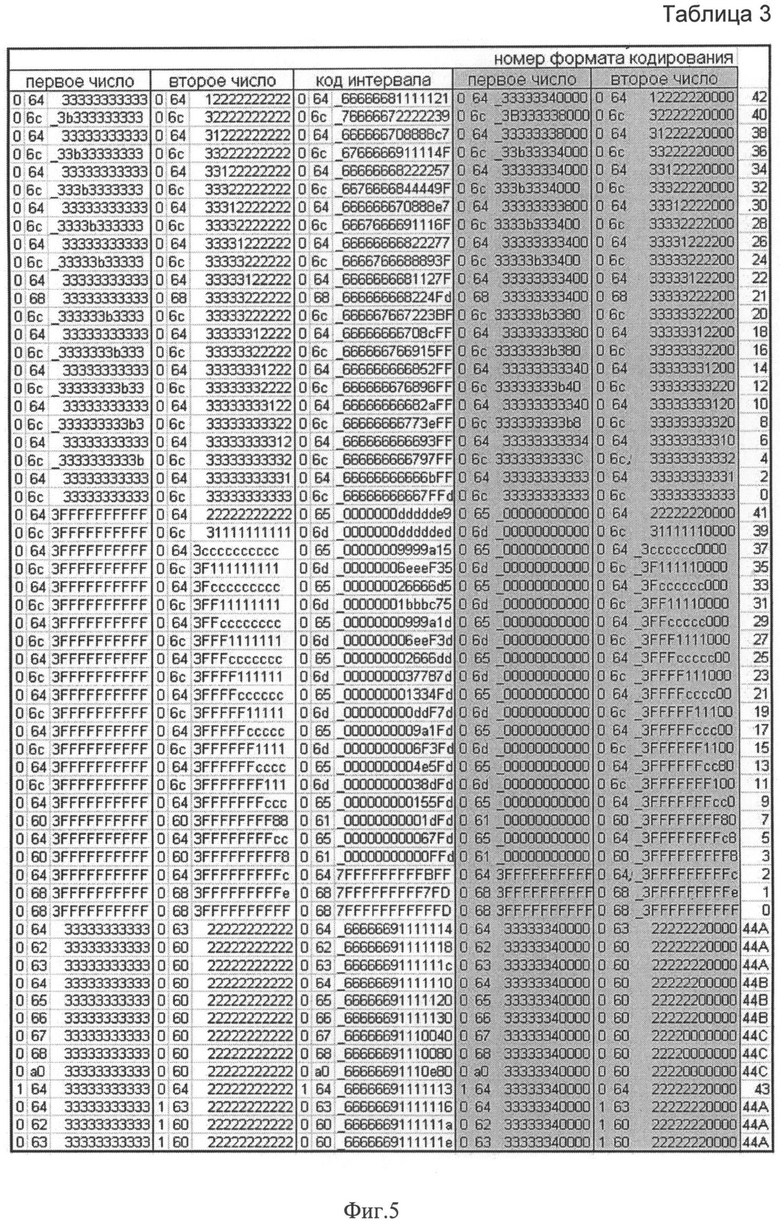

На фиг.5 приведена таблица, содержащая примеры кодирования пар пятидесятиодноразрядных чисел при помощи шестидесятичетырехразрядных кодов.

На фиг.1 и 2 справочно приведены разрядности шин, соединяющих элементы и блоки устройства. Например, надпись /b12 означает, что шина имеет двенадцать разрядов.

Предлагаемое устройство для совместного кодирования границ при интервальных вычислениях содержит первый D-триггер 1, RS-триггер 2 и первый регистр 3, информационный вход, вход установки и вход сброса которых подключены к первому управляющему входу 4 устройства, второй регистр 5 и регистр 6 сдвига, вход разрешения синхросигнала и вход загрузки которых подключены к второму управляющему входу 7 устройства, второй триггер 8, вход разрешения записи которого подключен к третьему управляющему входу 9 устройства, а выход является старшим шестьдесят четвертым разрядом информационного выхода 10 устройства, регистр мультиплексор 11, первый информационный вход которого подключен к пятидесяти младшим разрядам первого информационного входа 12 устройства, пятьдесят первый разряд которого соединен с информационным входом второго триггера 8, младшие сорок два разряда второго информационного входа 13 устройства соединены с параллельным информационным входом регистра 6 сдвига, при этом разряды с сорок третьего по пятьдесят первый второго информационного входа устройства соединены с информационным входом второго регистра 5, входы синхронизации всех триггеров и регистров подключены к входу 14 синхронизации устройства; выход первого регистра 3 соединен с адресными входами первого 15, второго 16, третьего 17 блоков ПЗУ и первым входом первого блока сравнения 18, восемь младших разрядов выхода второго регистра 5 соединены с входом вычитаемого первого вычитателя 19 и с входами первого элемента «ИЛИ» 20, выход которого соединен с последовательным входом регистра 6 сдвига; выход регистра мультиплексора 11 соединен с первым входом первого сумматора 21, при этом восемь старших разрядов упомянутого выхода соединены с входом уменьшаемого первого вычитателя 19 и являются разрядами, с пятьдесят шестого по шестьдесят третий, информационного выхода 10 устройства; второй вход первого сумматора 21, как и инверсные входы первой 22 группы элементов «И» подключены к шестнадцати старшим разрядам двадцатипятиразрядного выхода первого блока ПЗУ 15, а инверсные входы второй 23 группы элементов «И» подключены к пятнадцати старшим разрядам выхода первого блока ПЗУ 15, выход второй группы элементов «И» 23 подключен к пятнадцати младшим разрядам второго информационного входа регистра мультиплексора 11, сорок второй разряд входа регистра мультиплексора обнулен, а разряды с шестнадцатого по сорок первый и разряды с сорок третьего по пятидесятый упомянутого входа подключены к разрядам с семнадцатого по сорок второй и разрядам с сорок третьего по пятидесятый выхода первого сумматора 21, при этом разряды с семнадцатого по сорок второй выхода первого сумматора 21 являются разрядами с тридцатого по пятьдесят пятый информационного выхода 10 устройства; старшие двадцать пять разрядов управляющего входа группы 24 однобитных мультиплексоров подключены к выходу блока ПЗУ 15, а выход группы 24 мультиплексоров является разрядами со второго по двадцать девятый информационного выхода 10 устройства, выход первого вычитателя 19 соединен с первым входом второго блока сравнения 25 и входом уменьшаемого второго вычитателя 26, на вход вычитаемого которого заведено константное значение «3», при этом на второй вход второго блока сравнения 25 заведено константное значение «1»; входы первого элемента суммирования по модулю два 27 подключены к выходу второго D-триггера 8 и к старшему разряду выхода второго регистра 5; вход уменьшаемого третьего вычитателя 28 подключен к сорока двум младшим разрядам выхода первого сумматора 21, при этом шестнадцать младших разрядов входа вычитаемого подключены к выходу первой группы элементов «И» 22, а двадцать шесть старших разрядов упомянутого входа подключены к старшим разрядам выхода регистра 6 сдвига, выход третьего вычитателя 28 соединен с сорока двумя младшими разрядам входа приоритетного шифратора 30, при этом сорок один младший разряд выхода третьего вычитателя 28 соединен с информационным входом сдвигателя 31, пятиразрядный управляющий вход которого подключен к выходу второго блока ПЗУ 16, а двадцатипятиразрядный выход соединен с первым информационным входом первого мультиплексора 32, при этом выход приоритетного шифратора соединен с информационным входом первого регистра 3 и вторым входом первого блока сравнения 18; выход «равно» второго блока сравнения 25 соединен с входом первого элемента «И» 33, другой вход которого подключен к инверсному выходу второго элемента «ИЛИ» 34, и входом второго элемента «И» 35, другой вход которого подключен к сорок второму разряду выхода регистра мультиплексора 11, при этом входы второго элемента «ИЛИ» 34 подключены к выходу первого элемента суммирования по модулю два 27 и сорок второму разряду выхода регистра мультиплексора 11; выход «больше» второго блока сравнения 25 соединен с входом третьего элемента «ИЛИ» 36, другие входы которого подключены к выходам второго 35 и третьего 37 элементов «И», выход соединен с сорок четвертым разрядом входа приоритетного шифратора 30, первым и вторым разрядами управляющего входа группы 24 мультиплексоров, а инверсный выход является первым разрядом информационного выхода 10 устройства; выход «меньше» второго блока сравнения 25 соединен с входом четвертого элемента «И» 38 и с инверсным входом третьего элемента «И» 37, другие входы которых подключены к выходу первого элемента суммирования по модулю два 27; устройство также содержит второй элемент суммирования по модулю два 39, входы которого подключены к сорок третьим разрядам выходов регистра мультиплексора 11 и первого сумматора 21, пятый элемент «И» 40, входы которого подключены к выходам первого элемента «И» 33 и первого D-триггера 1, шестой элемент «И» 41, входы которого подключены к выходам RS-триггера 2 и второго элемента суммирования по модулю два 39, четвертый элемент «ИЛИ» 42, входы которого подключены к выходам третьего элемента «ИЛИ» 36 и четвертого элемента «И» 38, а выход соединен с управляющим входом первого мультиплексора 32 и третьим разрядом управляющего входа группы 24 мультиплексоров, седьмой элемент «И» 43, входы которого подключены к выходу шестого элемента «И» 41 и к инверсному выходу четвертого элемента «ИЛИ» 42, пятый элемент «ИЛИ» 44, входы которого подключены к третьему управляющему входу 9 устройства и к выходу шестого элемента «И» 41, а выход соединен с входом разрешения синхросигнала регистра мультиплексора 11, шестой элемент «ИЛИ» 45, один вход которого подключен к второму управляющему входу 7 устройства, два других входа подключены к выходам пятого 40 и седьмого 43 элементов «И», а выход соединен с входом разрешения синхросигнала регистра 6 сдвига и входом седьмого элемента «ИЛИ» 46, другие входы которого подключены к первому управляющему входу 4 устройства, выходу первого D-триггера 1, выходу «не равно» первого блока сравнения 18, при этом инверсный вход подключен к выходу RS-триггера 2, а инверсный выход соединен с входом сброса RS-триггера 2 и является выходом 47 готовности устройства, четвертый вычитатель 48, чей вход уменьшаемого подключен к выходу второго вычитателя 26, а на вход вычитаемого заведено константное значение «3», восьмой 49 и девятый 50 элементы «ИЛИ», входы которых подключены к восьмиразрядным выходам второго 26 и четвертого 48 вычитателей соответственно, инверсные входы и вход десятого элемента «ИЛИ» 51 подключены к выходу восьмого элемента «ИЛИ» 49, инверсному выходу займа второго вычитателя 26 и выходу четвертого элемента «И» 38, а выход десятого элемента «ИЛИ» 51 соединен с входом одиннадцатого элемента «ИЛИ» 52, входом восьмого элемента «И» 53, инверсным входом девятого элемента «И» 54 и инверсным входом обнуления выхода второго мультиплексора 55; выход восьмого элемента «И» 53 соединен с управляющим входом третьего мультиплексора 56 и первым входом десятого элемента «И» 57, а инверсный вход восьмого элемента «И» 53, как и инверсный вход обнуления выхода третьего мультиплексора 56, подключен к выходу четвертого элемента «И» 38; инверсные входы одиннадцатого элемента «ИЛИ» 52 подключены к выходу девятого элемента «ИЛИ» 50 и инверсному выходу займа четвертого вычитателя 48, а выход и инверсный выход одиннадцатого элемента «ИЛИ» 52 соединены с входом девятого элемента «И» 54 и управляющим входом четвертого мультиплексора 58; первый информационный вход третьего мультиплексора 56 подключен к семнадцатому разряду выхода регистра 6 сдвига, а второй информационный вход подключен к второму разряду выхода первого вычитателя 19, причем первый разряд упомянутого выхода соединен с вторым входом десятого элемента «И» 57; первый информационный вход второго мультиплексора 55 подключен к восемнадцатому и девятнадцатому разрядам выхода регистра 6 сдвига, второй информационный вход подключен к первому и второму разрядам выхода второго вычитателя 26, а управляющий вход второго мультиплексора 55 подключен к выходу девятого элемента «И» 54; первый информационный вход четвертого мультиплексора 58 подключен к разрядам с двадцатого по двадцать седьмой выхода регистра 6 сдвига, а второй информационный вход подключен к восьмиразрядному выходу четвертого вычитателя 48; третья группа 59 элементов «И», первые входы которых подключены к выходу четвертого элемента «И» 38, а вторые входы подключены к выходу десятого элемента «И» 57 и выходу третьего мультиплексора 56; при этом первые два разряда второго информационного входа первого мультиплексора 32 подключены к выходу второго мультиплексора 55, разряды с третьего по десятый подключены к выходу четвертого мультиплексора 58, а разряды с одиннадцатого по двадцать пятый упомянутого входа подключены к разрядам с двадцать восьмого по сорок второй выхода регистра 6 сдвига, разряды с первого по двенадцатый первого информационного входа группы 24 мультиплексоров подключены к выходу третьего блока ПЗУ 17, а разряды с тринадцатого по двадцать восьмой подключены к шестнадцати младшим разрядам выхода первого сумматора 21; первый разряд второго информационного входа группы 24 мультиплексоров подключен к выходу первого элемента суммирования по модулю два 27 второй и третий разряды подключены к выходу третьей группы элементов «И» 23, а разряды с четвертого по двадцать восьмой подключены к выходу первого мультиплексора 32.

Работа устройства начинается с загрузки и установки триггеров 1, 2, 3, 5, 6, 8, 11. На первый информационный вход 12 устройства подается первое число, соответствующее не меньшей по абсолютному значению границе интервала. На второй информационный вход 13 устройства подается второе число, соответствующее не большей по абсолютному значению границе интервала.

Если первое число положительное, оно является верхней границей арифметического интервала. Если первое число отрицательное, оно является нижней границей интервала.

Загрузка по первому информационному входу 12 сопровождается стробом на третьем управляющем входе 9 устройства, а загрузка по второму информационному входу 13 сопровождается стробом на втором управляющем входе 7 устройства. Строб на первом управляющем входе 4 устройства инициирует совместное кодирование двух чисел.

Строб на первом управляющем входе 4 устройства может поступить позже стробов на втором 7 и третьем 9 управляющих входах или одновременно с ними.

Как первое, так и второе число имеют знак, восьмиразрядный порядок и сорокадвухразрядную мантиссу.

Форматы, согласно которым предлагаемое устройство осуществляет кодирование арифметических интервалов, проиллюстрированы таблицей 2, представленной на фиг.4.

Если первое и второе число имеют одинаковые знаки и порядки, кодирование осуществляется согласно формату, имеющему номер от «0» до «42».

Если числа имеют одинаковые знаки, порядок второго числа на единицу меньше, чем порядок первого числа, и старший (после подразумеваемой единицы) разряд мантиссы первого числа равен нулю - кодирование осуществляется по одному из форматов «1» - «42».

Если порядки первого и второго числа, как до, так и после округления равны, а знаки чисел отличаются - кодирование осуществляется согласно формату «43».

Во всех остальных случаях кодирование осуществляется согласно формату номер «44» и его подвидам A, D, С.

При кодировании по форматам «3» - «44» производится округление первого и второго числа. При округлении используется маска, записанная в первом ПЗУ 15.

Округление первого числа выполняется в первом сумматоре 21. Корректность работы устройства при последовательных округлениях обеспечивается маскированием округленных разрядов при помощи второй группы 23 элементов «И». Округление второго числа, заключающееся в маскировании нужного числа младших разрядов мантиссы, осуществляется первой группой элементов «И» 22. Если округление приводит к увеличению порядка первого числа, в регистре мультиплексоре 11 выполняется операция нормализации первого числа, а в регистре 6 сдвига выполняется операция, соответствующая выравниванию порядков чисел. Сигнал об изменении порядка первого числа при его округлении вырабатывается элементом 39 суммирования по модулю два. Результат вычитания мантисс поступает на приоритетный шифратор 30, который вырабатывает следующий адрес обращения к блокам ПЗУ, соответствующий номеру формата кодирования.

На нужные позиции, в результирующем коде, значащие биты разности мантисс подаются посредством сдвигателя 31, первого мультиплексора 32 и группы мультиплексоров 24, при этом значение параметра сдвига определяется числом, выбираемым из второго блока ПЗУ 16.

Процесс кодирования заканчивается, в случае если в очередном такте работы устройства не происходит изменение порядка первого числа и не изменяется адрес обращения к блокам 15, 16, 17 ПЗУ. Отсутствие изменения порядка сигнализируется нулевым уровнем на выходе второго элемента суммирования по модулю два 39. Отсутствие изменения адреса обращения к ПЗУ сигнализируется нулевым уровнем на выходе первого блока сравнения 18.

Кодированный арифметический интервал содержит знак первого числа s, за которым следует восьмиразрядный порядок (округленного) первого числа, обозначенный как ееееееее. Следующие разряды кода содержат разряды мантиссы первого числа, обозначенные как b. Число представленных в коде разрядов мантиссы первого числа зависит от номера формата, использованного при кодировании.

Формат номер «0» используется для кодирования точных чисел (не подвергавшихся округлению). В таком случае, первое и второе числа арифметического интервала равны.

Формат номер «1» используется в том случае, если разность между первым и вторым числом может быть представлена единицей в младшем разряде мантиссы.

Через b обозначены старшие (после округления) разряды мантиссы первого числа, а через r обозначены разряды разности первого и второго чисел. Выделенной буквой b в таблице 2 обозначена позиция подразумеваемой единицы разности первого и второго чисел.

При кодировании по форматам «43» и «44» через с обозначены ставшие разряды мантиссы второго числа.

Если знак второго числа отличается от знака первого числа, при кодировании по формату «44» значение Z полагается равным 1, а при равенстве знаков двух чисел Z полагается равным 0.

Формат «44А» применяется, если разность порядков первого и второго числа равна 1, 2 или 3. Эта разность кодируется битами, обозначенными как PP. Формат «44В» применяется, при разности порядков первого и второго числа от 4 до 6. Эта разность кодируется битами, обозначенными как QQ, с добавлением подразумеваемого числа 3. Формат «44С» применяется, при разности порядков первого и второго числа более 6. Эта разность кодируется битами, обозначенными как ТТТТТТТТ, с добавлением подразумеваемого числа 6. Заметим, что при кодировании по формату «44» разрядность мантиссы первого числа равна двадцати шести. В формате «44С» разрядность мантиссы второго числа равна двадцати пяти, при двадцати трех разрядах в противопоставляемых устройствах. В форматах «44В» и «44С» разрядность мантиссы второго числа составляет 23 и 15 соответственно. Следовательно, только при кодировании по формату «44С» точность представления арифметических интервалов может оказаться меньше, чем в противопоставляемых устройствах.

Выбор одного из подвидов формата «44» осуществляется при помощи первого 19, второго 26 и четвертого 48 вычитателей и ассоциированной с ними логики.

Формирование совместного шестидесятичетырехразрядного кода осуществляется при помощи первого 32, второго 55, третьего 56 и четвертого 58 мультиплексоров, а также группы однобитных мультиплексоров 24.

Формирование результирующего кода занимает 2-4 такта работы устройства.

В таблице 3, на фиг.5, приведены примеры работы устройства. Первое и второе число представлены знаком, восьмибитным порядком и сорокадвухразрядной мантиссой. Порядок и мантисса записаны в шестнадцатеричной системе. Кодированный шестидесятичетырехразрядный арифметического интервала имеет знак, совпадающий со знаком первого числа, восьмиразрядный порядок, совпадающий с порядком округленного первого числа и пятидесятипятиразрядный совместный код. Порядок и совместный код записаны в шестнадцатеричной системе. В затененной области таблицы 3 представлены подразумеваемые значения декодированных первого и второго чисел.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Устройство для определения фазы спектральных составляющих | 1982 |

|

SU1080148A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах для осуществления вычислений в формате с плавающей запятой. Техническим результатом является увеличение точности запоминаемых результатов интервальных вычислений в формате с плавающей запятой, при сохранении суммарной разрядности кода верхней и нижней границ арифметического интервала. Устройство содержит триггеры, регистры, ПЗУ, вычитатели, сумматоры, мультиплексоры, сдвигатели, блоки сравнения, сумматоры по модулю два, элементы И, ИЛИ, приоритетный шифратор. 5 ил.

Устройство совместного кодирования границ при интервальных вычислениях, характеризующееся тем, что содержит первый D-триггер, RS-триггер и первый регистр, информационный вход, вход установки и вход сброса которых подключены к первому управляющему входу устройства, второй регистр и регистр сдвига, вход разрешения синхросигнала и вход загрузки которых подключены к второму управляющему входу устройства, второй триггер, вход разрешения записи которого подключен к третьему управляющему входу устройства, а выход является старшим шестьдесят четвертым разрядом информационного выхода устройства, регистр мультиплексор, первый информационный вход которого подключен к пятидесяти младшим разрядам первого информационного входа устройства, пятьдесят первый разряд которого соединен с информационным входом второго триггера, младшие сорок два разряда второго информационного входа устройства соединены с параллельным информационным входом регистра сдвига, при этом разряды с сорок третьего по пятьдесят первый второго информационного входа устройства соединены с информационным входом второго регистра, входы синхронизации всех триггеров и регистров подключены к входу синхронизации устройства; выход первого регистра соединен с адресными входами первого, второго, третьего блоков ПЗУ и первым входом первого блока сравнения, восемь младших разрядов выхода второго регистра соединены с входом вычитаемого первого вычитателя и с входами первого элемента «ИЛИ», выход которого соединен с последовательным входом сдвигового регистра; выход регистра мультиплексора соединен с первым входом первого сумматора, при этом восемь старших разрядов упомянутого выхода соединены с входом уменьшаемого первого вычитателя и являются разрядами, с пятьдесят шестого по шестьдесят третий, информационного выхода устройства; второй вход первого сумматора, как и инверсные входы первой группы элементов «И» подключены к шестнадцати старшим разрядам двадцатипятиразрядного выхода первого блока ПЗУ, а инверсные входы второй группы элементов «И» подключены к пятнадцати старшим разрядам выхода первого блока ПЗУ, выход второй группы элементов «И» подключен к пятнадцати младшим разрядам второго информационного входа регистра мультиплексора, сорок второй разряд входа регистра мультиплексора обнулен, а разряды с шестнадцатого по сорок первый и разряды с сорок третьего по пятидесятый упомянутого входа подключены к разрядам с семнадцатого по сорок второй и разрядам с сорок третьего по пятидесятый выхода первого сумматора, при этом разряды с семнадцатого по сорок второй выхода первого сумматора являются разрядами с тридцатого по пятьдесят пятый информационного выхода устройства; старшие двадцать пять разрядов управляющего входа группы однобитных мультиплексоров подключены к выходу блока ПЗУ, а выход группы мультиплексоров является разрядами со второго по двадцать девятый информационного выхода устройства, выход первого вычитателя соединен с первым входом второго блока сравнения и входом уменьшаемого второго вычитателя, на вход вычитаемого которого заведено константное значение «3», при этом на второй вход второго блока сравнения заведено константное значение «1»; входы первого элемента суммирования по модулю два подключены к выходу второго D-триггера и к старшему разряду выхода второго регистра; вход уменьшаемого третьего вычитателя подключен к сорока двум младшим разрядам выхода первого сумматора, при этом шестнадцать младших разрядов входа вычитаемого подключены к выходу первой группы элементов «И», а двадцать шесть старших разрядов упомянутого входа подключены к старшим разрядам выхода регистра сдвига, выход третьего вычитателя соединен с сорока двумя младшими разрядам входа приоритетного шифратора, при этом сорок один младший разряд выхода третьего вычитателя соединен с информационным входом сдвигателя, пятиразрядный управляющий вход которого подключен к выходу второго блока ПЗУ, а двадцатипятиразрядный выход соединен с первым информационным входом первого мультиплексора, при этом выход приоритетного шифратора соединен с информационным входом первого регистра и вторым входом первого блока сравнения; выход «равно» второго блока сравнения соединен с входом первого элемента «И», другой вход которого подключен к инверсному выходу второго элемента «ИЛИ», и входом второго элемента «И», другой вход которого подключен к сорок второму разряду выхода регистра мультиплексора, при этом входы второго элемента «ИЛИ» подключены к выходу первого элемента суммирования по модулю два и сорок второму разряду выхода регистра мультиплексора; выход «больше» второго блока сравнения соединен с входом третьего элемента «ИЛИ», другие входы которого подключены к выходам второго и третьего элементов «И», выход соединен с сорок четвертым разрядом входа приоритетного шифратора, первым и вторым разрядами управляющего входа группы мультиплексоров, а инверсный выход является первым разрядом информационного выхода устройства; выход «меньше» второго блока сравнения соединен с входом четвертого элемента «И» и с инверсным входом третьего элемента «И», другие входы которых подключены к выходу первого элемента суммирования по модулю два 27; устройство также содержит второй элемент суммирования по модулю два, входы которого подключены к сорок третьим разрядам выходов регистра мультиплексора и первого сумматора, пятый элемент «И», входы которого подключены к выходам первого элемента «И» и первого D-триггера, шестой элемент «И», входы которого подключены к выходам RS-триггера и второго элемента суммирования по модулю два, четвертый элемент «ИЛИ», входы которого подключены к выходам третьего элемента «ИЛИ» и четвертого элемента «И», а выход соединен с управляющим входом первого мультиплексора и третьим разрядом управляющего входа группы мультиплексоров, седьмой элемент «И», входы которого подключены к выходу шестого элемента «И» и к инверсному выходу четвертого элемента «ИЛИ», пятый элемент «ИЛИ», входы которого подключены к третьему управляющему входу устройства и к выходу шестого элемента «И», а выход соединен с входом разрешения синхросигнала регистра мультиплексора, шестой элемент «ИЛИ», один вход которого подключен к второму управляющему входу устройства, два других входа подключены к выходам пятого и седьмого элементов «И», а выход соединен с входом разрешения синхросигнала регистра сдвига и входом седьмого элемента «ИЛИ», другие входы которого подключены к первому управляющему входу устройства, выходу первого D-триггера, выходу «не равно» первого блока сравнения, при этом инверсный вход подключен к выходу RS-триггера, а инверсный выход соединен с входом сброса RS-триггера и является выходом готовности устройства, четвертый вычитатель, чей вход уменьшаемого подключен к выходу второго вычитателя, а на вход вычитаемого заведено константное значение «3», восьмой и девятый элементы «ИЛИ», входы которых подключены к восьмиразрядным выходам второго и четвертого вычитателей соответственно, инверсные входы и вход десятого элемента «ИЛИ» подключены к выходу восьмого элемента «ИЛИ», инверсному выходу займа второго вычитателя и выходу четвертого элемента «И», а выход десятого элемента «ИЛИ» соединен с входом одиннадцатого элемента «ИЛИ», входом восьмого элемента «И», инверсным входом девятого элемента «И» и инверсным входом обнуления выхода второго мультиплексора; выход восьмого элемента «И» соединен с управляющим входом третьего мультиплексора и первым входом десятого элемента «И», а инверсный вход восьмого элемента «И», как и инверсный вход обнуления выхода третьего мультиплексора, подключен к выходу четвертого элемента «И»; инверсные входы одиннадцатого элемента «ИЛИ» подключены к выходу девятого элемента «ИЛИ» и инверсному выходу займа четвертого вычитателя, а выход и инверсный выход одиннадцатого элемента «ИЛИ» соединены с входом девятого элемента «И» и управляющим входом четвертого мультиплексора; первый информационный вход третьего мультиплексора подключен к семнадцатому разряду выхода регистра сдвига, а второй информационный вход подключен к второму разряду выхода первого вычитателя, причем первый разряд упомянутого выхода соединен с вторым входом десятого элемента «И»; первый информационный вход второго мультиплексора подключен к восемнадцатому и девятнадцатому разрядам выхода регистра сдвига, второй информационный вход подключен к первому и второму разрядам выхода второго вычитателя, а управляющий вход второго мультиплексора подключен к выходу девятого элемента «И»; первый информационный вход четвертого мультиплексора подключен к разрядам с двадцатого по двадцать седьмой выхода регистра сдвига, а второй информационный вход подключен к восьмиразрядному выходу четвертого вычитателя; третья группа элементов «И», первые входы которых подключены к выходу четвертого элемента «И», а вторые входы подключены к выходу десятого элемента «И» и выходу третьего мультиплексора; при этом первые два разряда второго информационного входа первого мультиплексора подключены к выходу второго мультиплексора, разряды с третьего по десятый подключены к выходу четвертого мультиплексора, а разряды с одиннадцатого по двадцать пятый упомянутого входа подключены к разрядам с двадцать восьмого по сорок второй выхода регистра сдвига, разряды с первого по двенадцатый первого информационного входа группы мультиплексоров подключены к выходу третьего блока ПЗУ, а разряды с тринадцатого по двадцать восьмой подключены к шестнадцати младшим разрядам выхода первого сумматора; первый разряд второго информационного входа группы мультиплексоров подключен к выходу первого элемента суммирования по модулю два, второй и третий разряды подключены к выходу третьей группы элементов «И», а разряды с четвертого по двадцать восьмой подключены к выходу первого мультиплексора.

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЙ | 1991 |

|

RU2006929C1 |

| US 6658443 B1, 02.12.2003 | |||

| US 7069288 B2, 27.06.2006 | |||

| US 6779006 B1, 17.08.2004 | |||

| Устройство для умножения трех чисел | 1984 |

|

SU1226446A1 |

Авторы

Даты

2013-10-27—Публикация

2012-08-21—Подача