12

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах высокопроизводительных машин.

Цель изобретения - повышение про- изводительности устройства.

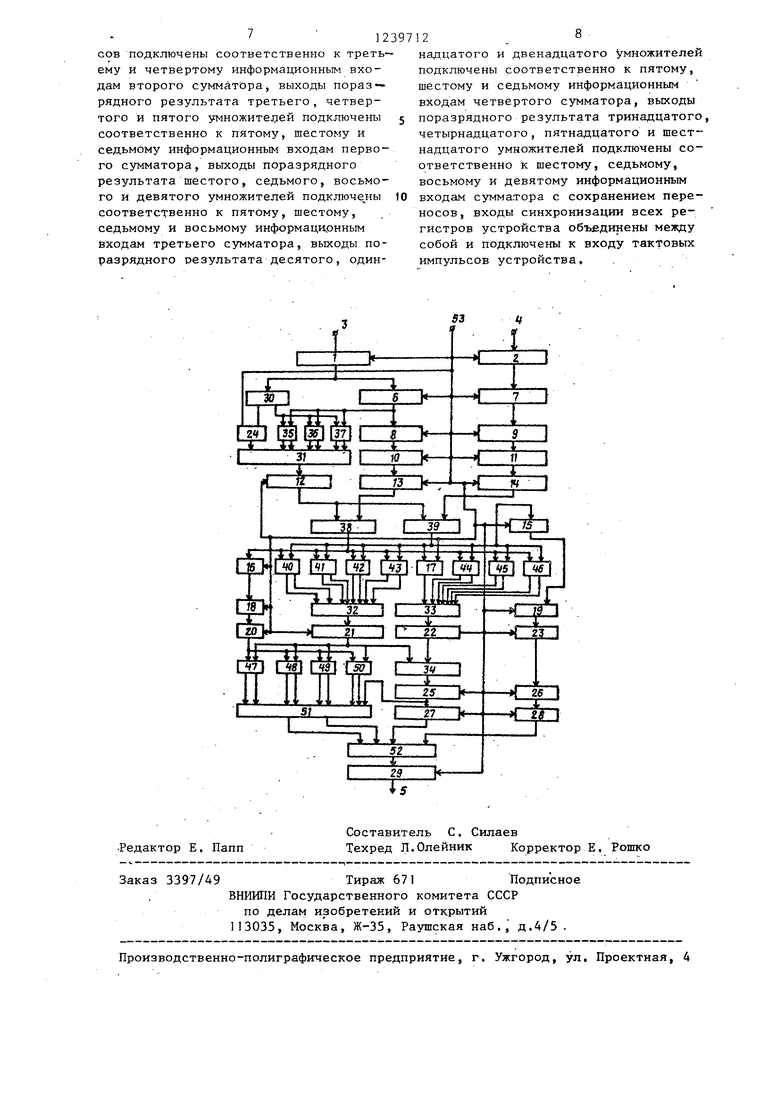

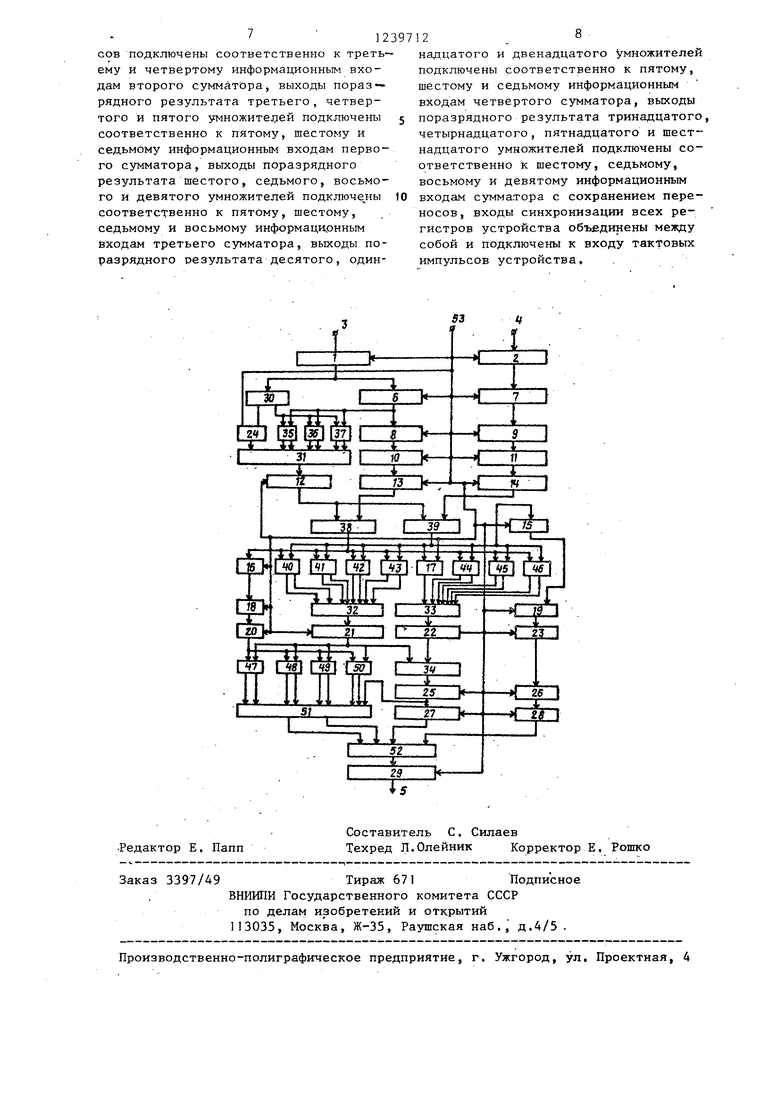

Схема устройства деления сорокавосьмиразрядных, чисел представлена на чертеже.

Устройство содержит регистр 1 де- лителя, регистр 2 делимого, входные шины 3 и 4 делителя и делимого, выходную шину 5 результата, регистры 6- 28, регистр 29 результата, блок 30 памяти, сумматоры 31-34, умножители 35-50, сумматор 51 с сохранением переносов и сумматор 52, входную шину 53 тактовых импульсов устройства ,

Устройство работает следующим образом,

Предлагаемое устройство является конвейерным, в связи с чем оно . поделено на части - сегменты, причем каждому сегменту соответствует комби национный блок, осуществляющий опре- деленный этап обработки, и регистровая память, сл ужащая для промежуточного хранения информации,

. Для обеспечения точности частного в 47 верных двоичных разрядах за две итерации (второго и третьего порядка точности соответственно) необходимо иметь заранее вычисленное начальное приближение (Хб) с не менее, чем семью верными двоичными разрядами, Начальные приближения сведены в таблицу, из которой они выбираются при помощи восьми разрядов нормализованного делителя, расположенных справа от старшей единицы. Таблица началь- ньгк приближений хранится в блоке 30 памяти.-

На вход блока 30 с регистра 1 пос тупает значение делителя (С), стар

шие разряды которого адресуют в таб

лице начальных приближений девятиразрядное значение Ха, поступающее на первый выход блока 30 памяти, на второй выход которого выбирается 18- разрядное значение квадрата началь- ного приближения (Х).

Формирование и суммирование частичных произведений, разделенных на три группы, осуществляется при помо- ци первого, второго и третьего умно- жителей 35 - 37, на вторые входы которых подается множимое С, На первые входы-умножителей 35 - 37 подаются

5

tO 15 20

- 25 30 -jj 40.

45

55

12 .

соответственно первая, вторая и третья шестираэрядные группы множителя Х, На выходах первого, второго и третьего умножителей 35-- 37 образуются три двухрядных кода.-Далее полученные двухрядные коды суммируются совместно с удвоенным значением начального приближения в обратном коде (-2X,j) , поступающего с регистра 24 на сумматор 31. .На выходе сумматора 31 образуется выражение ( + Xjj С ), которое запоминается в регистре 12 в обратном коде.

Восемнадцать стар01их разрядов выражения

-f 2Х 5 Хо С,

где Х - первое приближение обратной величины делителя С, с инверсного выхода регистра 12 поступают на первый вход умножителя 38, на второй вход которого подается А8-разрядное значение С, задержанное на регистрах 6, 8р 10 и 13. Производится умножение СХ,( . На вькод умножителя 38 пос-, тупает 38-разрядная величина 1-СЗ, получаемая путем отсечения шестнад-. цати старших и двенадцати младших разрядов произведения СХ.

В блоке 39 осуществляется умножение АХ , где А - делимое. На первьгй вход блока 39 : жножения поступает величина Х, на второй вход с регистра 2 делимого через регистры 7, 9, 11 и 14 подается 48-разряднле значение- А, На выходе блока 39 образуется путем, отсечения десяти младших разрядов 56-разрядное значение АХ,

Обратная величина делителя с точностью в 47 верных разрядах( может быть вычислена при помощи выражения

Xj X, + Х (1-СХ) +

+ x i-CKi) (J-cXi) (О

Для получения частного В необходимо Xj :)гмножить на делимое А:

В АХ а АХ + АХ (1-СХ) +

AX d-CX Xl-CXp. (2)

С целью увеличения быстродействия работы устройства деления при уело-. ВИИ достижения точности результата в 47 EiepHbrx двоичных разрядов выражение 2 преобразуется следующим образом:

АХ, (АХ) + (АХ). + Д X

3 12397

X (I-CX,) + АХ .(1-СХ, ); (СХ ). (3)

где (АХ){., - старшие 30 разрядов выражения АХ ;

(АХ )(vi - младшие. 26 разрядов выражения АХ ;

д5, старшие АО разрядов выражения

(1-СХ) - старшие 24 разряда выражения (1-СХ). iQ На умножителях 40,- 43 и на сум- I маторе 32 0 уществляется вычисление выражения AX(l-CX)g .

На вторые входы умножителей 40 - 43 поступает множимое АХ , На-первые je входы умножителей подаются соответственно- первая, вторая, третья и четвертая шестиразрядные группы множителя (l-CXi)c. На выходе умножителей 40 - 43 образуются четыре двухрядных . кода, которые суммируются на сумматоре 32, на выход которого пост-упает 40-разрядное выражение АХ () , которое запоминается в буферном регистре 2, На регистре 17, умножите- 25 лях 44-- 46 и на сумматоре 33 вычисляется выражение .

- АХ, (1-СХ)„ + (АХ), где (l-CXi)M (1-СХ) - (1-СХр,,

На первые входы умножителей 44- - 46 поступают 14 с младших разрядов выражения (1 -СХ,() ,.

На вторые входы, умножителей 44-46 поступает множимое АХ . На первые

входы умножителей 44 и 45 подаются соответственно первая и вторая шестиразрядные группы множителя (1-СХу()у на первый вход умножителя 4i5 поступают два младших разряда (l-CX)j. На выходе з ножителей 44 - 46 образуются три двухрядных кода, которые

(Суммируются совместно с двадцатью пятью младшими разрядами величины АХ с регистра 17 на сзп маторе 33, на выход которого поступает выражение

АХ .(1-СХ)„ -н (АХ)«,

-которое запоминается в регистре 22,

На сумматор 34 осуществляется сложение величин АХ .(1-СХ;,)о и Ж (1-СХ )s, -I- (AX,)t)n, которые подаются на первый и второй входы сумматора 34 соответственно с выходов регистров 21 и 22. На вькоде сзгммато.- ра 34 образуется 4С-разрядное выражение + (, которое запоминается в буферном регистре 25.

Q

e 5

0

.

Q

j

12 . . 4

На умножителях 47 - 50.и на сумматоре 51 вычисляется выражение

Ах,.(1-схр. (1-сх) + I AX X

X (1-СХ) + ( ,

где АХ .(1-СХ)(АХх), 25 младших разрядов величины АХ(1-СХ)+

+ (.

На входы -умножителей 47 - 50 подаются соответственно первая, вторая, третья и четвертая шестираз- . рядные группы множитетш (1-СХ), а на вторые - множимое АХ ()с, узлов уг-1ножения 47 - 50, Образуются четыре двухрядных кода, которые суммируются совместно с двадцатью пятью младшими разрядами величины АТ( (-СХ.() + (АХ)н на сумматоре 51 с сохранением переносов, Полученный двухрядный код поступает на первьй и второй входы сумматора 52.

30-разрядное значение (АХ)с задержанное на регистрах 15, 19, 23, 26 и 28, поступает на третий вход сумматора 52, Значение пятнадцати - старших разрядов АХ (1-СХ) + (АХ)м, задержанное на регистре 27, поступает на четвертый вход сумматора 52, с выхода которого сорокавосьмирлзряд- ное значение частного с сорока семью верными разрядами принимается на вы- ХОД.НОЙ регистр 29,

Формула из обретенияУстройство для деления-48-раэряд- ных чисел, содержащее регистр делителя, блок памяти, два умножителя, два сумматора, двадцать один регистр и выходной регистр, причем информаци- онньй вход регистра делителя является входом делителя устройства, выход регистра делителя подключен к адресному входу блока памяти и к информационному входу первого регистра, выход первого регистра подключен к информационному входу второго регистра, выход второго регистра подключен к информационному входу треть.его регистра, выход третьего регистра подключен к информационному входу четвертого регистра, выход первого сумматора подключен к информационному входу пятого регистра, выходы чет- . вертого и пятого .регистров подключены соответственно к первому и вто.рому информационным входам первого ножителя, выход первого умножителя, подключен к информационному входу шестого регистра, выход шестого ре- гистра подключен к информационному входу седьмого регистра, выход седьмого регистра подклзочен к информационному входу восьмого регистра, выход девятого регистра подключен к информационному входу десятого регистра, E; зlxoд десятого регистра под- ключрн к информационному входу один- ,надцатого регистра, выход одиннадцатого регистра подключен к информаци- онному входу двенадцатого регистра выход тринадцатого регистра подключен к, информационному входу четыр- надцато го регистра, выход четырнадцатого регистра подключен к информа- ционн ому входу пятнадцатого регистра выход пятнадцатого регистра подклю.- чек к информационному входу шестнадцатого регистра, выход шестнадцато- го регистра подключен к информацион- ному входу семнадцатого регистра, выход восемнадцатого регистра под- ключен к информационному входу девятнадцатого регистра, выходы семнадцатого и девятнадцатого регистров подключены соответственно к первому и . второму информациционным входам второго сумматора, выход второго сумматора подключен к информационному входу выходного регистра, выход выходного регистра является выходом результата устройства, о т л и ч а- ю щ е е с я тем,,что с целью .пов ы- шения производительности, в него введены регистр делимого, сзтчматора сумматор с сохранением переносов, дв регистра и четырнадцать з ножителей лричем информационный вход двадцать второго регистра подключен к первому информационному выходу блока памяти, первые информационные входы третьего четвертого, и .пятого умножителей подключены к второму информационному выходу блока памяти, вторые информационные входы третьего, четвертого и пятого умножителей подключены к выходу первого регистра, выход двадцать второго регистра и выходы поразрядных переносов третьего,четвертог и пятого умножителей подключены соот ветственно к первому,, второму, третьему и четвертому информационньм вхо цам первого сумматора, вход регистра

s 0 5 о о 5 о

5

делимого является входом делимого, выход регистра делимого подключен к информационному входу девятого регистра первый и второй информационные входы второго умножителя подключены соответственно к выходам пятого и двенадцатого регистров, выход первого умножителя подключен к первым инфор-- мационным .входам шестого седьмого, восьмого,, девятого, десятого, один- - надцатого и двенадцатого умножителей, выход второго умножителя подключен к вторым информационным входам шестого, седьмого, восьмого, девятого, десято. го 5 одиннадцатого и двенадцатого умножителей и к информационным входам двадцать третьего и тринадцатого р.е-. гистров, .выходы поразрядных переносов шестого, седьмого, восьмого .,и-девято- - го Умножителей подключены соответственно к первому, второму, третьему и чат- верто гу информационным входам третьего сумматора, выход двадцать третьего регистра и выходы адресных переносов десятого, одиннадцатого и двенадцатого у1чножителей подключены соответственно к первому,, второму третьему и четвертому информационным входам четвертого сумматора, выход третьего сумматора подключен к информационному входу двадцатого регистра, выход четвертого сумматора подключен к информационному входу двадцать первого регистра, выход восьмого регистра

подключен к первым информационным входам тринадцатого, четырнадцатого j пятнадцатого и шестнадцатого умножи-. т.елей выход двадцатого регистра подключен к вторым информационным входам тринадцатого , четырнадцатого, пятнадцатого и шес тнадцатого умножи .телей и к первому информационному входу пятого су1У1матора, выход двад- дать первого регистра подключен к второму информационному входу пятого сумматора, выход пятого сз мматора подключен к информационному входу, восемнадцатого регистра, первый, второй, третий, четвертый и пятый входы сумматора с сохранением переносов подключены соответственно к выходам поразрядных переносов тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого умножителей и к выходу во-;

.; семнадцатого регистра, выход поразрядных переносов и выход разрядных сумм сумматора с сохранением перено-7 12

GOB подключены соответственно к треть ему и четвертому информационным входам второго сумматора, выходы пораз рядного результата третьего, четвертого и пятого yмнoжитeJзeй подключены соответственно к пятому, шестому и седьмому информационным входам первого сумматора, выходы поразрядного результата шестого, седьмого, восьмого и девятого умножителей подключе 1Ы соответственно к пятому, шестому, седьмому и восьмому информационным входам третьего сумматора, выходы поразрядного результата десятого, один12 . надцатого и двенадцатого умножителей подключены соответственно к пятому, шестому и седьмому информационным входам четвертого сумматора, вьтоды поразрядного результата тринадцатого четырнадцатого, пятнадцатого и шестнадцатого умножителей подключены соответственно к шестому, седьмому, восьмому и девятому информационным входам сумматора с сохранением переносов, входы синхронизации всех регистров устройства объединены между собой и подключены к входу тактовых импульсов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Устройство для деления | 1990 |

|

SU1728860A1 |

| УСТРОЙСТВО ДЛЯ УЧЕТА ЭЛЕКТРОЭНЕРГИИ | 1997 |

|

RU2125269C1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Устройство для вычисления обратной величины 48-разрядных чисел | 1983 |

|

SU1173412A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ НАИМЕНЬШИХ КВАДРАТОВ | 1993 |

|

RU2049354C1 |

Изобретение относи тся к области вычислительной техн.ики и может быть использовано в арифметических устройствах высокопроизводительных цифровых вычислительных мащин в качестве отдельного функционального устройства. Данное устройство представляет, собой конвейер, в связи с чем оно поделено на части-сегменты, причем каждому сегменту конвейера соответствует ком- бинационнЬ1й блок, осуществляющий определенный этан обработки, и регист- ровая память, служащая для промежуточного хранения информации. Положи- -тельный . эффект изобретения состоит в расширении функциональных возможностей устройства, в увеличении быстродействия выполнения операции деления, в повышеш1и точности .частного до 47 верных разрядов и в обеспечении возможности дополнительного распараллеливания -вычислений благодаря освобож- .дению устройства умножения для выполнения своей основной функции. 1 ил. i (Л ГчЭ : со ч1

Tir

52

Редактор Е. Папп

Составитель С. Силаев

Техред Л.Олейник Корректор Е. Рошко

Заказ 3397/49Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Карцев М.А, и Брик Б,А. | |||

| Вычислительные системы и синхронная арифметика | |||

| -М.: Радио и связь, 1981, с.226-230 | |||

| Устройство для вычисления обратной величины 48-разрядных чисел | 1983 |

|

SU1173412A1 |

Авторы

Даты

1986-06-23—Публикация

1984-12-17—Подача