(54) yQTPOnCTBO ДЛЯ РЕШЕНИЯ СИСТЕМ ДИФФЕРЕНЦИАЛЬНЫХ

УРАВНЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем дифференцильных уравнений | 1977 |

|

SU717778A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714406A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU705454A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Субоптимальный нелинейный фильтр | 1990 |

|

SU1714618A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для градуировки датчиков силы | 1989 |

|

SU1682845A1 |

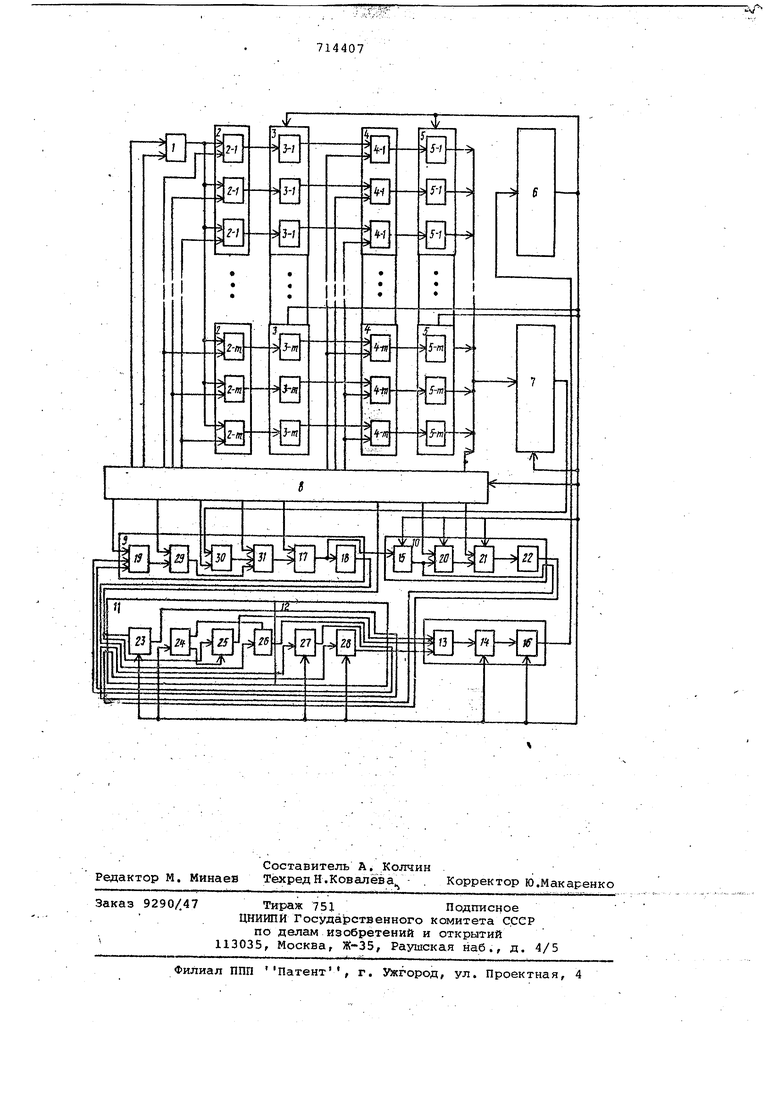

Изобретение относится к области .вычислительной техники и может быть применено для решения.с высокой точностью систем обыкновенных дифференциальных уравнений, например, в системах автоматического регулирования и управления динамическими объектами Известны вычислительные устройства и системы для решения систем обык новенных дифференциальных уравнений, содержащие блоки умножения, суммиров ния, интегрирования, блоки комму -Лто ров, блоки памяти, блоки управления 1. Основным недостатком известной вычис.лительной системы для решения дифференциальных уравнений является сравнительно невысокая точност.ь вычисления вектора искомых неизвестных Наиболее близким по технической сущности к предложенному является устройство для решения систем дифференциальных уравнений, содержащее блок памяти, первый, второй, третий, четвертый и пятый выходы которого подключены соответственно к первому, второму, третьему, четвертому и пятому входам блока реккурентных вычислений, первый выход которого соединен с первьм входом блока памяти и со вхо дом Первого сумматора, выход которого подключен соответственно к первому входу блока сдвига, второй и третий, выходы которого соединены соответственно с шестым и седьмым выходами блока памяти, и к первому входу первого коммутатора, второй вход которог.р соединен с выходом блока сдвига, первый ВЫХ.ОД первого коммутатора подключен к первому входу элемента ИЛИ, выход которого подключен ко входу второго сумматора, выход которого . соединен со входом блока сравнения, выход которого подключен ко Bxojiy блока управления, второй и третий входы элемента ИЛИ соединены соответственно с первьм и вторым выходами второго коммутатора, первый и второй входы которого подключены к первому и второму выходам блока реккурентных вычислений, шестой и седьмой входы которого соединены соответственно со вторым выходом первогокaviMyTaтора и с третьим выходом второго коммутатора, восьмой вход блока реккурентных вычислений подк.точен к выходу первого блока сумматоров, управляюцие входы блока памяти, первого и второго сумматоров, блока сдвига, п.ервого блока сумматоров блока реккурентных вычислений, блока сравнеМия; nepBOjTp и второго коммутаторов, второго блока сумматоров соединены с соответствующими выходами блока управления, группа блоков умножения, блок умножителей 2.; Недостатком известного устройства является невозможность получения решений системы дифференциальных уравнений с произвольным нелинейносч-й. ; . :. ,. ; Целью предложенного изобретения является расширение класса решаемых задач за счет возможности решения ;систем уравнений с произвольным видс нелинейности. Это достигается тем, 1то в устройстве дополнительно введены третий ко мутатор и умножитель. Причем первый и второй входы умножителя подключены к восьмому и девято му вйходам блока памяти, первая груп па выходов которого соединена с первой группой входов группы блоков yiviнШёния, вторая группа входов которой подключена к выходу умножителя, вьвсоды ГРУППЕ блоков, умножения соеди нены со входами второго блока сз мматоров, выходы которого подключены к первой группе входов блока умножителей, вторая -группа входов которого соединена со второй группой выходов блока памяти,выходы блока умножителей подключены ко входам третьего коммутатора, выход которого соединен со ВХОДСЖ1 пёрвого блока сумйаторов и со вторым входсм блока управ ляющий вход третьего коммутатора под ключен к соответствующему выходу бло кауйравленйя; v.; - .Описываемое устройство представле но на чертеже. Оно содержит умножитель 1, группу блоков .2 умножения; (2-l-2 m), блок 3 сумматоров () , блок 4 умножителей () , коммутатор 5, блок б управления, блок 7 сумматоров ,блщ 8 памяти, блок 9 реккурёнтньк вычислений, блок 10 сдвига, коммутаторы 1 12, элемент 13 ИЛИ, сумматоры 14, 15 блок 16 сравнения, умножитель 17, ин вертор 18, элемент 19 ИЛИ, регистры 20, 21, инвертор 22, элемент 23 И триггер 24, элементы 25-28 И, умножи тели 29, 30, сумматор 31. : Работу устройства поясним на ПриMejJe решения систем обыкновенных не;ли1ЙЙных дифференциальных уравнений вида:. .. .qxitj. + ax(t) + By(x(t)) f (t) qt ....,, .. ... „ , . ,., :i:, ;,:;--. x(o) XQ, . ; (€) вектор нейёвестнйГ/ - А,В - матрицы постоянных ксээф фициентов, . (t) - вектор правых частей, у x(t) - нелинейная вёктор-функци.я, t - время, X (0) - значение к(t)пpи t О, ричем , . (x(-ti)l))),v2(K,i(m.- ,)нСх,ш), (2) Ht/ajX w vffi/ajX W п Сх„Л)) S И-з si«e.jX(i)+cosp-x a)) О) (--,1,...,(, 1,2,...,« j ,dj , гРл Постоянные коэффициенты. j f. Решение проводится с помощью -преобразований Тейлера - (M3icvt W 4 0ь . - (i)(...t .-с(.Г f Uj. ЛГ Х,.аи-П f 5) .-aC)-e/sw (i +t-e) л .i Wjjn E-o T йч -ИЬ.ч (е)Хц№ц-ш )--х(1ИУ; bf-i.,, ---W« jXicv ;-- .jX .№)-v. .Ct). (г),J..(г). де U.-rt (k) - дискрета изобра; ясающей Uxia (t) функции. 1A q,-Я компонента, вектора. дискрет (5) изображакнцей вектор, х j (-г) вектор-функции, - д.я компонента вектора iisx дискрет изображающей вектор (f) вектор-функции, - IcsH дискрета изображаю(J) щей г (Г) функции. дискрета изображаюV.-,«.((k) ,Чс щей , (-с) функции, дискрет.а изображаю щ щей ) функции. Ра.б6та вычислительной структуры начинается с выдачи управляющих сигналов из блока 6 управления на управ йййййе вхЪды блока 8 памяти, первого 20 и второго 21 запоминающих регистров . При поступлении этих сигналов происходит считывание из блока 8 памяти и запись в регистры 20 и 21 начальных усло1зий: в регистр 20 заносится значение вектора Хо(0), в регистр. 21 - вектора Х (0) . Одновременно и.з ..блока 8 памяти на соответствуквдие входы блока 9 реккурентных вычислений поступает вектор ХдСО) дискрет. По сигналам управления из блока 6 осуществля ется последовательное считывание из блока 8 памяти на входы блока 7 сумматоров и последовательное суммировани ё в нем (т раз) соответствующих компонентов векторов и., (О ), V., (0), Wjj-j (0) , т,е. вычисЛяются компоненты вектора R:J (0) диск 1рет., . I 1. По сигналам управления из бло.ка б, поступающим на управляющие Bico ды управляющего триггера 24, блока 16 сравнения, блока; 3 сумматоров, блока 7 сумматоров, сумматоров 14. ;и 15, осуществляется установка в .них кодов нуля нулевых. Начальных условий По сигналам управления из блока б управления, поступающим на управя.яюЩие входы элемента 28 И коммутатора 12, инвертированный .вектор(-Х (0)) дискрет с выходов блока 22 инверторов знака через открытый элемент 28 И поступает через э лёмент 13 ИЛИ :на входы сумматора 14. По сигналам (управления, поступающим из блока б управления на упра;вляющие входы сVM: Iaтopa 14, осуществляется суммирование занесенного первоначального в ,. него кода нуля и значения вектора .;(-X,j (0) ) дискрет. ,. -.- /. , , . 2. После этого из блока 8 памяти в блок 9 реккурентных вычис.лёний считываются значения коэффициентов . H(k + 1), вектора F(k) дискрет, компонент матриц (В) и (-Ai, соотв.етс.твенно значение Хр(1) из блока 9 рек- курентных вычислений поступает на- вхо ды блока 8 памяти, cyMMatopa 15 к ксм мутатора 11. По сигналам управления, поступающим из блока 6 на управляю-; щие входы блока 8 памяти и сумматора осуществляется запись полученного .Текущего значения Хр (1 ) вектора дискрет в блоке 8 памяти и суммирование, первоначально занесенного В сумматрр 15 кода нуля с вектором ). Одновременно вектор Хр (1) через открытый еди ничным сигналс 1 управления с йнверсного вькода управляющего триггера 24. элемент 25 И поступает через.элолент 13 ИЛИ навход сумматора 14, в кОТорсм по сигна лам из блока б управления поступающим на управляющие входы сумматора 14, осуществляется вычисление текущего . значения левой части условия: (Хо(1) - Х (0)), поступающей на входы блока 16 сравнения. По сигналам упра.вления из блока 6 осущертвляетря ydTaHOBKa в исходное . (нулевое) состояние блока 3 сумматоров и блока 7 сумматорЪв. При поступлении управляющих сигналов из блока б на управляющие входы блока 16 сравнения осуществляется проверка условия Хо(1) - Х|(0) . Если условие выполнено, то код выполнения условия с выходов блока 16 сравнения п.оступает на входы блока б .управления, после, чего управляющие сигналы с выходов последнего, поступая на управляющие входы элемента 27 И, открывают его,и вектор поступает с выхода блока 10 сдвига на входы блока 9 реккурентных вычислений. Следовательно, в следующем цикле работы- вычислительной структуры на вторые входы первого блока 29 умножителей поступает вектор Х/(0) Xp(k), вместо в.ектора XQ. По сигналам управления, поступающим последовательно во времени на второй 21 и первый 20 запоминающие регистры, осуществляются сдвиг информации(в блоке 10 сдви-i га: вектор Xjj (6) записывается из первого запоминающего регист ра 20 во второй запоминающий регистр 21 вместо вектора Х (0), а в первый,запоминающий регистр 20 записываетсяХ (0) с выходов сумматора 19. Если условие 1И Т достижения конца интервала ий-; тегрирования выполнено,то вычисления останавливаются., в противном случае осуществляется следующий (i+l)ifl цикл работы вычислительной структуры- аналогично описанному ниже, начиная с .пункта 1. .. , . . . Если условие не выполн.ёнб, тоlib сигналам из 6 управления на Г первые и вторые входы умножителя 1 :из блока 8.памяти считываются значе-. ния вектрров дискрет (Ic+l-E) и .,коэффициентов (k+1-C) / (+1) соответственно, а на Вторые входы группы блоков 2 умножения значения векторов и.ч (е), Uzi (е),..., (е), (е), Vj,- (е),...,v,-(E),(e),. (e ),..., W. (е) , после этого, поступают сигналы управления из блока б на упрайлягощйе.входы блока сумматоров 3. Приведенная последовательн.ость операций повторя.ется (k + 1) раз, то есть реализуется зависимость вида:;: . - ,....k+1-e (С) x.(k+i-e) k+i После этого по .сигналам из блока б. управления, поступающим на управляющие входы блока 8 памяти, коммутатора 5, и блока 7 сумматоров, осуществ-. ляется умножение полученных парных произведений .на соответствующие оэффициенты d,,-, tj и (-pj), последоательное поступление (в течение тактов) полученных значений векторови.,- (k+1), , (k+i; ,w,,-,- (k+i) Выходов блока 4 умножения через оммутатор 5 на входы блока 7 суммаоров и блока 8 памяти, то есть осуествляется вычисление следующего теущего значения вектора (k+l) и апись в блок 8 памяти векдоров ( , V-jVc (k+1) , W.,vq, (k+1) , Посе этого, подачей сигналов управления

из блока 6 управления на счетный вход управляющего триггера 24; последний . переводится в противоположное, состояние (в рассматриваеиом случае - единичное) : единичный сигнал с прямого выхода триггера 24 открываетэлемент 26 И, а нулевой сигнал с инверсного выхода триггера 24 закрывает элемент 25 И. После этого по сигналам управ- ления из блока б открывается элемент 23 И и вычисления повторяются анало гично описаннсяиу выше, начиная с пункта 2: вычисляется следующий вектор дискрет (в данном случае Х,(2) itsOero подинтервала интегрирования, на входы сумматора 14 поступает с выходов блока 9 реккурентных вычисулений через элемент 26 И и элемент 13 ИЛИ его инвертированное значение (-Хо(2)). В дальнейшем работа вычислительной структуры аналогична описанному выше, в зависимости от результатов проверки условия, осуществляется либо переход к следующему подинтервалу интегрирования, либо вычисление следующего на текущем подинтервале вектора дискрет неизвестНЫХ. ;- -

Рассматриваемое устройство благода:ря наличии новых элементов и связей между ними позволяет проводить решение систем обыкновенных дифференциальных уравнений с произвольной нелинейностью.

формула изобретения

Устройство для решения систем дифференциальньк уравнений, содержащее блок памяти, первый, второй, третий, четвертый и пятый выходы которого подключены соответственно к первому, вторсжлу, третьему, четвертому и пятбму входам блока реккурентных вычислений, первый выход которого соединен с первым входом блока памяти и со входом первого сумматора, выход кбторог о подключен соответственно к первому входу блока сдвига, второй и третий входы которого соединены соответствен но с шестым и седьмьй вьйсодами блока памяти, и к первому входу первого коммутатора, второй вход которого соединен с выходЬм блока сдвига, nepv вый выход первого коладутатора подключен к первому входу элемента ИЛИ, выход которого подключен ко вхо .. ду .второго сумматора, выход котЬрого соединен со входом блока сравнения, выход которого подключен ко входу блока управления, второй и третий входы элемента ИЛИ соединены соответственно с первым и вторым выходами второго коммутатора, первый и второй выходы которого подключены к первому и второму выходам блока реккурентных вычислений, шестой и седьмой входы которого соединены соответственно с вторым выходом (Первого коммутатора и с третьим выходом второго ксжлмутатора, восьмой вход блока реккурентных вычислений подключен к выходу первого блока сумматоров, управляющие входы блока памяти, первого и второго сумматоров, блока сдвига, первого блока сумматоров, блока реккурентных вычислений, блока сравнения, первого и второго комму та торов, второго блока сумматоров соединены с соответствующими выходами блока управления, группа блоков умножения, блок умножителей, отличающееся тем, что, с целью расширения класса решаемых задач за счет возможности решения систем уравнений с произвольнь1И виг дом нелинейности, в устройство дополнительно введены третий коммутатор ;и умножитель, причем первый и второй ;входы умножителя подключены к восьмому и девятому выходам блока памяти, Первая группа выходов которого соеди йена с первой группой входов группы блоков умножения, вторая группа входов которой подключена к выходу умножителя, выходы группы блоков умножения соединены со входами второго блока сумматоров, вЬаходы которого подключены к первой группе входов блока умножителей, вторая группа входов которого соединена со второй группой выходов блока памяти выходы блока умножителей подключены ко входам третьего коммутатора, выход которого соединен со входом первого блока сумматоров и со BTOpfcW входом блока памяти, управлягаций вход третьего коммутатора, подключен к соответствующему выходу блока управления.

Источники информации, принятые во внимание при экспертизе

363065, кл. G 06 G 7/34, 23.05.73.

Авторы

Даты

1980-02-05—Публикация

1977-10-25—Подача