ее

О) 00

00 00

00

1

Изобретение относится к цифровой вычислительной технике и предназначено для решения нелинейных уравнений теплопроводности вида

эи at

C(U) 4f- - 7(U)

Эх

эи ах

10

-t- f(x)

или в конечно-разностном представлении системы алгебраических уравнений вида

с(и; )

ut

и (Uu, ) . (&х) (, -и ) .

Mul ) „,i

(4x7

(и - и , )

f;

с(и ) „:it

и

к которой сводится При этом

,)

(1).

и, и(х;, t,); f, f(х;);

Ч 3 2,...,

U t; L.

i 1,2,

Р; j

Целью изобретения является расширение функциональных возможностей модуля одномерной вычислительной сие темы для решения нелинейных уравнений теплопроводности за счет учета нелинейной зависимости коэффициента теплоемкости от решения и наличия составляющей внутренних источников энергии и упрощения модуля.

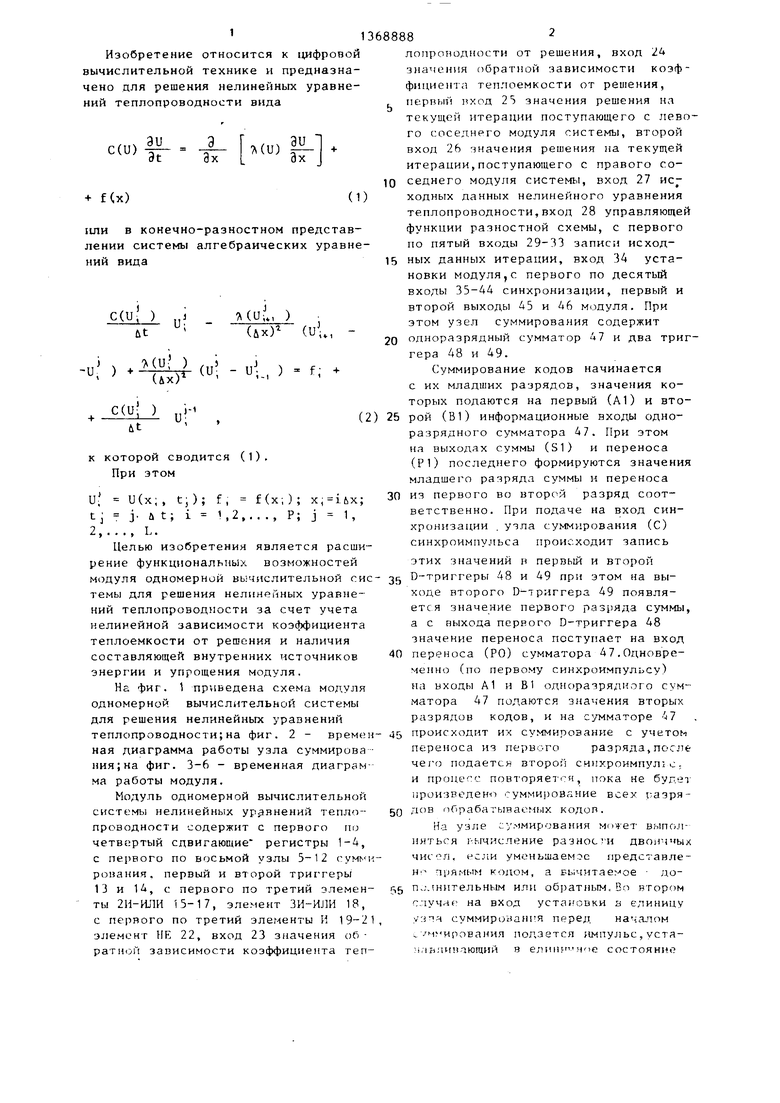

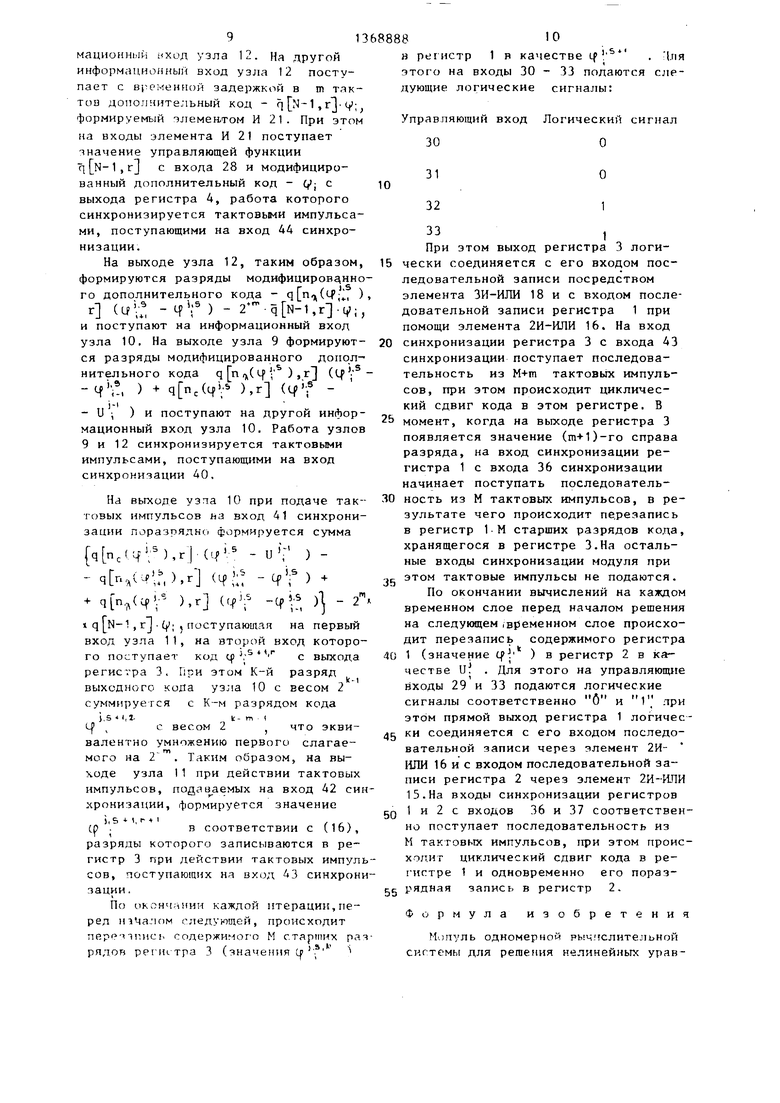

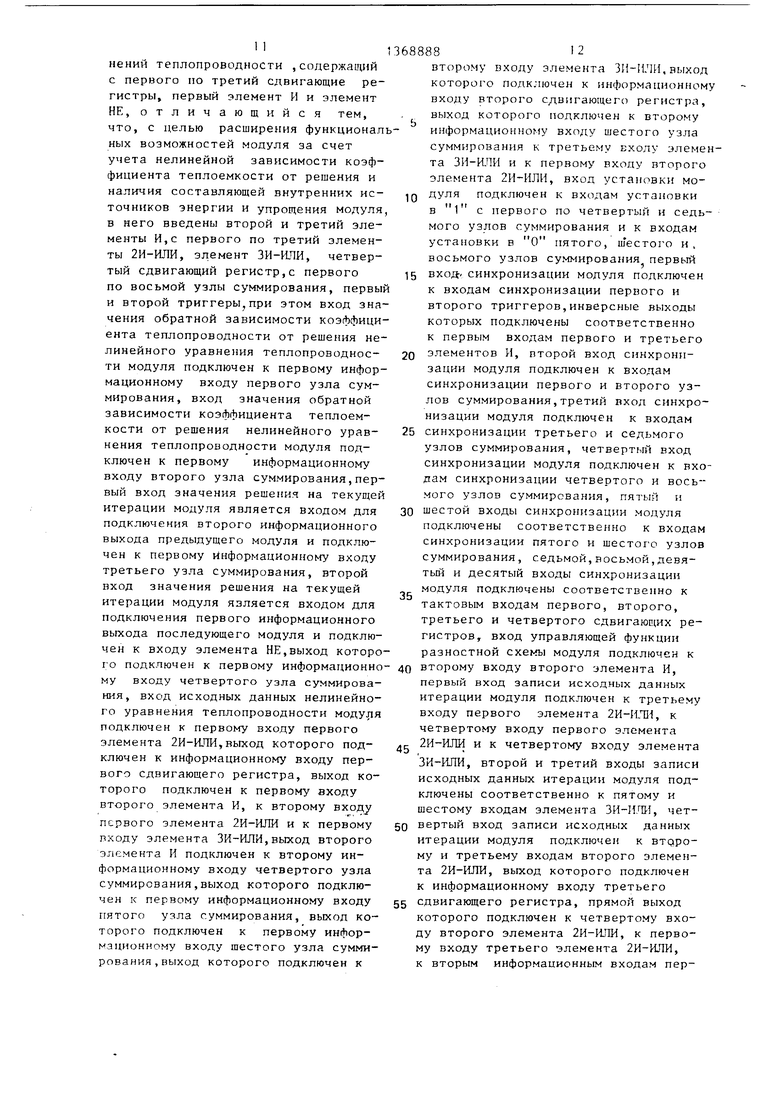

На фиг. 1 пр иведена схема модуля одномерной вычислительной системы для решения нелинейных уравнени11

13688882

лопронодности от решения, вход L значения обратной зависимости коэффициента теплоемкости от решения, первый нход 25 значения решения на текущей итерации поступающего с левого соседнего модуля системы, второй вход 26 значения решения на текущей итерации,поступающего с правого соседнего модуля системы, вход 27 ис- (1) ходных данных нелинейного уравнения теплопроводности,вход 28 управляющей функции разностной схемы, с первого по пятый входы 29-33 записи исход15 ных данных итерации, вход 34 установки модуля,с первого по десятый входы 35-4А синхронизации, первый и второй выходы 45 и 46 модуля. При этом узел суммирования содержит

20 одноразрядный сумматор 47 и два триггера 48 и 49.

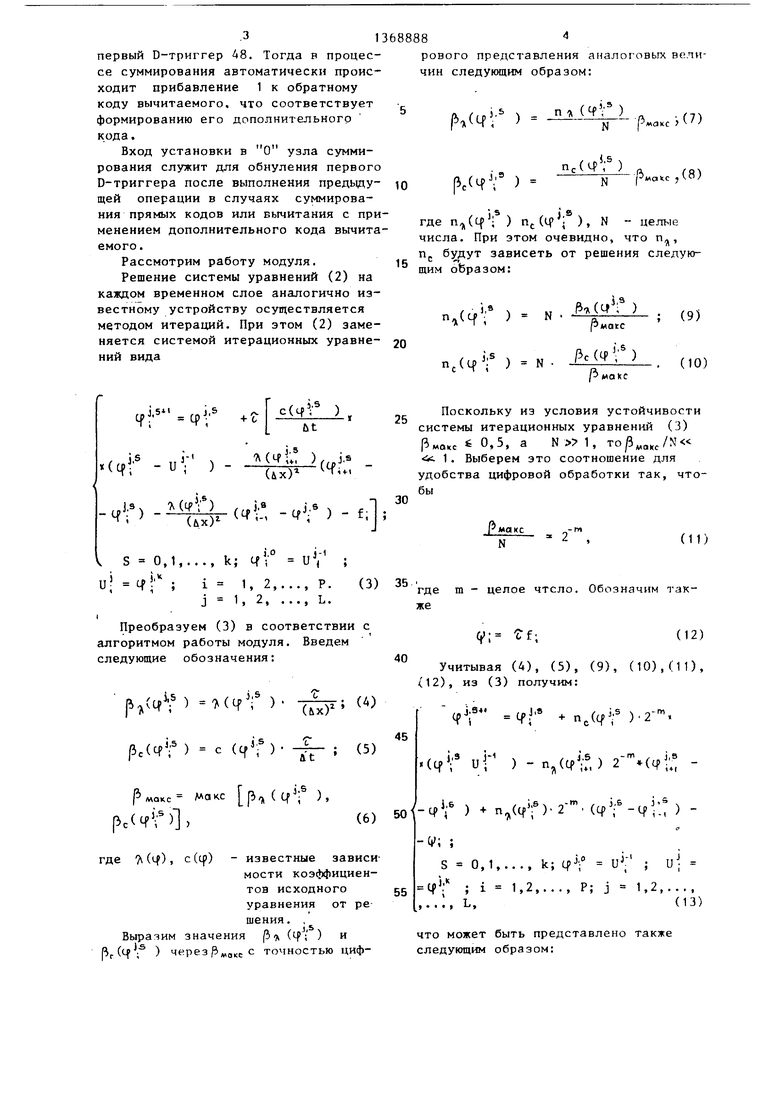

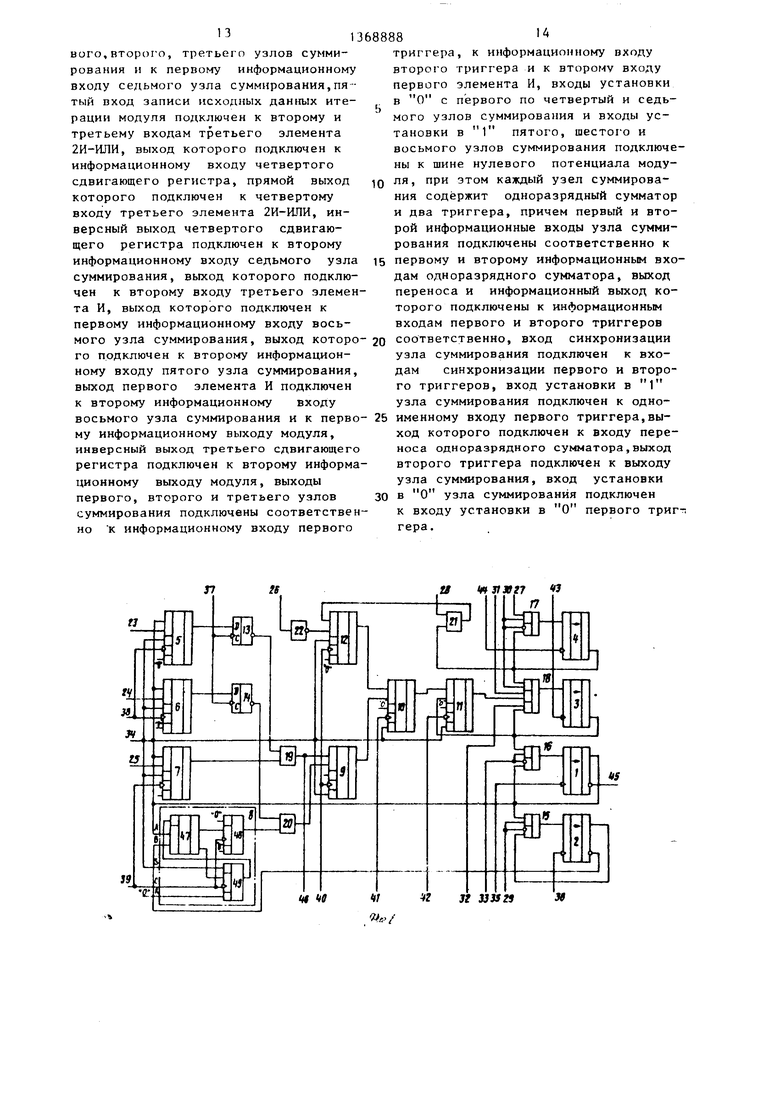

Суммирование кодов начинается с их младших разрядов, значения которых подаются на первый (А1) и вто- (2) 25 рой (В1) информационные входы одноразрядного сумматора 47. При этом на выходах суммы (S1) и переноса (Р1) последнего формируются значения младшего разряда суммы и переноса

30 из первого во второй разряд соответственно. При подаче на вход синхронизации . узла суммирования (С) синхроимпульса происходит запись

этих значений и первый и второй 35 D-триггеры 48 и 49 при этом на выходе второго D-триггера 49 появляется значение первого разряда суммы, а с выхода первого D-триггера 48 значение переноса поступает на вход 40 переноса (РО) сумматора 47.Одновременно (по первому синхроимпульсу) на входы А1 и В1 одноразрядного сумматора 47 подаются знач-ения вторых разрядов кодов, и на сумматоре 47

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Узловой процессор | 1986 |

|

SU1399763A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Многоканальное устройство для ввода информации от двухпозиционных датчиков | 1988 |

|

SU1550521A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для контроля устройства микропрограммного управления | 1988 |

|

SU1608674A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

Иеобретение относится к области цифровой вычислительной техники. Цель изобретения - расширение функциональных возможностей за счет учета нелинейной зависимости коэффициента теплопроводности от решения и наличия составляющей внутренних источников энергии и упрощения модуля. Модуль одномерной вычислительной системы для решения нелинейных уравнений теплопроводности содержит сдвигающие регистры, узлы - суммирования, триггеры, элементы 2И-1 ШИ, элемент ЗИ-ИЛИ, элементы И, элемент НЕ. 6 ил.

теплопроводности;на фиг. 2 - времен- 45 происходит их суммирование с учетом

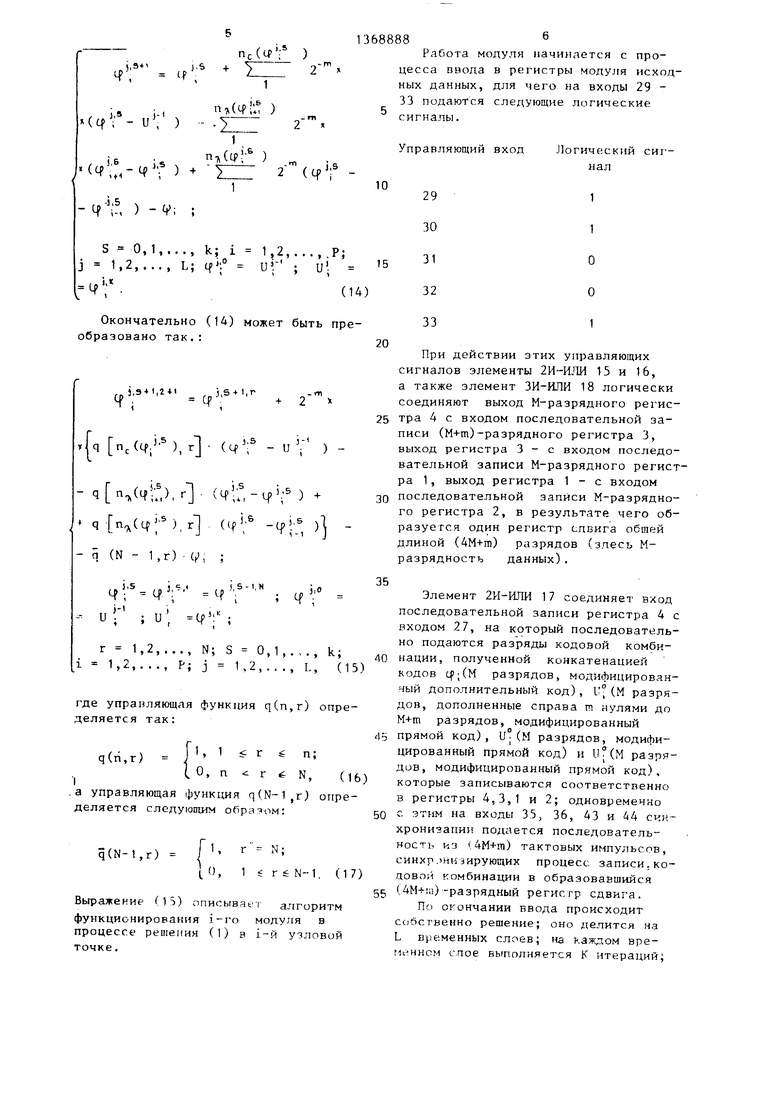

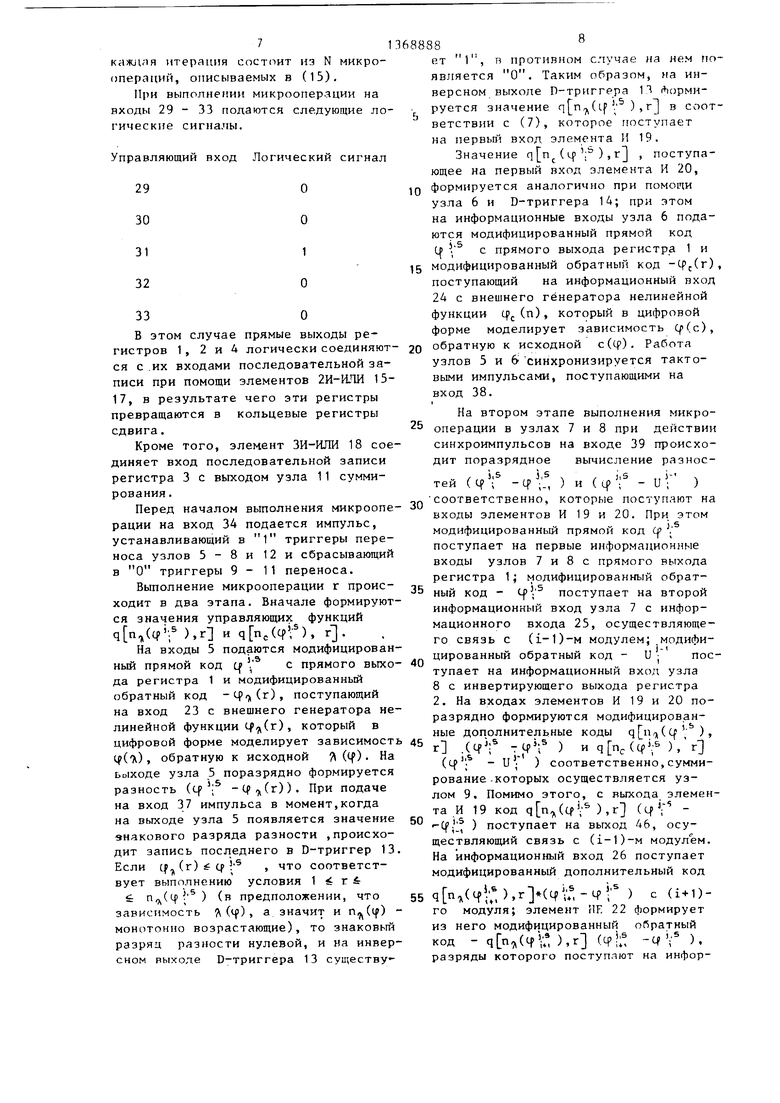

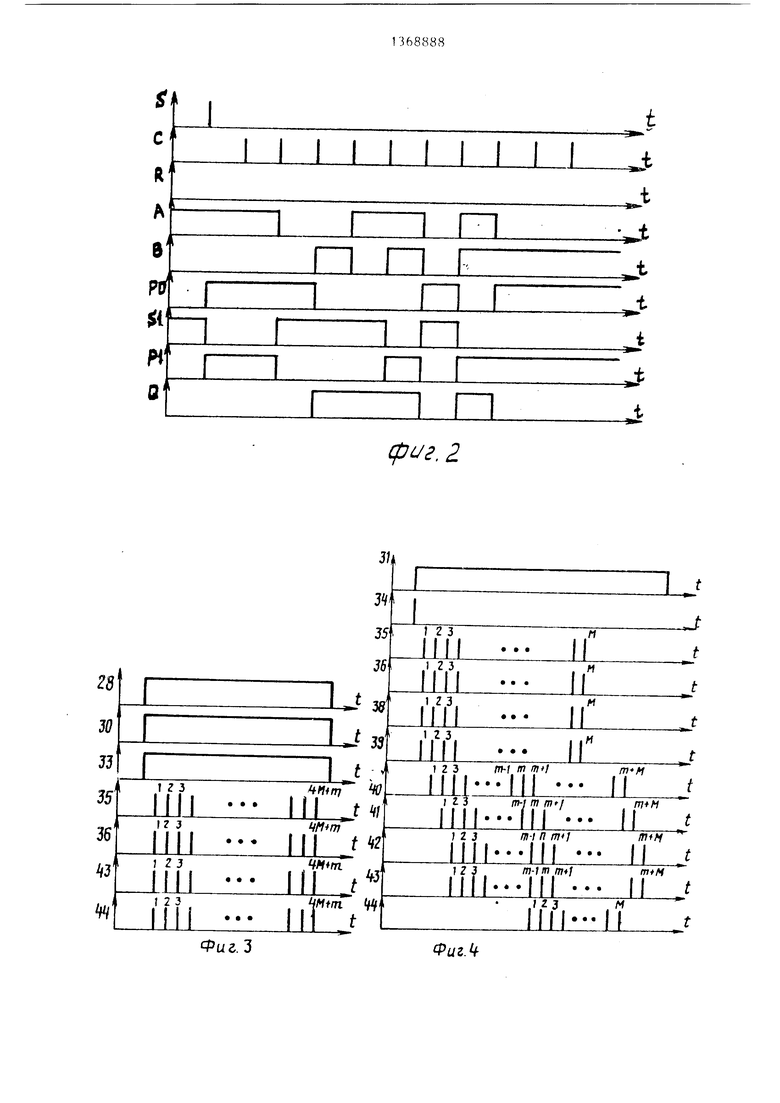

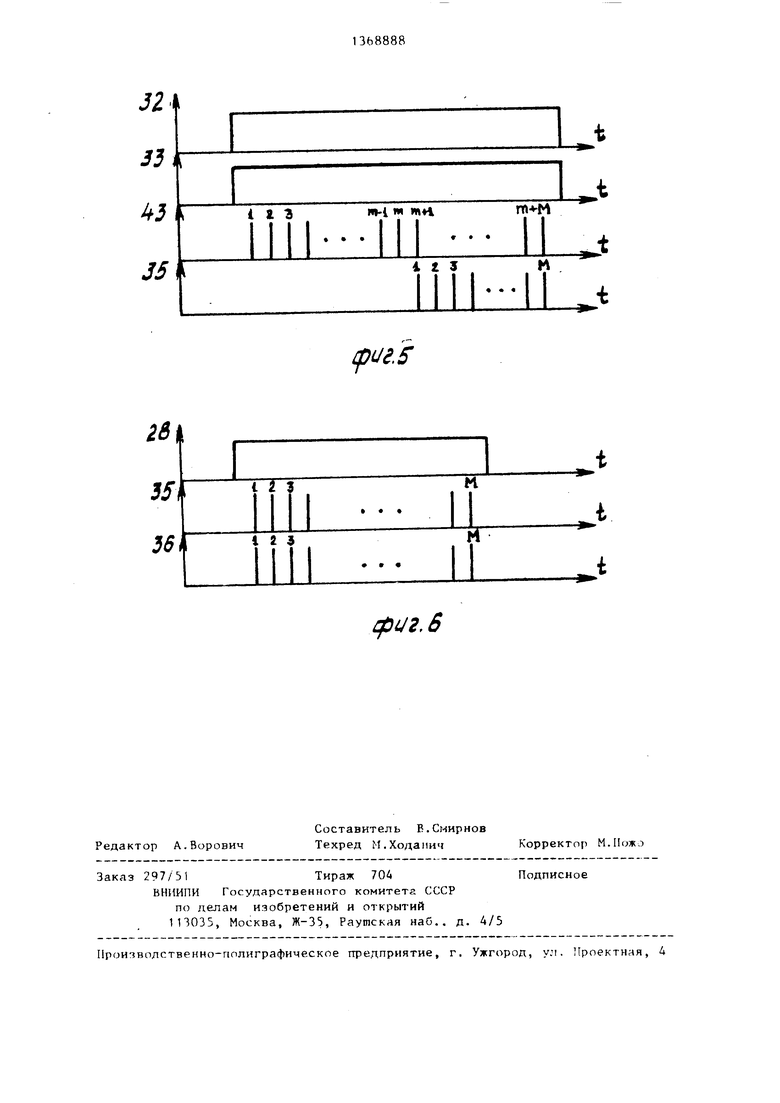

ная диаграмма работы узла суммирования; на фиг. 3-6 - временная диаграмма работы модуля.

Модуль одномерной вычислительной системы нелинейнь х уравнений теплопроводности содержит с первого по четвертый сдвигающие регистры 1-4, с первого по восьмой узлы 5-12 cyм. ронания, первый и второй триггеры 13 и 14, с первого по третий элементы 2И-ИЛИ 15-17, элемент ЗИ-ИЛИ 18, с первого по третий элементы И 19-21, элемент НЕ 22, вход 23 значения обратной зависимости коэффициента теппереноса из первого разряда,после чего подается второй сиихроимпул с, и процесс повторяется, пока не будв ь роизведен-о сумми1)ование всех разряДС В пГфабатынаемых кодоп.

На узле суммирования может выполняться г-ьгчисление разности дво11Ччых чисел, если уменьшаем:: е представле- Н п;)ямын кодом, а вычитаемое - доп,;.шительным или обратным. Во втором случае на вход установки а единицу узпч суммирования перед - ммирования подается импульс, уста- н.чвлитющий 8 ели111 Н (е состояние

31368888

первый D-триггер 48. Тогда в процес- рового представления аналоговых велн- се суммирования автоматически прайс- чин следующим образом: ходит прибавление 1 к обратному коду вычитаемого, что соответствует .гш Ч

формированию его дополнительного ft Ccf ) 1 лакс

кода.

Вход установки в О узла суммирования служит для обнуления первого, , ) D-триггера после выполнения предьщу- Q N i « щей операции в случаях суммирования прямых кодов или вычитания с при- / i. N л 1.4

где п..(Ч ; ) ntdfj ), N - целые менением дополнительного кода вычита- „ с - i

числа. При этом очевидно, что п«, емого.

,,п. будут зависеть от решения следуюРассмотрим работу модуля. IK

„ ..„ч щим образом:

Решение системы уравнений (2) на

каждом временном слое аналогично известному устройству осуществляется, ). и PuCt-f ; )

D л n l- iy у t у V- I Г у / J V 1 ajin CIV..М| Л М /АПЧ

методом итераций. При этом (2) заме- /b/natc

10)

няется системой итерационных уравне- 20

ий видаn,(4 i ) N . (

,-0, ,-j,5 . )Поскольку из условия устойчивости

btсистемы итерационных уравнений (3)

j,5 .,, t 0,5, а N 1, TO,,/N«

j,s г ч /А (ч и, ) /..j. 1. Выберем это соотношение для

«(гг -U; ) - :;;; ( (лх) удобства цифровой обработки так, чтобы,5; :а -. -I 30

- Г - .

S 0,1,..., k; tfi UV ;

|- макс „-М - 2 ,(11)

i 1,2,...,. (3) 35 чтсло. Обозначим такj 1 , 2, . .., L. I

Преобразуем (3) в соответствии с

алгоритмом работы модуля. ВведемVi 1

следующие обозначения:40, ч ч ч . , ч

Учитывая (4), (5), (9), (10),(11), (12), из (3) получим: i5 . . . . .. . ,

Т fr n,( ).2,,,....,.,, ,3) ,,,.„.. ,.,,,.,.,,.

P,(cfY) ( ) ()

PMQKC макс РТ, ( ),

Р.СЧ-Г),(6)

-V; ; где (if), с(ц)) - известные зависи-q-i; ) nXf).2-.(4.)

0,1,..., k; CfY ; U-| мости коэффициен-

тов исходного55 ,..., Р; j 1,2,..., уравнения от ре- ,. . ,, L,(13)

шения. ,

Выразим значения (3-х () и что может быть представлено также R (cf. ) через Р иакс точностью циф- следующим образом:

-q-i; ) nXf).2-.(4.) псСм ; )

(,3+1 ),6

ч--, cf ,

( uV )

n,(tfaT )

1

),б

ч-Т )

пт,{(уГ )

(

),5

-tfT, ) -V; ;

S 0,1,..., k; i j 1,2,..., L; tff i,x

,0

(f

Окончательно (14) может быть преобразовано так.:

5,,7.. J.S..,r -. i1

,,(Cf),r. ( - UV ) - ,(ч),г. ()

4 q f n( q ) r ((f -IfV )1 - разуется один регистр сдвига обшей

При действии этих управляющих сигналов элементы 2И-ИЛИ 15 и 16, а также элемент ЗИ-ИЛИ 18 логически соединяют выход М-разрядного реги

25 тра 4 с входом последовательной за писи (М+т)-разрядного регистра 3, выход регистра 3-е входом послед вательной записи М-разрядного реги ра 1, выход регистра 1 - с входом

3Q последовательной записи М-разрядн го регистра 2, в результате чего о

длиной (4М+гп) разрядов (здесь М- разрядность данных).

- q (N - 1,г) V, ;

fV ; r ; и; (Y;

35

и Г

г 1,2,..., N; S 0,1,..., k; 1,2,. .., Р; j 1.2,.. ., L, (15)

q(ri,r)

Элемент 2И-ИЛИ 17 соединяет вход последовательной записи регистра 4 с входом 27, на который последовательно подаются разряды кодовой комби- 40 нации, полученной конкатенацией

кодов q ;(M разрядов, модифицированный дополнительный код), U°(М разрягде управляющая функция q(n,r) опре- ДО, дополненные справа m нулями до деляется так: разрядов, модифицированный

45 прямой код), U|(M разрядов, модифи-1,1 г ё п; цированный прямой код) и U(M разря- „дов, модифицированный прямой код),

I- И6) которые записываются соответственно

.а управляющая функция q(N-1,r) опре- в регистры 4,3,1 и 2; одновременно деляется следующим образом:50 - этим на входы 35, 36, 43 и 44 синхронизации подается последовательГ, I,.ность из (4М+га) тактовых импульсов,

q(N-1,r) синхронизирующих процесс записи.ко(0, 1 г N-1, (17) aoBOii комбинации в образовавшийся

дс ()-разрядный регистр сдвига.

Выражение (15) описывает алгоритм По окончании ввода происходит функционирования i-ro модуля в собственно решение; оно делится на процессе решения (1) в i-й узловой L временных слоев; на каждом вре- точке.пеннсм слое выполняется К итераций;

1368888

Работа модуля начинается с процесса ввода в регистры модуля исходных данных, для чего на входы 29 - 33 подаются следующие логические

сигналы. Управляющий вход

29 30 31 32 33

Логический сигнал

1

1

О О

1

разуется один регистр сдвига обшей

При действии этих управляющих сигналов элементы 2И-ИЛИ 15 и 16, а также элемент ЗИ-ИЛИ 18 логически соединяют выход М-разрядного регистра 4 с входом последовательной записи (М+т)-разрядного регистра 3, выход регистра 3-е входом последовательной записи М-разрядного регистра 1, выход регистра 1 - с входом

последовательной записи М-разрядного регистра 2, в результате чего образуется один регистр сдвига обшей

длиной (4М+гп) разрядов (здесь М- разрядность данных).

кажлля итерация состоит из N микроопераций, описываемых в (15).

При выполнении микрооперации на входы 29 - 33 подаются следующие логические сигналы.

Управляющий вход 29 30 31 32

Логический сигнал

О

33О

В этом случае прямые выходы регистров 1, 2 и 4 логически соединяются с .их входами последовательной записи при помощи элементов 2И-ИЛИ 15- 17, в результате чего эти регистры превращаются в кольцевые регистры сдвига.

Кроме того, элемент ЗИ-ИЛИ 18 соединяет вход последовательной записи регистра 3 с выходом узла 11 суммирования .

Перед началом выполнения микрооперации на вход 34 подается импульс, устанавливающий в 1 триггеры переноса узлов 5 - 8 и 12 и сбрасывающий в О триггеры 9-11 переноса.

Выполнение микрооперации г проис

ходит в два этапа. Вначале формируются значения управляющих функций ,((f ; ),г и ,(Cf ,), г.

На входы 5 подаются модифицированный прямой код Lf V с прямого выхода регистра 1 и модифицированный обратный код -ер(г), поступающий на вход 23 с внешнего генератора нелинейной функции tf,(г), который в цифровой форме моделирует зависимость Ч ( Х), обратную к исходной ((f). На Ьо1ходе узла 5 поразрядно формируется разность (cf 1 -(f,j,(r)). При подаче на вход 37 импульса в момент,когда на выходе узла 5 появляется значение знакового разряда разности ,происходит запись последнего в D-триггер 13 Если Cf(r)q , что соответствует выполнению условия 1 г г ё: п(Ц1| ) (в предположении, что

зависимость

лСн).

а значит и п,

,((f)

монотонно возрастающие), то знаковьш разряд разности нулевой, и на инверсном выхоле D-триггера 13 существу

5

10

ет 1, п противном случае на нем появляется О. Таким образом, на инверсном выхоле D-триггера 11 Лорнируется значение п7(. ) , соответствии с (7), которое поступает на первьв вход элемента И 19.

Значение ( ц| : ), г , поступающее на первый вход элемента Н 20, формируется аналогично при помощи узла 6 и D-триггера 14; при этом на информационные входы узла 6 подаются модифицированный прямой код Ц| V с прямого выхода регистра 1 и 5 модифицированный обратный код -Cf(г) , поступающий на информационный вход 24 с внешнего генератора нелинейной функции Cfj.(n), который в цифровой форме моделирует зависимость Cf(c), обратную к исходной c(Cf). Работа узлов 5 и 6 синхронизируется тактовыми импульсами, поступающими на вход 38.

На втором этапе выполнения микрооперации в узлах 7 и 8 при действии синхроимпульсов на входе 39 происхо- вычисление разнос- )20

25

30

35

40

45

дит поразрядное

/ liS J,S тай ( tf ; -Cf ;-,

50

55

) и (q)r - U; ) соответственно, которые поступают на входы элементов И 19 и 20. При, этом модифицированный прямой код Cf V поступает на первые информационные входы узлов 7 и В с прямого выхода регистра 1; модифицированный обратный код - ср поступает на второй информационный вход узла 7 с информационного входа 25, осуществляющего связь с (i-l)-M модулем; модифицированный обратный код - и поступает на информационный вход узла 8 с инвертирующего выхода регистра 2, На входах элементов И 19 и 20 поразрядно формируются модифицированные дополнительные коды (Cf ), г .( ) и (cfi;b )/г

(ср ; - и. ) соответственно, суммирование -которых осуществляется узлом 9. Помимо этого, с выхода элемента И 19 код ( ),г ( - поступает на выход 46, осуществляющий связь с (i-l)-M модулем. На информационный вход 26 поступает модифицированный дополнительный код

,(4.;f,),r(,-4 r ) с ( го модуля; элемент НЕ 22 формирует из него модифицированный обратный код - (tf ),г ( -с ), разряды которого поступают на инфор9

мацнонный узла 12. На другой информационный вход узла 12 поступает с временной задержкой в m тактов дополнительный код - , формируемый злемеатом И 21. При это яа входы элемента И 21 поступает значение управляющей функции ,rj с входа 28 и модифицированный дополнительный код - Cf- с выхода регистра 4, работа которого синхронизируется тактовыми импульсами, поступающими на вход 44 синхронизации.

На выходе узла 12, таким образом

формируются разряды модифицировднно- го дополнительного кода - .)(cf-, ),

г (1 - f ) - .,r.Vi, и поступают на информационный вход узла 10. На выходе узла 9 формируются разряды модифицированного дополнительного кода q п/хС Ц| ), г (( -Ц ;Д ) + ,(Lf . b ),г (tf f - и ; ) И поступают на другой информационный вход узла 10, Работа узлов 9 и 12 синхронизируется тактовыми импульсами, поступающими на вход синхронизации 40,

На выходе узла 10 при подаче так-- товых импульсов на вход 41 синхронизации поразрядно формируется сумма

),г;

( ) 5

- и

- ,(r,).r ( :; . ) .

,( ),г ((f -( ) - 2

t q N-I , rJ (; J поступающая на первый вход узла 11, на второй вход которого поступает код qi - с выхода регистра 3, При этом К-й разряд выходного кода узла 10 с весом 2 суммируется с К-м разрядом кода

j,,(

Cf С весом 2 J что эквивалентно умножению первого слагаемого на 2, Таким образом, на выходе узла I1 при действии тактовых импульсов, подаваемых на вход 42 синхронизации, формируется значение

),6 1, 1- + If , г

ср . Б соответствии с (16), разряды которого записываются в регистр 3 при действии тактовых импульсов, поступающих на вход 43 синхронизации .

По оконч;и(ии каждой итерации,перед Н1 ча.пом следующей, происходит перет inncii содержимого М старших разрядов репк тра 3 (значаняя Cf

10

я регистр

l.S

1 в качестве cf

этого на входы 30 - 33 подаются дующие логические сигналы:

вход

Логический сигнал О

О

1

5

0

0

33

I

При этом выход регистра 3 логически соединяется с его входом последовательной записи посредством элемента ЗИ-ИЛИ 18 и с входом последовательной записи регистра 1 при помощи элемента 2И-ИЛИ 16. На вход синхронизации регистра 3 с входа 43 синхронизации поступает последовательность из М+т тактовых импульсов, при этом происходит циклический сдвиг кода в этом регистре, В

5 момент, когда на выходе регистра 3 появляется значение (m-t-l)-ro справа разряда, на вход синхронизации регистра 1 с входа 36 синхронизации начинает поступать последовательность из М тактовых импульсов, в результате чего происходит перезапись в регистр I.M старших разрядов кода, хранящегося в регистре З.На остальные входы синхронизации модуля при этом тактовые импульсы не подаются.

По окончании вычислений на каждом временном слое перед началом рещения на следующем(временном слое происходит перезапись содержимого регистра 1 (значение ср ) в регистр 2 в качестве Uf . Для этого на управляющие входы 29 и 33 подаются логические сигналы соответственно б и при этом прямой выход регистра 1 логичес5 ки соединяется с его входом последовательной записи через элемент 2И- НЛИ 16 и с входом последовательной записи регистра 2 через элемент 2И-ИЛИ 15.На входы синхронизации регистров

0 1 и 2 с входов 36 и 37 соответственно поступает последовательность из М тактовых импульсов, гфи этом происходит циклический сдвиг кода в регистре 1 и одновременно его поразg рядная запись в регистр 2,

Формула изобретения

Молуль одномерной рыч-чслительной системы для решения нелинейных урав5

0

нений теплопроводности ,содержа1члй с первого по третий сдвигающие регистры, первый элемент И и элемент НЕ, отличающийся тем, что, с целью расширения функционал ных возможностей модуля за счет учета нелинейной зависимости коэффициента теплоемкости от решения и наличия составляющей внутренних источников энергии и упрощения модуля в него введены второй и третий элементы И,с первого по третий элементы 2И-ИЛИ, эдемент ЗИ-ИЛИ, четвертый сдвигающий регистр,с первого по восьмой узлы суммирования, первы и второй триггеры при этом вход значения обратной зависимости коэффициента теплопроводности от решения нелинейного уравнения теплопроводности модуля подключен к первому информационному входу первого узла суммирования, вход значения обратной зависимости коэффициента теплоемкости от решения нелинейного уравнения теплопроводности модуля подключен к первому информационному входу второго узла суммирования,первый вход значения решения на текущей итерации модуля является входом для подключения второго информационного выхода предыдущего модуля и подключен к первому информационному входу третьего узла суммирования, второй вход значения решения на текущей итерации модуля является входом для подключения первого информационного выхода последующего модуля и подключен к входу элемента НЕ,выход которого подключен к первому информационному входу четвертого узла суммирования, вход исходных данных нелинейного уравнения теплопроводности модуля подключен к первому входу первого элемента 2И-ИЛИ,выход которого подключен к информационному входу первого сдвигающего регистра, выход которого подключен к первому входу второго элемента И, к второму входу первого элемента 2И-ИЛИ и к первому пходу элемента ЗИ-ИЛИ,выход второго элемента И подключен к второму информационному входу четвертого узла суммирования,выход которого подключен к первому информационному входу пятого узла суммирования, выход которого подключен к первому информационному входу шестого узла суммирования , выход которого подключен к

68888 2

второму входу элемента ЗИ-ИЛИ,выход которого подключен к информационному входу второго сдвигающего регистра, выход которого подключен к второму информационному входу шестого узла суммирования к третьему входу элемента ЗИ-ИЛИ и к первому входу второго элемента 2И-ИЛИ, вход установки мо- Q дуля подключен к входам установки в 1 с первого по четвертый и седьмого узлов суммирования и к входам установки в О пятого, ш естого и. восьмого узлов суммирования первый 15 вход- синхронизации модуля подключен к входам синхронизации первого и второго триггеров,инверсные выходы которых подключены соответственно к первым входам первого и третьего 20 элементов И, второй вход синхронизации модуля подключен к входам синхронизации первого и второго узлов суммирования,третий вход синхронизации модуля подключен к входам 25 синхронизации третьего и седьмого узлов суммирования, четвертый вход синхронизации модуля подключен к входам синхронизации четвертого и восьмого узлов суммирования, пятый и 30 шестой входы синхронизации модуля подключены соответственно к входам синхронизации пятого и шестого узлов суммирования, седьмой,восьмой,девятый и десятый входы синхронизации модуля подключены соответственно к тактовым входам первого, второго, третьего и четвертого сдвигающих регистров,, вход управляющей функции разностной схемы модуля подключен к 40 второму входу второго элемента И, первый вход записи исходных данных итерации модуля подключен к третьему входу первого элемента 2И-ИЛИ, к четвертому входу первого элемента .g 2И-ИЛИ и к четвертому входу элемента ЗИ-1-ШИ, второй и третий входы записи исходных данных итерации модуля подключены соответственно к пятому и шестому входам элемента ЗИ-ИЛИ, чет- 50 вертый вход записи исходных данных итерации модуля подключен к BTQPO- му и третьему входам второго элемента 2И-ИГГИ, выход которого подключен к информационному входу третьего 55 сдвигающего регистра, прямой выход которого подключен к четвертому входу второго элемента 2И-ИЛИ, к первому входу третьего элемента 2И-ИЛИ, к вторым информационным входам пер35

13

вого,второго, третьего узлов суммирования и к первому информационному входу седьмого узла суммирования,пятый вход записи исходных данных итерации модуля подключен к второму и третьему входам третьего элемента 2И-ИЛИ, выход которого подключен к информационному входу четвертого сдвигающего регистра, прямой выход которого подключен к четвертому входу третьего элемента 2И-ИЛИ, инверсный выход четвертого сдвигающего регистра подключен к второму информационному входу седьмого узла суммирования, выход которого подключен к второму входу третьего элемента И, выход которого подключен к первому информационному входу восьмого узла суммирования, выход которо- 20 соответственно, вход синхронизации

го подключен к второму информационному входу пятого узла суммирования, выход первого элемента И подключен к второму информационному входу

восьмого узла суммирования и к перво- 25 именному входу первого триггера,вы- му информационному выходу модуля, инверсный выход третьего сдвигающего регистра подключен к второму информационному выходу модуля, выходы первого, второго и третьего узлов 30 суммирования подключены соответственно к информационному входу первого

ход которого подключен к входу переноса одноразрядного сумматора,выход второго триггера подключен к выходу узла суммирования, вход установки в О узла суммирования подключен к входу установки в О первого триг гера.

37

IS

68888

триггера, к информационному входу BTopoi o триггера и к второму входу первого элемента И, входы установки в О с первого по четвертый и седь- мого узлов суммирования и входы установки в 1 пятого, шестого и восьмого узлов суммирования подключены к шине нулевого потенциала моду- 0 ля, при этом каждый узел суммирования содержит одноразрядный сумматор и два триггера, причем первый и второй информационные входы узла суммирования подключены соответственно к 15 первому и второму информационным входам одноразрядного сумматора, выход переноса и информационный выход которого подключены к информационным входам первого и второго триггеров

узла суммирования подключен к входам синхронизации первого и второго триггеров, вход установки в 1 узла суммирования подключен к одноименному входу первого триггера,вы-

ход которого подключен к входу переноса одноразрядного сумматора,выход второго триггера подключен к выходу узла суммирования, вход установки в О узла суммирования подключен к входу установки в О первого триггера.

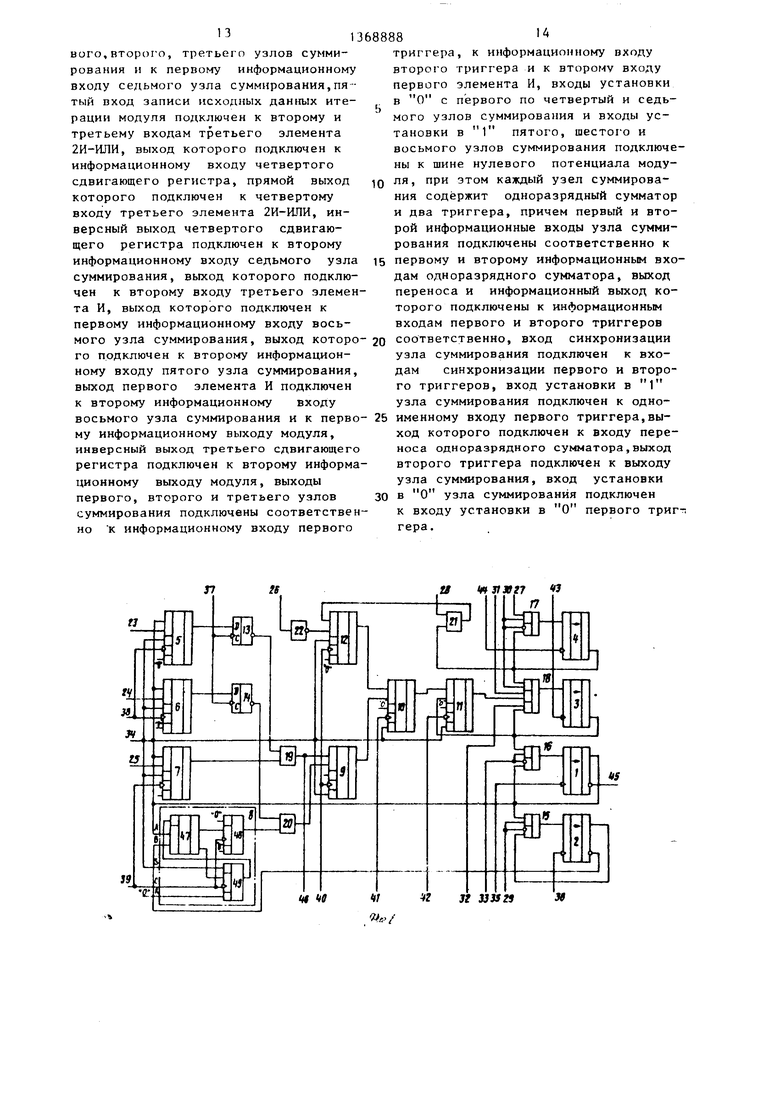

ti I ляг

Фиг. 3

.2.

ФцгМ

35

1

I di

i 2 3

i 9

M

f/es

i t

CpU2.6

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЗАДАЧ ТЕПЛОПРОВОДНОСТИ | 0 |

|

SU373735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1159030, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-01-23—Публикация

1986-07-18—Подача