П к ючены к выходам соответствующих эл ментов ИЛИ второй группы, первые вхо ды элементов ИЛИ второй группы подключены к выходам соответствующих элементов И второй группы, вторые входа элементов ИЛИ второй группы по ключены к выходам- соответствующих элементов И- первой группы, разряды выхода второго вычитател подключены к первым входам соответствующих разрядов блока сравнения, разряды выхоДа блока задания точности вычислений подключены к вторым входам соответствующих разрядов блока сравнения,, выход которого подключен к втор входам элементов И первой группы, пр чем блок управления содержит генератор импульсов, девять триггеров, фор мирователь импульсов, четыре элемента задержки, девять эле.ментов И, сдвигающий регистр, пять распределителей импульсов, и шифратор, причем выход первого триггера подключен к входу запуска генератора импульсов, выход генератора импульсов подключен к первым входам пятого, шестого, сед мого, восьмого и девятого элементов блока управления, выходы которых подключены к входам первого, второго, третьего, четвертого и пятого ра пределителей импульсов, первый выход первого распределителя импульсов под ключен к установочному входу третьег триггера через первый элемент задержки и к первому входу шифратора,- второй выход первого распределителя импульсов подключен к второму i входу шифратора,-третий выход первог распределителя импульсов подключен к установочному входу пятого триггера через второй элемент задержки и к TpeTbeNry в:соду шифратора, четвертый выход первого распределителя импульсов подключен к установочному входу седьмого триггера через третий элемент задержки и к четвертому входу шифратора, пятый выход первого распределителя импульсов подключен к входу формирователя импульсов и к пятому входу шифратора, первый выход второго распределителя импульсов подключен к шестому входу шифратора, а второй выход - к второму входу первого элемента И блока управления, первый выход третьего распределителя импульсов подключей к седьмому входу шифратора, второй выход - к второму входу второго элемента И, первый выход четвертого 3 распределителя импульсов подключен к восьмому входу шифратора, второй вы- ход - к установочному входу девятого триггера через четвертый элемент задержки и к девятому входу шифратора третий выход четвертого распределителя импульсов подключен к деся:Тому входу шифратора, а четвертый и пятый выходы - к одиннадцатому и двенадцатому входам шифратора соответственно, шестой выход четвертого распределителя импульсов подключен к второму входу третьего элемента Иблока управления и к тринадцатому входу шифратора, первый выход пятого распределителя импульсов подключен к четырнадцатому входу шифратора, а- второй вьпсод - к второму входу четвертого элемента И блока управления, к первому входу первого, второго, третьего и четвертого элементов И блока управления подключен прямой выход второго., четвер того-, шестого и восьмого триггер.ов соответственно, входы сброса первого, второго, четвертого, шестого и восьмого триггеров подключены к выходу формирователя импульсов, выходы первого, второго, третьего и четвертого элементов И блока управления подключены к входам сброса соответственно третьего, пятого, седьмого и девятого триггеров, прямые выходы которых подключены к. вторым входам шестого, седьмого восьмого- и девятого элементов И блока управления соответственно, инверсные выходы третьего, пятого и седьмого триггеров подключены соответственно к второму, третьему и четвертому входу пятого элемента И блока управления, инверсный вьпкод девятого триггера подключен к третьему входу восьмого элемента И блока управления, первый выход шифратора подключен к входу управления сдвигом сдвигающего регистра блока управления, выход мпадшего разряда которого соединен с установочным входом четвертого триггера, с входом управления сдвигом третьего сдвигающего регистра и с входом синхронизации второго сдвигшощего регистра, второй выход шифратора подключен к входам синхронизации второго и первого регистров, третий выход шифратора подключен к входам управления записью ервого и четвертого сдвигающих регистров, четвертый выход шифратора подключен к входам управления сдвигом первого и четвертого сдвигающих ретистров, пятый выход шифратора под ключен к вторым входам элементов И второй группы, шестой выход шифратора подключен к входу синхронизации четвертого регистра-, седьмой выход ши.фратора подключен к входу синхронизации квадратора и к входу синхронизации сумматора, восьмой выход 1йифратора подключен к входу синхронизации первого вычитателя, девятый вы ход шифратора подключен .к входам управления записью пятого и шестого сдвигаю1цих регистров, десятый выход шифратора подключен к входам управления сдвигом пятого и шестого сдвигающих регистров одиннадцатый выход шифратора подключен к входу синхронизации третьего сдвигающего регистра, двенадцатый выход шифратора подключен к входу, синхронизации второго вычитателя, а тринадцатый выход шифратора подключен к входу младшего разряда второго регистра, выход блока сравнения подключен : установочному входу шестого триггера, выход младшего разряда четвертого, сдвигающего регистра подключен к установочному входу четвертого триггера, а выход младшего разряда пятого сдвигающего регистра подключен к установочному входу восьмого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1988 |

|

SU1569827A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Цифровой генератор функций | 1981 |

|

SU1035594A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Устройство для контроля параметров | 1989 |

|

SU1667009A1 |

| Генератор двоичных чисел | 1981 |

|

SU1062674A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ,содержащее сумматор и первый сдвигающий регистр, выходы которого подключены к первой группе входов .сумматора, отличающееся тем, что, с цепью расширения диапазона изменения аргу- мента и увеличения быстродействия, в него введены второй, третий-, четвертый, пятый и шестой сдвигающие регистры, элемент задержки, первый, второй, третий и четвертый регистры, первый и второй вычитатели, первая и вторая группы элементов ИЛИ, блок сравнения, квадратор, блок задания точности вычислений, первая и вторая группы элементов И и блок управления, причем выход элемента задержки подключен к входу старшего разряда второго сдвигающего perHCTpat выход младшего разряда третьего сдвигающего регистра подключен к входу элемента задержки и к управляющим входам сдвига и обнуления второго- сдвигающего ре гистра, информационный вход третьего сдвигающего регистра соединен с информационным входом первого сдвигающего регистра, выходы 26 -го и

1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах и однородных вычислительных структурах.

Целью изобретения является расширение диапазона изменения аргумента, улучшение эксплуатационных характеристик и увеличение быстродействия.

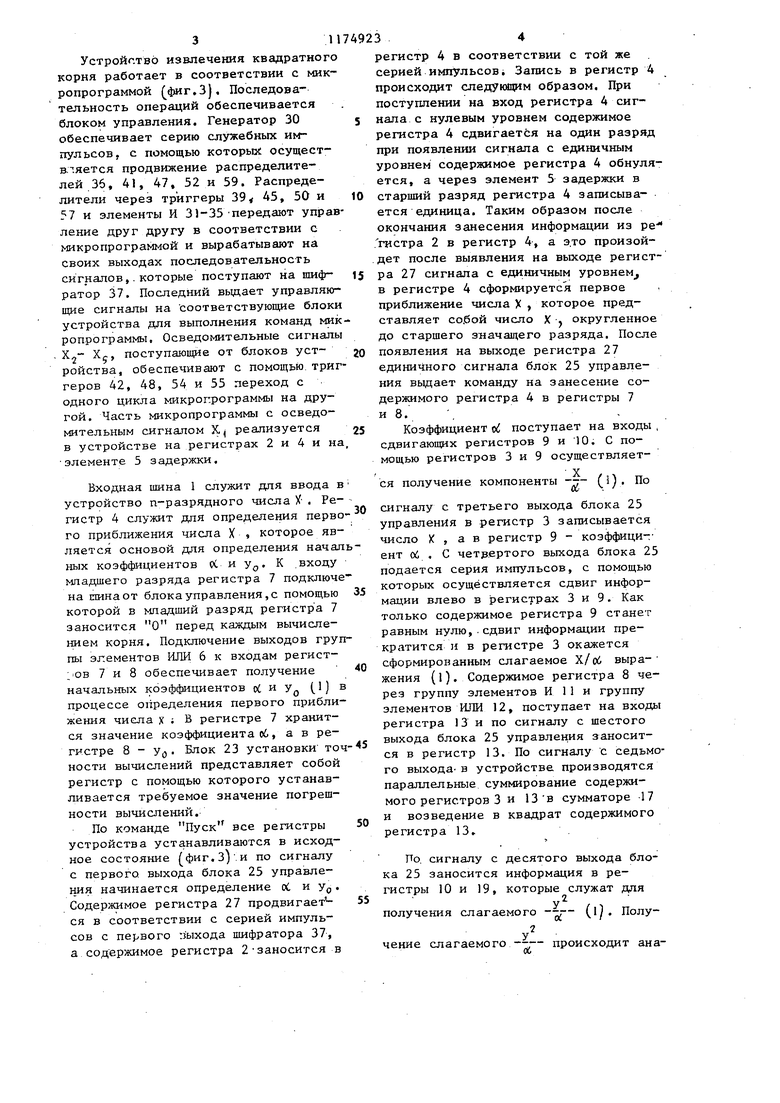

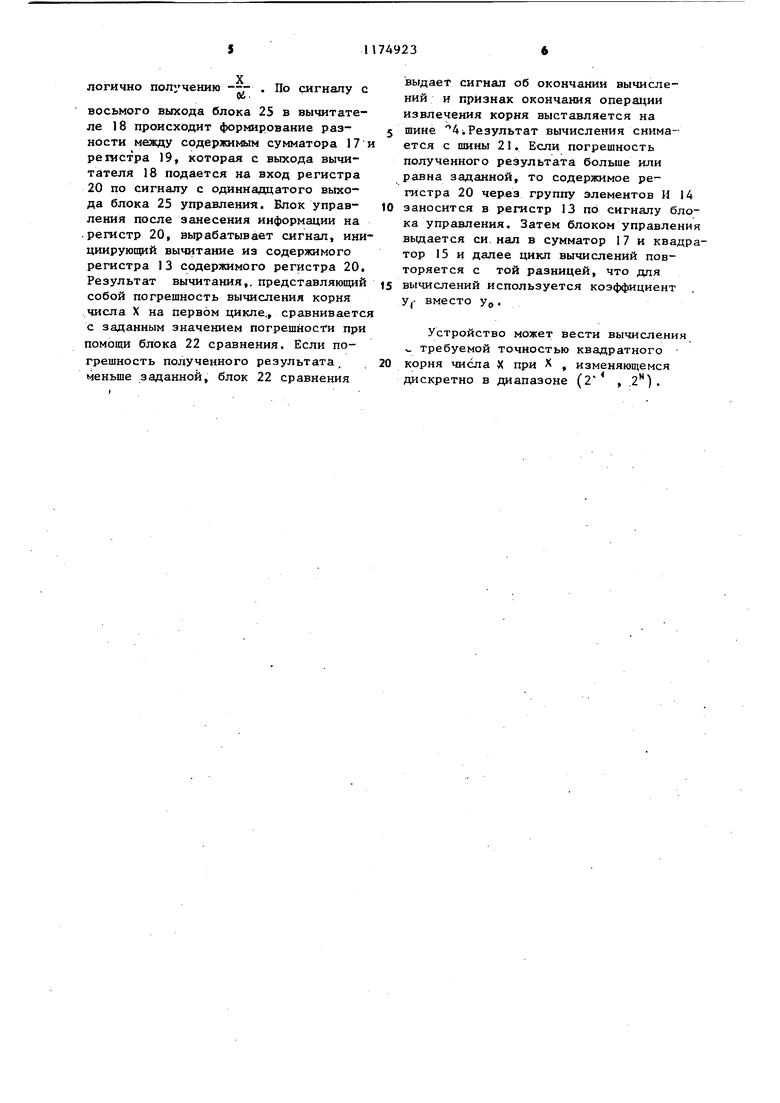

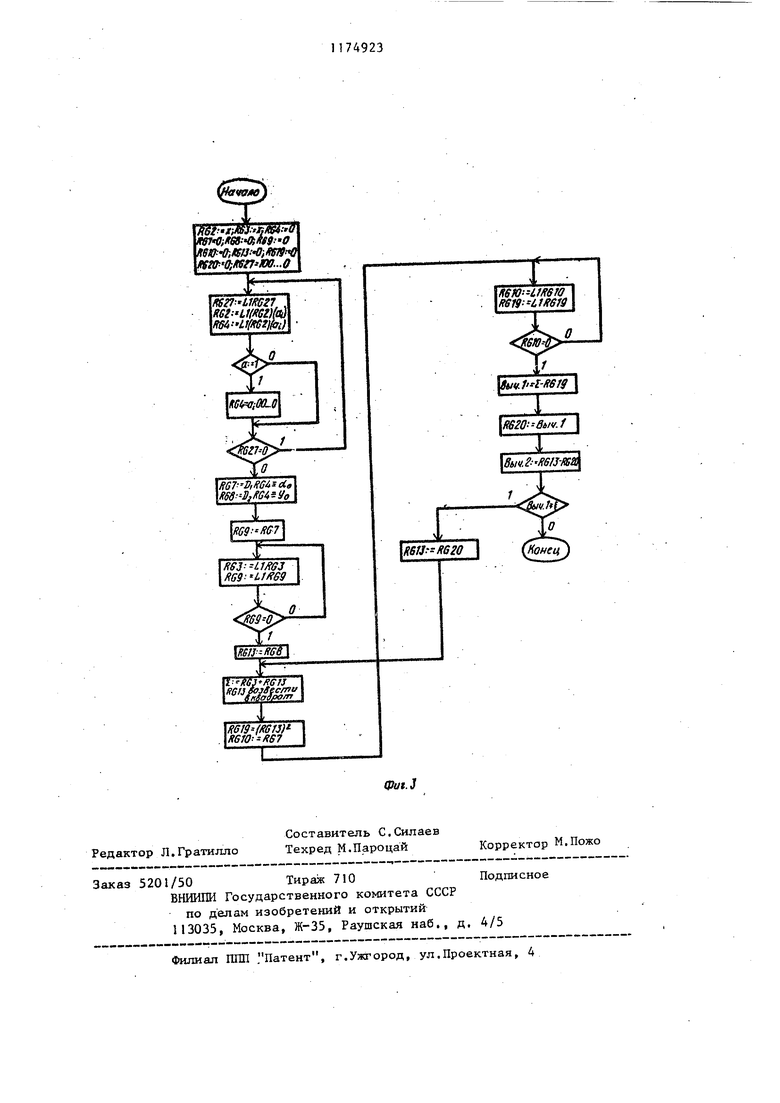

На фиг.1 приведена функциональная схема предлагаемого ycтpoйcтвaj на фиг.2 - вариант функциональной схемы блока управления на фиг.З микропрограмма работы устройства.

Устройство содержит входную шину 1, сдвигающие регистры 2-4, линию 5 задержки, элементы 6.1,..Я,6.е, регистры 7 и 8, сдвигающие регистры 9 и 10, группу элементов И 11, группу элементов ИЛИ 12, регистр 13, группу элементов И 14, квадратор 15, вычитатель 16, сумматор 17, вычитатель 18, сдвигающий регистр 19, регистр 20, выходную шину 21, блок 22 сравнения, олок 23 установки точноети вычислений, выходную шину 24, блок 25 управления и входную шину 26

Блок управления устройства содержит сдвигаюш Ий регистр 27, входную шину 28, триггер 29,генератор 30, элементы И 31-35, распределитель 36

импульсов, шифратор 37,элемент 38 задержки, триггер 39, элемент И 40, распределитель 41 импульсов, триггер 42, входную шину 43, элемент 44 задержки, триггер 45-, элемент И 46, распределитель 47 импульсов, триггер 48, элемент 49 задержки, триггер 50, элемент И 51, распределитель 52 импульсов, формирователь 53 импульсов, триггеры 54 и 55, элемент И 56, триггер 57, элемент 58 задержки, распределитель 59 импульсов, входные шины 60 и 61, выходные шины 62 - 74.

Устройство реализует итерационный алгоритм

х к

УК

(1)

УК

K + I к К об где X - значение входного числа; . - значение начального коэффициента.

Известно, что итерационный процесс у (f/Уг,/ будет сходимым, если выполняется условие

(2)

В данном случае Ср / уЛ 1 2у.

- -п-, поэтому выбор начальных коэфициентов с соотношением о 2 у, позволяет для каждого значения числа X а заданном интервале получать выполнение условия (2).

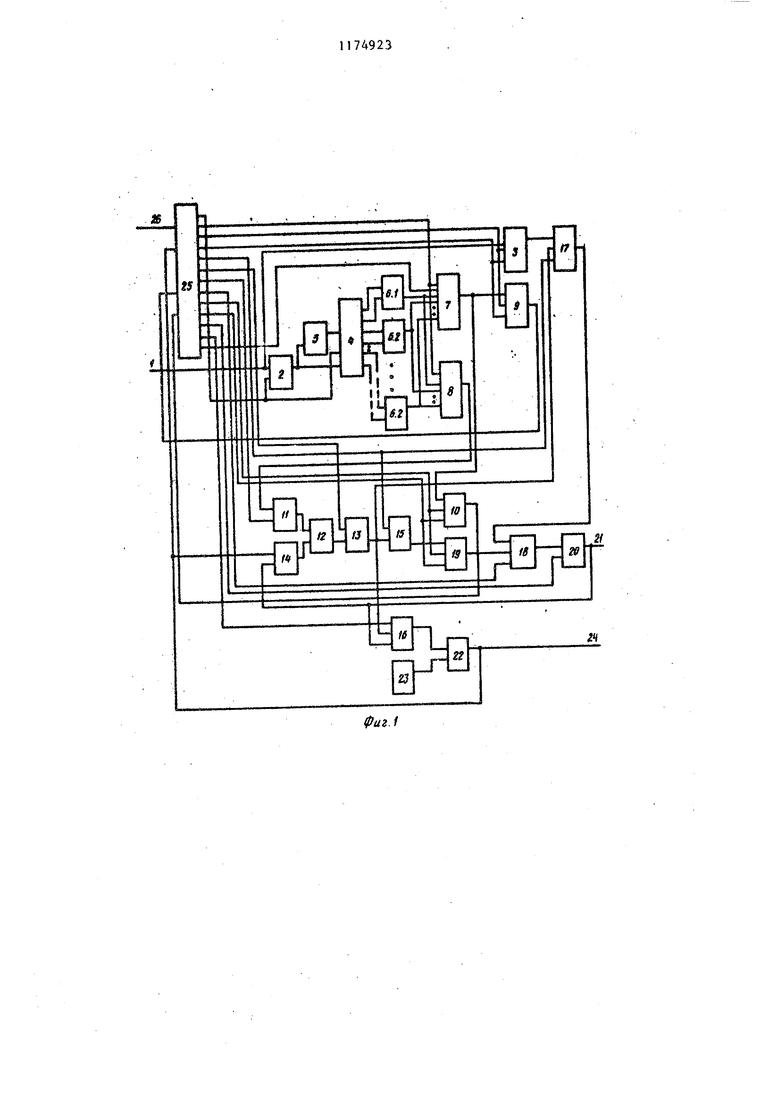

Устройство извлечения квадратного корня работает в соответствии с микропрограммой (фиг.З). Последовательность операций обеспечивается блоком управления. Генератор 30 обеспечивает серию служебных импульсов, с помощью которых осуществ- яется продвижение распределителей 36, 41, 47, 52 и 59. Распределители через триггеры 39 45, 50 и 57 и элементы И 31-35передают управление друг другу в соответствии с микропрограммой и вырабатывают на своих выходах последовательность сигналов,.которые поступают на шиф- ратор 37. Последний вьщает управляю щие сигналы на соответствующие блоки устройства для выполнения команд ьдакропрограммы. Осведомительные сигналы Xj- Х, поступаюш;ие от блоков устройства, обеспечивают с помощью, триггеров 42, 48, 54 и 55 переход с одного цикла микропрограммы на другой. Часть микропрограммы с осведомительным сигналом Х.| реализуется в устройстве на регистрах 2 и 4 и на элементе 5 задержки.

Входная шина 1 служит для ввода в устройство п-разрядного числа X . Регистр 4 служит для определения перво го приближения числа X , которое является основой для определения началных коэффициентов РС и у. К .входу младшего разряда регистра 7 подключена пшнаот блока управления, с помощью которой в мпадший разряд регистра 7 заносится О перед каждым вычислением корня. Подключение выходов группы элементов ИЛИ 6 к входам регистjOB 7 и 8 обеспечивает получение начальных коэффициентов оС и у ( в процессе определения первого приближения числа X ; В регистре 7 хранится значение коэффициента об, а в регистре 8 - У(5. Блок 23 установки точ ности вычислений представляет собой регистр с помощью которого устанавливается требуемое значение погрещности вычислений.

По команде Пуск все регистры устройства устанавливаются в исходное состояние фиг.З).и по сигналу с первого, выхода блока 25 управления начинается определение оС и у,. Содержимое регистра 27 продвигает ся в соответствии с серией импульсов с первого гзыхода шифратора 37, а содержимое регистра 2заносится в

регистр 4 в соответствии с той же серией импульсовi Запись в регистр 4 происходит следующим образом. При поступлении на вход регистра 4 сигнала с нулевым уровнем содержимое регистра 4 сдвигается на один разряд при появлении сигнала с единичным уровнем содержимое регистра 4 обнуляется, а через элемент 5 задержки в старший разряд регистра 4 записывается единица. Таким образом после окончания занесения информации из ре .гистра 2 в регистр 4, а э.то произой.дет после выявления на выходе регистра 27 сигнала с единичным уровнем, в регистре 4 сформируется первое приближение числа X, которое представляет собой число X -j округленное до старшего значащего разряда. После появления на выходе регистра 27 единичного сигнала блок 25 управления выдает команду на занесение содержимого регистра 4 в регистры 7 и 8. .,

Коэффициент «; поступает на входы сдвигающих регистров 9 и 10. С помощью регистров 3 и 9 осуществляет j ся получение компоненты --;- (1). По

сигналу с третьего выхода блока 25 управления в регистр 3 записывается число X , а в регистр 9 - коэффициг ент OU . С четвертого выхода блока 25 подается серия импульсов, с помощью которых осуществляется сдвиг информации влево в регистрах 3 и 9. Как только содержимое регистра 9 станет равным нулю,.сдвиг информации прекратится и в регистре 3 окажется сформированным слагаемое Х/о6 выражения (1). Содержимое регистра 8 через группу элементов И 11 и группу элементов ИЛИ 12, поступает на входы регистра 13 и по сигналу с шестого выхода блока 25 управления заносится в регистр 13. По сигналу с седьмого выхода-в устройстве производятся параллельные суммирование содержимого регистров 3 и 13в сумматоре 17 и возведение в квадрат содержимого регистра 13.

По. сигналу с десятого выхода блока 25 заносится информация в регистры 10 и 19, которые служат для

У

получения слагаемого --,- () Получение слагаемого --- происходит анал

логично получению --- . По сигналу с

06

восьмого выхода блока 25 в вычитателе 18 происходит формирование разности между содержимым сумматора 17 и регистра 19, которая с выхода вычитателя 18 подается на вход регистра 20 по сигналу с одиннадцатого выхода блока 25 управления. Епок управления после занесения информации на .регистр 20, вьфабатывает сигнал, инициирующий вычитание из содержимого регистра 13 содержимого регистра 20. Результат вычитания,, представляющий собой погрешность вычисления корня числа X на первом цикле., сравнивается с заданным значением погрешности при помощи блока 22 сравнения. Если погрешность полученного результата, меньше заданной, блок 22 сравнения

выдает сигнал об окончании вычислений и признак окончания операции извлечения корня выставляется на шине АiРезультат вычисления снимается с шины 21. Если погрешность полученного результата больше или равна заданной, то содержимое регистра 20 через группу элементов И 14 заносится в регистр 13 по сигналу блока управления. Затем блоком управления выдается си. нал в сумматор 17 и квадратор 15 и далее цикп вычислений повторяется с той разницей, что для вычислений используется коэффициент У(- вместо УО .

Устройство может вести вычисления требуемой точностью квадратного корня числа X при X , изменяющемся дискретно в диапазоне ( , .2).

гу

1Лw

i

да

II f

SV

|ЩТ

J и

IM

№

2f

I

16

гн

| Устройство для извлечения квадратного корня | 1977 |

|

SU684540A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функции у= х | 1976 |

|

SU593210A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-23—Публикация

1983-11-09—Подача