Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на цилиндрических магнитных доменах (ЦМД)..

Целью изобретения является упрощение устройства для обхода дефектных регистров в доменной памяти и повышение его быстродействия.

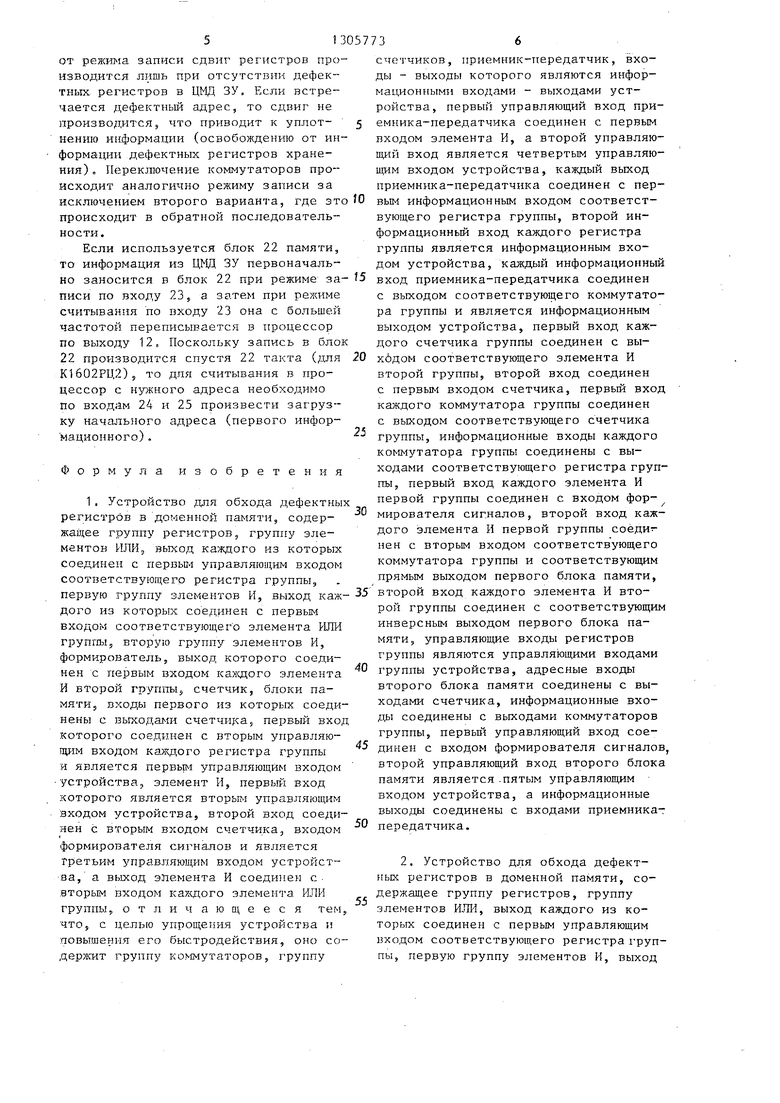

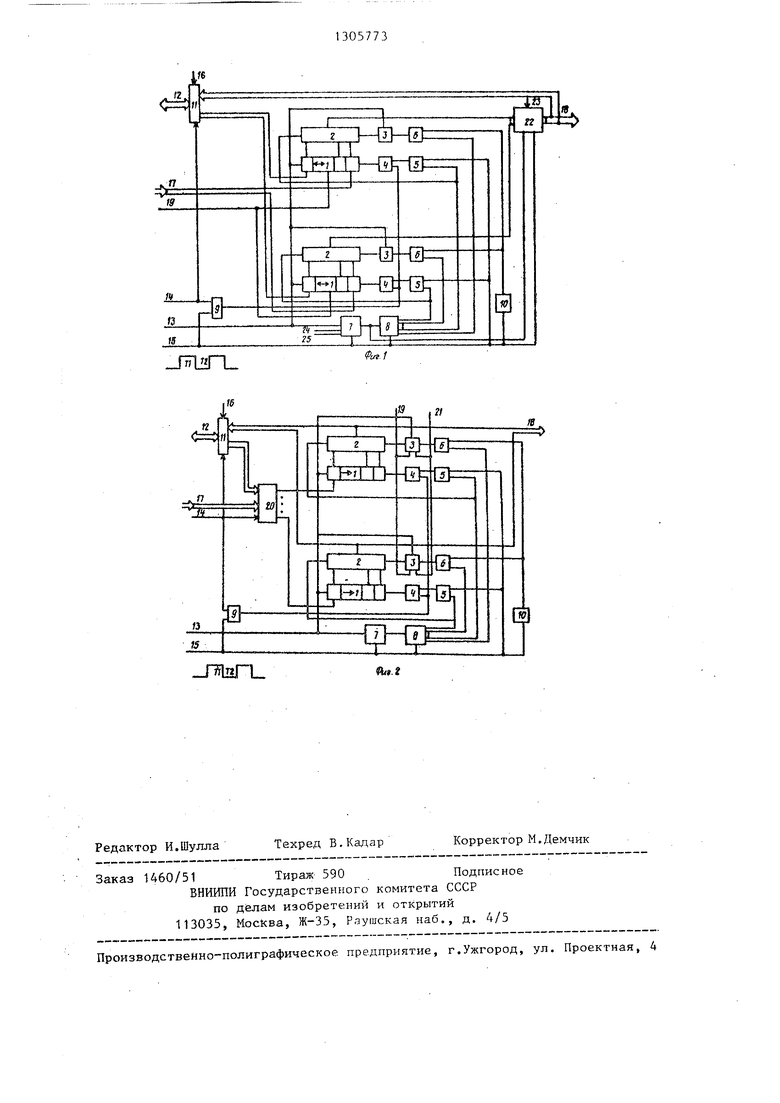

На фиг.1 изображена блок-схема предлагаемого устройства, первый вариант; на фиг.2 - то же, без второго блока памяти (второй вариант).

Предлагаемое устройство в обоих « вариантах содержит группу регистров 1, группу коммутаторов 2, группу счетчиков 3, группу элементов ИЛИ 4, первую 5 и вторую 6 группы элементов И, счетчик 7, первый блок 8 памяти, эл е- мент И 9, формирователь 10, приемникпередатчик 11, информационные входы - выходы 12 устройства, первый 13, второй 14, третий 15 и четвертый 16 управляющие входы устройства, информационные входы 17 и выходы 18 устрой- ства, первую группу управляющих входов 19, коммутатор 20, вторую группу управляющих входов 21, второй блок 22 памяти, пятый управляющий 23, шестой управляк)щий 24 входы устройства и третью группу управляющих входов 25.

35

Регистры 1 могут быть выполнены на ИС К155ИР13, коммутаторы 2 - на НС К155КП1, счетчики 3 - на ИСК155ИЕ5 для первого варианта и на ИС К531 НЕ 17П для второго варианта, элементы ИЛИ - на ИС К155ЛЛ1, элементы И 5 и 6 - на С К155ЛИ1, счетчик 7 - на ИС К155ИЕ5 Q (К531ИЕ17П для второго варианта с блоком 22 памяти), первый блок 8 памяти может быть вьтолнен на БИС К556РТ7 и регистре К155ТМ7 (или с инверторами на ИС К155ЛН1) или на ГШМ , К556РТ1 - одна ПЛМ для двух регистров при использовании ЦМД микросборок типа К1602РЦ2, формирователь 10 может быть вьтолнен или на инверторе (ИС К155ЛН1), или на двух последовательно включенных одновибраторах на ИС К155АГ1, причем на входе каждого из них включается дифференциальная цепочка (один - для задержки, а другой - для фop шp6вaния длительности импульса), приемник-передатчик - на ИС К589АП16, второй блок памяти - на ВИС К541РУ2, коммутатор 20 - на ИС К531КП11.

55

5

Q ,

5

Первьш блок 8 памяти используется для хранения карты годности (номер дефектных регистров) и может быть выполнен на РПЗУ и регистре, как в известном устройстве, когда стробирую- щий вход регистра подключается к входу формирователя, его выходы (прямые и инверсные) являются выходами блока, а входы соединены с выходами РПЗУ, входы которого являются входами блока. Вместо регистра могут быть использованы инверторы для получения инверсных выходов у РПЗУ. Кроме того, блок памяти 8 может быть выполнен на ПЛМ (группе ПЛМ), каждая из которых подключается к своему регистру через элемент И,

Предлагаемое устройство работает следующим образом.

В режиме записи информации в ЦМД ЗУ (при отсутствии блоков 22 памяти) перед записью информации на первый управляющий вход 13 необходимо подать сигнал начальной установки, по окончании которого регистр 1, счетчики 3 и 7 устанавливаются в исходное (нулевое) состояние. Причем во втором варианте установка счетчика 3 производится иначе. На входах 19 устанавливается режим параллельного занесения информации, а на входах 21 - нулевой код. После подачи сигнала на вход 13, он поступает на счетчик (для ИС К531ИЕ17П совместно с сигналом с выхода элемента И 6 через элемент ИЛИ (не показан, поскольку необходим только при данной реализации счетчика), производя его обнуление. После этого на входах 19 устанавливают код управления счетчиков в режиме суммирования. На второй вход 14 подается сигнал ЗП (Лог. 1), а на третий вход 15 подают синхросерию с частотой 100 кГц для ЦМД типа К1602РЦ2. На четвертьш вход подается разрешающий потенциал. Сдвиг в регистрах 1 для первого варианта по входам 19 устанавливается вправо (по фиг.1).

Синхронно с огактом Т1 на входы 12 необходимо подавать байты информации (если обмен происходит байтами), По переднему фронту такта Т1 каждый разряд слова записывается по второму входу соответствующего регистра 1. При этом, если нет дефектных рег ист- ров, на прямых входах блока 8 присутствуют разрешаю1цие потенциалы, открывающие коммутаторы 2. Синхросерия

313

через элемент И 9 и элементы ИЛИ 4 поступает на первый управляющий нход регистров 1, осуодествляя прием и сдвиг информации в каждом такте. При этом счетчик 3 сохраняет нулевое сое- тояние, вследствие чего коммутаторы 2 всегда открыты по первому входу (левому на фиг.1), и информация после занесения в регистры 1 через коммутатор 2 поступает на выход 18 и далее в ЦМД ЗУ. Поскольку задержки в элементах невелики, то информация поступает в ЦМД ЗУ практически одновременно с тактом Т1, осуществляющим занесение информации в ЦМД ЗУ.

Смена адресов в счетчике 7 происходит по окончании такта Т1, и до поступления нового такта Т1 на выходе блока 8 устанавливается код наличия или отсутствия дефектного регистра по следующему адресу, к которому будет обращение в следующем такте.

Если в очередном такте Т1 встретится дефектный регистр, то на прямом выходе соответствующего разряда бло- кг 8 логический О, а на инверсном - логическая 1. Информация по переднему фронту Т1 записывается в регистр 1, но коммутатор 2 закрыт по второму входу, и на выход 18 поступает сигнал нуля. В течение такта Т2 формирователь 10 вырабатывает сигнал, который через открытый .элемент 6 переключает соответствующий счетчик 3 в следующее состояние, а перед приходом так- та Т1 соответствующий коммутатор открывается по следующему входу, вследствие чего информация, поступающая через первый информационный вход этого регистра, до следующего дефектно- го регистра в ЦМД ЗУ поступает через коммутатор 2 на выход 1В по этому входу. При следующем дефектном адресе открывается следующий вход и т.д. Количество разрядов в регистре 1 и входов у коммутатора 2 должно быть на единицу больше возможного числа дефектных регистров в ЦМД ЗУ.

Отличие работы устройства по вто- рому варианту заключается в том, что информация поступает через приемник- передатчик не непосредственно на входы регистров 1, а через коммутатор 20

Отличие работы устройства с блоками 22 памяти заключается в том, что информация, первоначально разбавленная нулями в блоках 1 и 2, поступает на запись в блок 22 памяти, кото734

рьй имеет малое время обращения, вследствие чего занесение информации происходит в 10-15 раз быстрее, чем при непосредственной записи в ЦМД ЗУ. Д-пя этого на входе 23 устанавливают режим записи в блок 22. В этом случае частота обмена существенно увеличивается, что освобождает процессор от взаимодействия по обмену информацией с ЦМД ЗУ. После занесения информации в блок 22 необходимо обнулить счетчик 7, установить сигнал считьшания по входу 23 и подать на вход- 14 частоту, соответствующую рабочей частоте ЦМД ЗУ. Считьшаемая из блока 22 информация записывается в ЦМД ЗУ. С входа 16 сигнал разрешения можно снять После окончания записи во всех вариантах необходимо произвести остановку

В режиме считывания информации из Ш-Щ ЗУ (при отсутствии блоков 22 памяти) информация поступает из ЦМД ЗУ по входам 17 устройства. Поскольку она может быть задержана относительно поступления синхросерии на вход 15 можно осуществить задержку синхросерии, поступающей на вход 13 с помощью двух одновибраторов, выполненных на ИС К155АГ16, между которыми и на входе первого включить необходимо дифференциальную цепочку. Первый одновибратор позволит задержать импульс, а второй - выработать импульс нужно длительности. Во втором варианте информация поступает через коммутатор 20 на тот же, что и при записи, вход регистра 1, поскольку он, как и в режиме записи, сдвигается вправо (по фиг.2). В первом варианте информация при считывании поступает на второй информационный вход регистра 1, которьш в данном случае сдвигается влево после подачи соответствующих управляющих сигналов на входы 19.

В первом варианте коммутатор 2 работает аналогично работе при записи информации, а во втором варианте - наоборот, т.е. первоначально включается последний (правый на фиг.2) вход, что достигается начальной установкой счетчика 3 по шинам 19 и 21. После начальной установки по входам 19 необходимо установить режим работы счетчика в режиме вычитания.

После поступления синхросерии информация заносится в регистры 1 по соответствующим входам, но в отличие

от режима записи сдвиг регистров производится лишь при отсутствии дефектных регистров в ЦМД ЗУ. Если встречается дефектный адрес, то сдвиг не производится, что приводит к уплот- 5 нению информации (освобождению от информации дефектных регистров хранения) . Переключение коммутаторов происходит аналогично режиму записи за исключением второго варианта, где это JO происходит в обратной последовательности.

Если используется блок 22 памяти, то информация из ЦМД ЗУ первоначальсчетчиков, приемник-передатчик, входы - выходы которого являются информационными входами - выходами устройства, первый управляющий вход при емника-передатчика соединен с первым входом элемента И, а второй управляю 1ДИЙ вход является четвертым управляю щим входом устройства, каждый выход приемника-передатчика соединен с пер вым информационным входом соответствующего регистра группы, второй ин- формационньш вход каждого регистра группы является информационным входом устройства, каждый информационны

но заносится в блок 22 при режиме за- 5 вход приемника-передатчика соединен писи по входу 235 а затем при режиме считывания по входу 23 она с большей частотой переписывается в процессор по выходу 12, Поскольку запись в блок 22 производится спустя 22 такта (для 20 K1602PU,2)5 то для считывания в процессор с HjoKHoro адреса необходимо по входам 24 и 25 произвести загрузку начального адреса (первого инфор23

с выходом соответствующего коммутато ра группы и является информационным выходом устройства, первый вход каждого счетчика группы соединен с вы- хбдом соответствующего элемента И второй группы, второй вход соединен с первым входом счетчика, первый вхо каждого коммутатора группы соединен с выходом соответствующего счетчика группы, информационные входы каждого коммутатора группы соединены с выходами соответствующего регистра гру пы, первый вход каждого элемента И первой группы соединен с входом формирователя сигналов, второй вход каж дого элемента И первой группы соединен с вторым входом соответствующего коммутатора группы и соответствующим прямым выходом первого блока памяти,

мационного) .

Формула изобретения

1. Устройство для обхода дефектных регистров в доменной памяти, содер- жахцее группу регистров, группу элементов ИЛИз выход каждого из которых соединен с первьш управляющим входом соответствующего регистра группы

30

с выходом соответствующего коммутато ра группы и является информационным выходом устройства, первый вход каждого счетчика группы соединен с вы- хбдом соответствующего элемента И второй группы, второй вход соединен с первым входом счетчика, первый вхо каждого коммутатора группы соединен с выходом соответствующего счетчика группы, информационные входы каждого коммутатора группы соединены с выходами соответствующего регистра гру пы, первый вход каждого элемента И первой группы соединен с входом формирователя сигналов, второй вход каж дого элемента И первой группы соединен с вторым входом соответствующего коммутатора группы и соответствующим прямым выходом первого блока памяти,

первую группу элементов И, выход каж- 35 второй вход каждого элемента И втодого из которых соединен с первым вxoдo s соответствующего элемента РШИ группы, вторую группу элементов И, формирователь, выход которого соединен с первым входом каходого элемента И второй группЫг счетчик, блоки памяти, входы первого из которых соединены с выходами счетчи1 :а5 первый вход которого соединен с вторым управляющим входом ка-ждого регистра группы и является первьм управляющим входом устройства, элемент И, первый Вход которого является вторым управляющим входом устройства, второй вход соединен с вторым входом счетчика, входом формирователя сигналов и является Третьим управляющим входом устройства, а выход элемента И соединен с. вторым входом казгодого элемента ИЛИ группы, отличающееся тем что, с целью упрощения устройства и повышения его быстродействия, оно содержит группу коммутаторов, группу

счетчиков, приемник-передатчик, входы - выходы которого являются информационными входами - выходами устройства, первый управляющий вход приемника-передатчика соединен с первым входом элемента И, а второй управляю- 1ДИЙ вход является четвертым управляющим входом устройства, каждый выход приемника-передатчика соединен с первым информационным входом соответствующего регистра группы, второй ин- формационньш вход каждого регистра группы является информационным входом устройства, каждый информационный

вход приемника-передатчика соединен

с выходом соответствующего коммутатора группы и является информационным выходом устройства, первый вход каждого счетчика группы соединен с вы- хбдом соответствующего элемента И второй группы, второй вход соединен с первым входом счетчика, первый вход каждого коммутатора группы соединен с выходом соответствующего счетчика группы, информационные входы каждого коммутатора группы соединены с выходами соответствующего регистра группы, первый вход каждого элемента И первой группы соединен с входом фор мирователя сигналов, второй вход каждого элемента И первой группы соединен с вторым входом соответствующего коммутатора группы и соответствующим прямым выходом первого блока памяти,

рои группы соединен с соответствующим инверсным выходом первого блока памяти, управляющие входы регистров группы являются управляющими входами группы устройства, адресные входы второго блока памяти соединены с выходами счетчика, информационные вхо- д)I соединены с выходами коммутаторов группы, первьш управляющий вход сое- динен с входом формирователя сигналов, второй управляющий вход второго блока памяти является .пятым управляющим входом устройства, а информационные выхода соединены с входами приемника- передатчика.

2, Устройство для обхода дефект- Ftbix регистров в доменной памяти, содержащее группу регистров, группу элементов ИЛИ, выход каждого из которых соединен с первым управляющим входом соответствующего регистра группы, первую группу элементов И, выход

кяждого из которых соединен с первым входом соответствующего элемента ИЛИ группы, вторую группу элементов И, формирователь сигналов, выход которого соединен с первым входом каждого элемента И второй группы, счетчик, блоки памяти, входы первого из которых соединены с выходами счетчика, первый вход которого соединен с вторым управляющим входом каждого регис- О вующим входом приемника-передатчика

тра группы и является первым управляющим входом устройства, элемент И, первый вход которого является вторым управляющим входом устройства, второй вход соединен с вторым входом f5 счетчика, входом формирователя сигналов и является третьим управляющим входом устройства, а выход элемента И соединен с вторым входом каждого элемента ИЛИ группы, отличающееся тем, что, с целью упрощения устройства и повьшения его быстродействия, оно содержит группу коммутаторов, группу счетчиков, коммутатор, приемник-передатчик, входы- выходы которого являются информационными входами-выходами устройства, первый управляющий вход приемник редатчика соединен с управляющим входом коммутатора и первым входом эле- 30 мента И, второй управляющий вход приемника-передатчика является четвертым управляющим входом устройства, входы первой группы коммутатора являются информационными входами устройства, а входы второй группы соединены с выходами приемника-передатчика, информационный вход каждого регистра группы соединен с соответствуи является информационным выхо устройства, второй вход каждог мента И второй группы соединен ответствующим инверсным выходо вого блока памяти, первый вход дого элемента И первой группы нен с входом формирователя сиг второй вход калсдого элемента И группы соединен с вторьм управ щим входом соответствующего ко тора группы и соответствующим выходом первого блока памяти, и мационные входы каждого коммут группы соединены с выходами со ствующего регистра группы, упр щие входы счетчиков группы явл управляющими входами первой гру устройства, а информационные в счетчиков группы являются упра ми входами второй группы устрой адресные входы второго блока па соединены с выходами счетчика, формационные входы соединены с дами коммутаторов группы, первы 35 равляющий вход соединен с входо формирователя, второй управляющ вход второго блока памяти являе пятым управляющим входом устрой а информационные выходы соедине

20

25

ющим выходом коммутатора, первый уп- 40 входами приемника-передатчика.

равляющни вход каждого коммутатора -группы соединен с выходом соответствующего счетчика группы, первый вход каждого счетчика группы соединен с выходом соответствующего элемента И второй группы, второй вход каждого счетчика группы соединен с первым входом счетчика, -выход каждого коммутатора группы соединен с соответст50

и является информационным выходом устройства, второй вход каждого элемента И второй группы соединен с соответствующим инверсным выходом первого блока памяти, первый вход каждого элемента И первой группы соединен с входом формирователя сигналов, второй вход калсдого элемента И первой группы соединен с вторьм управляющим входом соответствующего коммутатора группы и соответствующим прямьм выходом первого блока памяти, информационные входы каждого коммутатора группы соединены с выходами соответствующего регистра группы, управляющие входы счетчиков группы являются управляющими входами первой группы устройства, а информационные входы счетчиков группы являются управляющими входами второй группы устройств а, адресные входы второго блока памяти соединены с выходами счетчика, информационные входы соединены с выходами коммутаторов группы, первый уп- 5 равляющий вход соединен с входом формирователя, второй управляющий вход второго блока памяти является пятым управляющим входом устройства, а информационные выходы соединены с

0

5

Фиг.1

jt9 j,

-ЛЯдП.

t.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1352496A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357967A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357966A1 |

| Устройство сопряжения процессора с памятью | 1985 |

|

SU1357968A1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Устройство для переадресации информации | 1981 |

|

SU1001177A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Устройство формирования маскирующих сигналов для доменной памяти | 1987 |

|

SU1429165A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

Изобретение касается вычислительной техники и может быть использовано при построении запоминающих устройств на цилиндрических магнитных доменах. Цель изобретения - упрощение устройства для обхода дефектных регистров в доменной памяти и повышение его быстродействия. Предлагаемое устройство в обоих вариантах исполнения содержит группу .регистров, группу коммутаторов, группу счетчиков, группу элементов ИЛИ, первую и вторую группы элементов И, счетчик, первьш блок памяти, элемент И, формирователь, приемник-передатчик, ин- формационные входы - выходы устройства, управляющие входы,информационные выходы устройства, группы управляющих входов коммутатора, блок памяти. 2 с,п, ф-лы, 2 ил. SS СО О СП. --J СО

| Патент США № 4073012, кл.365-15, опублик | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| ) УСТРОЙСТВО ДЛЯ ОБХОДА ДЕФЕКТНЫХ РЕГИСТРОВ В ДОМЕННОЙ ПАМЯТИ (ЕГО ВАРИАНТЫ) | |||

Авторы

Даты

1987-04-23—Публикация

1985-04-29—Подача