4::

to

Р

СП

I Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на цилиндрических магнитных доменах (ЦМД)о

Целью изобретения является повышение надежности устройства.

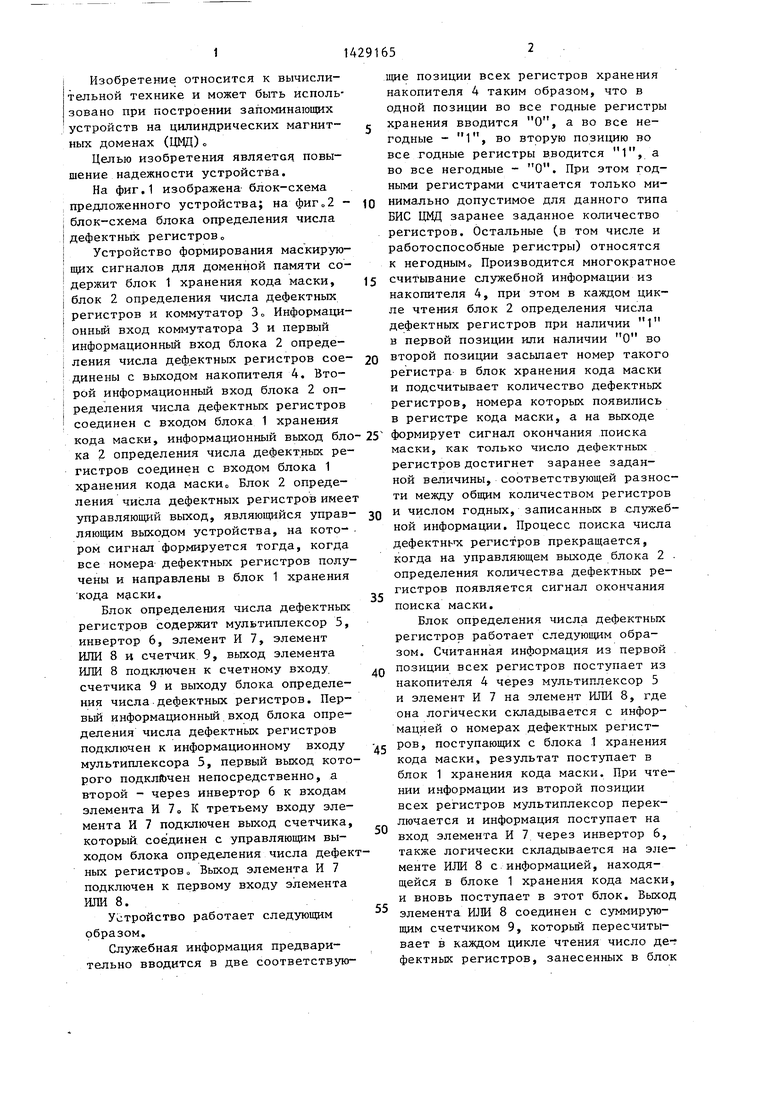

На фиг,1 изображена блок-схема предложенного устройства; на фиг«2 - I блок-схема блока определения числа дефектных регистров I Устройство формирования маскирую- ; щих сигналов для доменной памяти со- ; держит блок 1 хранения кода маски, i блок 2 определения числа дефектных I регистров и коммутатор 3 Информаци- I онный вход коммутатора 3 и первый ; информационный вход блока 2 опреде- I ления числа дефектных регистров сое- динены с выходом накопителя 4. Вто- I рой информационный вход блока 2 оп- i ределения числа дефектных регистров соединен с входом блока 1 хранения кода маски, информационный выход блока 2 определения числа дефектных регистров соединен с входом блока 1 хранения кода маски Блок 2 определения числа дефектных регистро в имее управляющий выход, являющийся управляющим выходом устройства, на кото- ром сигнал формируется тогда, когда все номера дефектных регистров получены и направлены в блок 1 хранения кода маски.

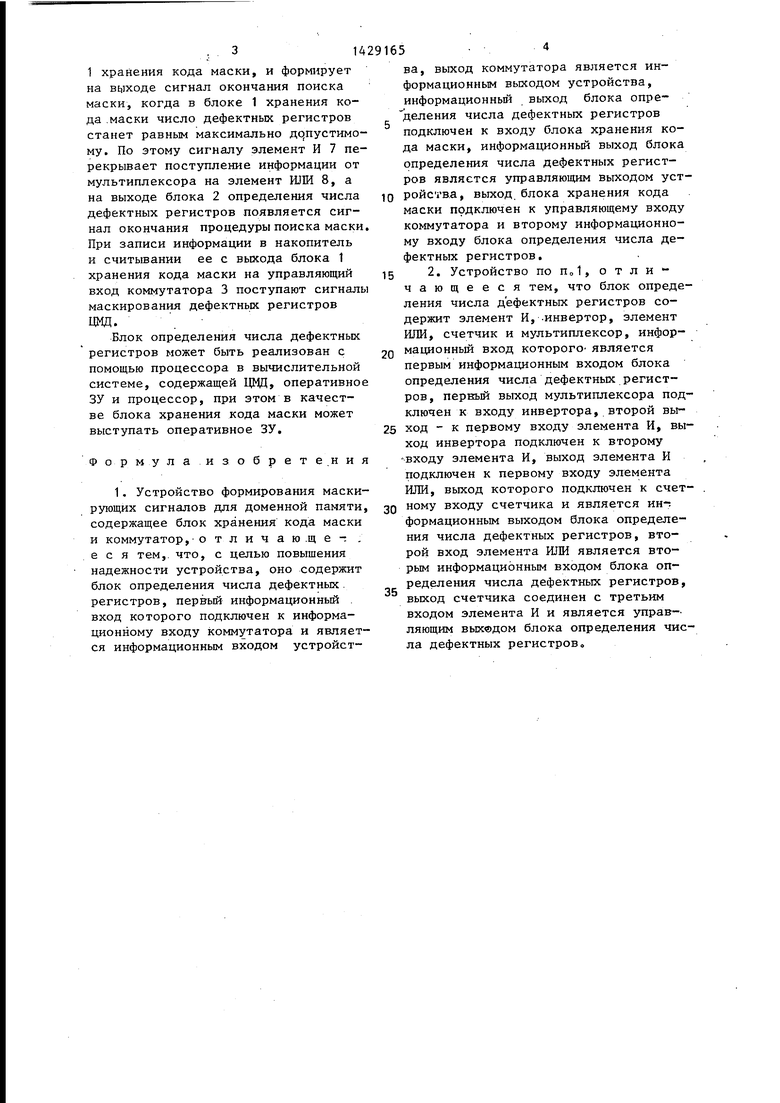

Блок определения числа дефектных регистров содержит мультиплексор 5, инвертор 6, элемент И 7, элемент ИЛИ 8 и счетчик 9, выход элемента ИЛИ 8 подключен к счетному входу, счетчика 9 и выходу блока определения числа дефектных регистров. Первый информационньй.вход блока определения числа дефектных регистров подключен к информационному входу мультиплексора 5, первый выход которого подключен непосредственно, а второй - через инвертор 6 к входам элемента И 7 К третьему входу элемента И 7 подключен выход счетчика, который соединен с управляющим выходом блока определения числа дефекных регистров о Выход элемента И 7 подключен к первому входу элемента ИЛИ 8.

Устройство работает следующим образом.

Служебная информация предварительно вводится в две соответствующие позиции всех регистров хранения накопителя 4 таким образом, что в одной позиции во все годные регистры

хранения вводится О, а во все негодные - 1, во вторую позицию во все годные регистры вводится 1, а во все негодные - О. При этом годными регистрами считается только минимально допустимое для данного типа БИС ЦМД заранее заданное количество регистров. Остальные (в том числе и работоспособные регистры) относятся к негодным Производится многократное

считывание служебной информации из накопителя 4, при этом в каждом цикле чтения блок 2 определения числа дефектных регистров при наличии 1 в первой позиции или наличии О во

второй позиции засыпает номер такого регистра в блок хранения кода маски и подсчитывает количество дефектных регистров, номера которых появились в регистре кода маски, а на выходе

формирует сигнал окончания поиска маски, как только число дефектных регистров достигнет заранее заданной величины, соответствующей разности между общим количеством регистров

и числом годных, записанных в служебной информации. Процесс поиска числа дефектньтс регистров прекращается, когда на управляющем выходе блока 2 . определения количества дефектных регистров появляется сигнал окончания поиска маски.

Блок определения числа дефектных регистров работает следующим образом. Считанная информация из первой

позиции всех регистров поступает из накопителя 4 через мультиплексор 5 и элемент И 7 на элемент ИЛИ 8, где она логически складывается с информацией о номерах дефектных регистров, поступающих с блока 1 хранения кода маски, результат поступает в блок 1 хранения кода маски. При чтении информации из второй позиции всех регистров мультиплексор переключается и информация поступает на вход элемента И 7 через инвертор 6, также логически складывается на элементе ИЛИ 8 с информацией, находящейся в блоке 1 хранения кода маски, и вновь поступает в этот блок. Выход

элемента ИЛИ 8 соединен с суммирующим счетчиком 9, которьм пересчитывает в каждом цикле чтения число дефектных регистров, занесенных в блок

1 хранения кода маски, и форм11рует на вуходе сигнал окончания поиска маски, когда в блоке 1 хранения кода .маски число дефектных регистров станет равным максимально дqпycтимo- му. По этому сигналу элемент И 7 перекрывает поступление информации от мультиплексора на элемент ШШ 8, а на выходе блока 2 определения числа дефектных регистров появляется сигнал окончания процедуры поиска маски При записи информации в накопитель и считывании ее с выхода блока 1 хранения кода маски на управляющий вход коммутатора 3 поступают сигналы маскирования дефектньк регистров

днц. .

Блок определения числа дефектных регистров может быть реализован с помощью процессора в вычислительной системе, содержащей ЦМД, оперативное ЗУ и процессор, при этом в качестве блока хранения кода маски может выступать оперативное ЗУ.

Формулаизобрете.ния

1. Устройство формирования маскирующих сигналов для доменной памяти, содержащее блок хранения кода маски и коммутатор,- отличаю.щ е- . е с я тем,, что, с целью повышения надежности устройства, оно содержит блок определения числа дефектных. регистров, первьй информационный . вход которого подключен к информационному входу коммутатора и является информационным входом устройст0

5

0

5

0

5

ва, выход коммутатора является информационным выходом устройства, информационный выход блока опре- деления числа дефектных регистров подключен к входу блока хранения кода маски, информационньй выход блока определения числа дефектных регистров является управляющим выходом уст- ройс гв.а, выход, блока хранения кода маски подключен к управляющему входу коммутатора и второму информационному входу блока определения числа дефектных регистров.

2. Устройство по Пс,1, отличающееся тем, что блок определения числа дефектных регистров содержит элемент И, -инвертор, элемент ШШ, счетчик и мультиплексор, информационньй вход КОТОРОГО является первым информационным входом блока определения числа дефектных регистров, первъй выход мультиплексора подключен к входу инвертора, второй выход - к первому входу элемента И, выход инвертора подключен к второму ВХОДУ элемента И, выход элемента И подключен к первому входу элемента ИЛИ, выход которого подключен к счетному входу счетчика и является ин-: формационным выходом блока определения числа дефектных регистров, второй вход элемента ИЛИ является вторым информационным входом блока определения числа дефектных регистров, выход счетчика соединен с третьим входом элемента И и является управ-- ляющим выхФдом блока определения числа дефектных регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования маскирующих сигналов для доменной памяти | 1986 |

|

SU1317480A1 |

| Устройство для формирования маскирующих сигналов для доменного запоминающего устройства | 1981 |

|

SU1020861A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1984 |

|

SU1188787A1 |

| Накопитель для запоминающего устройства на цилиндрических магнитных доменах | 1982 |

|

SU1084891A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Устройство для обхода дефектных регистров в доменной памяти (его варианты) | 1985 |

|

SU1305773A1 |

| Устройство для переадресации информации | 1981 |

|

SU1001177A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении дополнительных устройств на цилиндрических магнитных доменах (ЦМД) Целью изобретения является повьппение надежности устройства. Устройство формирования маскирующих сигналов для доменной памяти содержит блок 1 хранения кода маски, блок 2 определения числа дефектных регистров и коммутатор 3. Информационный вход коммутатора 3 и первьш информационный вход блока 2 определения числа дефектных регист- ,ров соединены с выходом накопителя 4. Второй информационный вход блока 2 соединен с входом блока 1 хранения кода маски, информационный выход блока 2 соединен с входом блока 1. Блок определения числа дефектньгх регистров имеет управляю1)ий выход, являющийся управляющим выходом устройства, на котором сигнал формируется тогда, когда все номера дефектных регистров получены и направлены в блок хранения кода маски. 1 з.п. ф-лы, 2 иЛо в (Л

Редактор О.Юрковецкая

Составитель Ю.Роэенталь

Техред Л.Сердюкова Корректор Л.Патай

Заказ 5132/48

Тираж 590

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская каб., д, 4/5

9иг.г

Подписное

| Патент США № 4090251, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Устройство для формирования маскирующих сигналов для доменного запоминающего устройства | 1981 |

|

SU1020861A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-16—Подача