1.13

Изобретение относится к устройствам ввода и обработки циклически повторяющихся аналоговых сигналов, на- npi-iMep видеосигнала от неподвижного телевизионного изображения. Б частности к обработке сигнала, включающего преобразование аналогового изображения в цифровую форму и его запоминание для дальнейшей обработки.

Целью изобретения является увеличение скорости преобразования при сохранении точности преобразования.

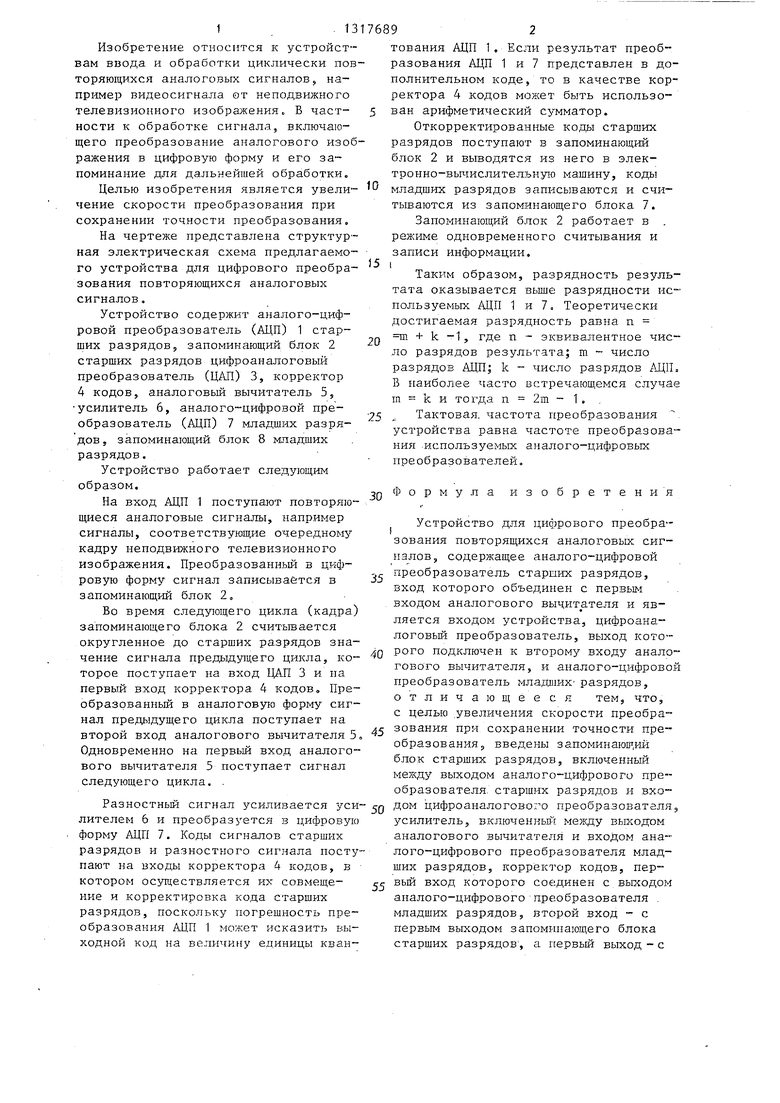

На чертеже представлена структурная электрическая схема предлагаемого устройства для цифрового преобразования повторяющихся аналоговых сигналов.

Устройство содержит аналого-цифровой преобразователь (АЦП) 1 старших разрядов, запоминающий блок 2 старших разрядов цифроаналоговый преобразователь (ЦАП) 3, корректор 4 кодов, аналоговый вычитатель 5, усилитель 6, аналого-цифровой преобразователь (АЦП) 7 младших разря- дов, запоминающий блок 8 младших разрядов.

Устройство работает следующим образом.

На вход АЦП 1 поступают повторяющиеся аналоговые сигналы, например сигналы, соответствующие очередному кадру неподвижного телевизионного изображения. Преобразованньш в цифровую форму сигнал записывается в запоминающий блок 2,

Во время следующего цикла (кадра) запоминающего блока 2 считьшается округленное до старших разрядов значение сигнала предьщущего цикла, которое поступает на вход ЦАП 3 и на первый вход корректора 4 кодов. Преобразованный в аналоговую форму сигнал предыдущего цикла поступает на второй вход аналогового вычитателя5 Одновременно на первый вход аналогового вычитателя 5 поступает сигнал следующего цикла. .

Разностный сигнал усиливается усилителем 6 и преобразуется в цифровую форму АЦП 7. Коды сигналов старших разрядов и разностного сигнала поступают на входы корректора 4 кодов, в котором осуществляется их совмещение и корректировка кода старших разрядов, поскольку погрешность преобразования АЦП 1 может исказить выходной код на величину единицы кван

92

тования АЦП 1. Если результат преобразования АЦП 1 и 7 представлен в дополнительном коде, то в качестве корректора 4 кодов может быть использован арифметический сумматор.

Откорректированные коды старших разрядов поступают в запоминающий блок 2 и выводятся из него в электронно-вычислительную машину, коды

младших разрядов записываются и считываются из запоминающего блока 7.

Запоминающий блок 2 работает в режиме одновременного считывания и записи информации.

Таким образом, разрядность результата оказывается вьш1е разрядности используемых АЦП 1 и 7. Теоретически достигаемая разрядность равна п

т + k -1, где п - эквивалентное число разрядов результата; m - число разрядов АЦП; k - число разрядов АЦП. В наиболее часто встречающемся случае m k и тогда п 2т - 1 . ,

, Тактовая, частота преобразования , устройства равна частоте преобразования используемых аналого-цифровых преобразователей.

30

Формула изобретения

Устройство для цифрового преобразования повторящихся аналоговых сигналов, содержащее аналого-цифровой

преобразователь старших разрядов, вход которого объединен с первым входом аналогового вычитателя и является входом устройства, цифроаналоговый преобразователь, выход которого подключен к второму входу аналогового вычитателя, и аналого-цифровой преобразователь младших разрядов, отличаюа1ее ся тем, что, с целью .увеличения скорости преобразования при сохранении точности преобразования, введены запоминающий блок старших разрядов, включенный между выходом аналого-цифрового преобразователя, старших разрядов и входом цнфроаналогового преобразователя, усилитель, включенньш между выходом аналогового вычитателя и входом аналого-цифрового преобразователя младших разрядов, корректор кодов, первьй вход которого соединен с выходом аналого-цифрового преобразователя , младших разрядов, второй вход - с первым выходом запоминающего блока старших разрядов, а первьй выход - с

313176894

вторым входом запоминающего блока разрядов, вход которого подключен к старших разрядов, второй выход кото- второму выходу корректора, кодов, а рого является выходом старших разря- выход является выходом младших раз- дов, и запоминающий блок младших рядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1319279A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2010 |

|

RU2441317C1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

Изобретение относится к устройствам ввода и обработки циклически повторяющихся аналоговых сигналов и обеспечивает увеличение скорости преобразования при сохранении точности преобразования. Устройство содержит АЦП 1 старших разрядов, запоминающий блок 2 старших разрядов, ЦАП 3, корректор 4 кодов, аналоговый вычи- татель 5, у-ль 6j АЦП 7 младших разрядов, запоминающий блок 8 младших разрядов. Откорректированные коды старших разрядов поступают в блок 2 и выводятся из него в ЭВМ. Коды младших разрядов записываются и считываются из блока 8. Тактовая частота преобразования устройства равна частоте преобразования используемых АЦП. 1 ил. Выход / старших разряаоб Bjto

| Бондаренко Ю.В | |||

| и др | |||

| Система регистрации и ввода в ЭВМ одномерных изображений слабосветящихся объектов и быстропротекающих процессов | |||

| - Автометрия, 1983, № 4 | |||

| Бахтаров Г.А | |||

| и др | |||

| Аналого-цифровые преобразователи | |||

| М.: Советское радио, 1980, с | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-06-15—Публикация

1984-12-25—Подача