11

Изобретение относится к цифровой вычислительной технике и может быть использовано для поиска неисправностей в блоках ЦВМ.

Цель изобретения - повышение достоверности контроля.

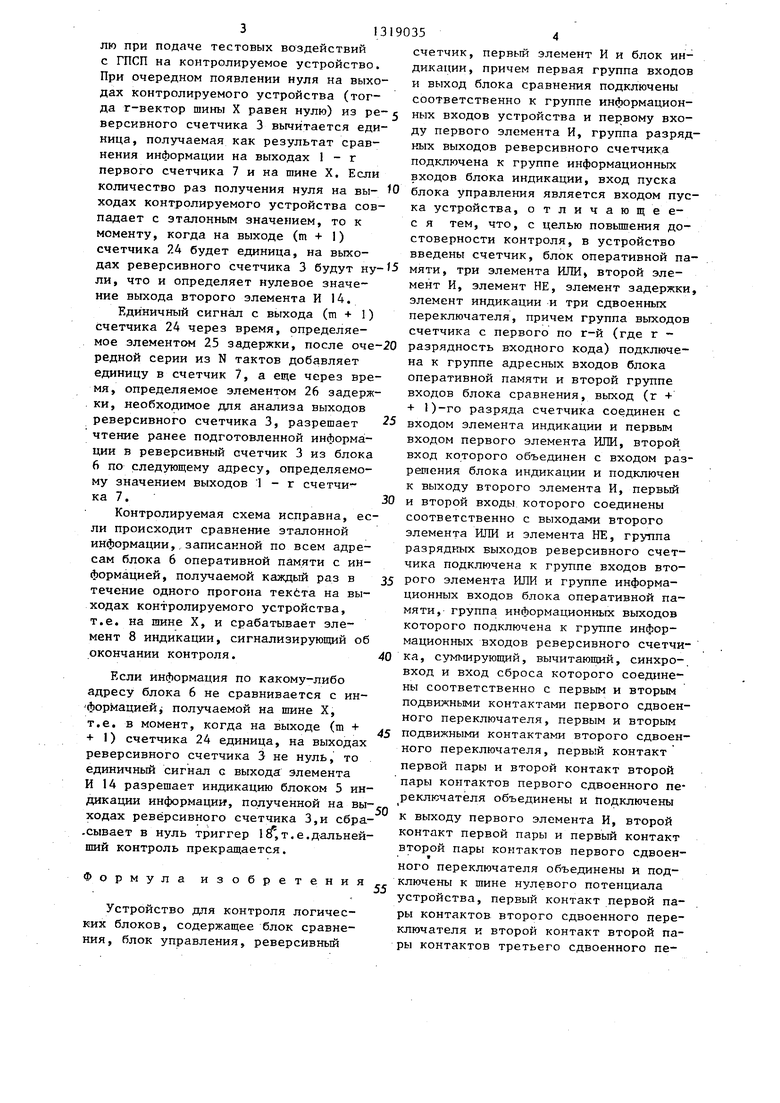

На чертеже представлена функциональная схема устройства.

Устройство содержит блок 1 управления, блок 2 сравнения, реверсивный счетчик 3, первый элемент И 4, блок 5 индикации, блок 6 памяти, счетчик 7, элемент 8 индикации, элемент 9 задержки, первый 10, второй 11 и трети 12 элементы ИЛИ, элемент НЕ 13, вто- .рой элемент И 1Д, сдвоенные переключатели 15-17.

Блок управления содержит триггер 18, одновибратор 19, лервый элемент И .0, генератор 21 гактовых импульсов, элементы ИЛИ 22- - 23, счетчик 24, элементы 25 - 26 задержки, второй элемент И 27,

Блок сравнения содержит г-входо- вой элемент ИЛЙ-НЕ 28 и г сумматоров 29 - 29.г по модулю два.

Устройство работает -в режиме под- готовки данных и в режиме контроля следующим образом.

При работе схемы в режиме подготовки данных для последующего контро ля берут заведомо исправную схему. Переключатели 15 и 17 находятся в верхнем положении, а переключатель 16 - в нижнем.

По приходу сигнала Пуск триггер 18 устанавливается в единичное состояние и запускает одновибратор 19, который генерирует импульс сброса, переводящий реверсивный счетчик 3 и счетчики 7 - 24 в исходное состояние По окончании импульса сброса начинает работу генератор 21. Счетчик 24 на протяжении N тактов, (где N 2 - -1 - период М-последовательности, а m - количество элементов памяти генераторов псевдослучайной последовательности разрешает работу последнего,с входов которого на контролируемое устройство подаются тестовые последовательности. На выходах счетчика 7 пока нуль,и каждьш раз при получении нуля на выходах контролируемого устройства (г-вектор шины X равен нулю) в ответ на тестовые воздействия в реверсивный счетчик 3 прибавляется единица, получаемая как результат сравнения информации на выходах счетчика 7 и

5

0352

шины X, Элемент У задержки служит для обеспечения синхронной работы блока 2 сравнения и первого элемента И 4.

Когда счетчик 24 досчитывает до величины 2, генератор псевдослучайной последовательности прекращает работу, так как на выходах 1 - m счетчика 24 и соответственно на выходе

элемента И 27 нули, что запрещает работу ГПСП. Единичный сигнал на выходе (т + 1) счетчика 24 разрешает запись некомплектной информации, определяющей сколько раз г-вектор шины

X равняется нулю, из реверсивного счетчика 3 в блок 6 оперативной памяти по нулевому адресу, так как на выходах счетчика 7 пока нули.

А через время, определяемое эле0 ментом 25 задержки блока управления и достаточное для записи в блок 6 информации по адресу, соответствующему выходам 1 - г первого счетчика 7, в последний добавляется единица и приводятся в исходное состояние.реверсивный счетчик 3 и счетчик 24.

Со следующего такта генератора 21 опять разрешается работа ГПСП и блока 2 сравнения. Теперь в блок 6 уже

по первому адресу записывается значение реверсивного счетчика 3, которое определяет сколько раз г-вектор шины X равнялся единице.

Устройство работает в режиме под5 готовки данных до тех пор пока на (г + )-м выходе счетчика 7 не появляется единица, т.е. счетчик 7 просчитывается до величины 2 . Сбрасывается триггер 18 и элемент 8 индика0 ции сигнализирует об окончании режима подготовки данных.

Для работы в режиме контроля переключателя 15 и 17 устанавливаются в нижнее положение, а переключатель

5 16 - в верхяее, и нажимается кнопка Пуск.

/Работа устройства в режиме контре- ля происходит аналогично работе в режиме подготовки данных, исключение состоит в следующем. По импульсу сброса, переводящему счетчики 7 и 21 в исходное состояние, происходит чтение по нулевому адресу, так как на выходах счетчика 7 пока нули, из блока 6 в реверсивный счетчик 3 по синхросигналу ранее подготовленной информации, определяющей сколько раз г-вектор шины X должен быть равен н 31319035

лю при подаче тестовых воздействий с ГПСП на контролируемое устройство. При очередном появлении нуля на выходах контролируемого устройства (тогсч

ди и со

да г-вектор шины X равен нулю) из ре- ных входов устройства и первому вховерсивного счетчика 3 вычитается единица, получаемая как результат сравнения информации на выходах 1 - г первого счетчика 7 и на шине X, Если

ду первого элемента И, группа разрядных выходов реверсивного счетчика подключена к группе информационных входов блока индикации, вход пуска

количество раз получения нуля на вы- 0 блока управления является входом пусходах контролируемого устройства совпадает с эталонным значением, то к моменту, когда на выходе (т + 1) счетчика 24 будет единица, на выходах реверсивного счетчика 3 будут ну- -5 мяти, три элемента ИЛИ второй элели, что и определяет нулевое значение выхода второго элемента И 14.

Единичный сигнал с выхода (т 1) счетчика 24 через время, определяемое элементом 25 задержки, после оче-20 разрядность входного кода) подключе- редной серии из N тактов добавляет на к группе адресных входов блока единицу в счетчик 7, а еще через времент И, элемент НЕ, элемент задержки элемент индикации и три сдвоенных переключателя, причем группа выходов счетчика с первого по г-й (где г оперативной памяти и второй группе входов блока сравнения, выход (г -- + 1)-го разряда счетчика соединен с входом элемента индикации и первым входом первого элемента ИЛИ, второй вход которого объединен с входом разрешения блока индикации и подключен к выходу второго элемента И, первый и второй входы которого соединены соответственно с выходами второго элемента ИЛИ и элемента НЕ, группа разрядных выходов реверсивного счетчика подключена к группе входов вто- 35 рого элемента ИЛИ и группе информационных входов блока оперативной памяти, группа информационных выходов которого подключена к группе информационных входов реверсивного счетчика, суммирующий, вычитающий, синхро- вход и вход сброса которого соединены соответственно с первым и вторым подвижными контактами первого сдвоенного переключателя, первым и вторым подвижными контактами второго сдвоенного переключателя, первый контакт первой пары и второй контакт второй пары контактов первого сдвоенного пе- реключателя объединены и подключены

мя, определяемое элементом 26 задержки, необходимое для анализа выходов реверсивного счетчика 3, разрешает чтение ранее подготовленной информа - ции в реверсивный счетчик 3 из блока 6 по следующему адресу, определяемому значением выходов 1 - г счетчика 7,

Контролируемая схема исправна, если происходит сравнение эталонной информации,,записанной по всем адресам блока 6 оперативной памяти с информацией, получаемой каждый раз в течение одного прогона текбта на выходах контролируемого устройства, т.е. на шине X, и срабатывает элемент 8 индикации, сигнализирующий об окончании контроля.

Если информация по какому-либо адресу блока 6 не сравнивается с ин- фopмaциeйj получаемой на шине X, т.е. в момент, когда на выходе (т + + 1) счетчика 24 единица, на выходах реверсивного счетчика 3 не нуль, то единичный сигнал с выхода элемента И 14 разрешает индикацию блоком 5 индикации информации, полученной на выходах реверсивного счетчика 3,и сбра- -сывает в нуль триггер 1,т.е.дальнейший контроль прекращается.

Формула изобретения

Устройство для контроля логических блоков, содержащее блок сравнения, блок управления, реверсивный

счетчик, первый элемент И и блок индикации, причем первая группа входов и выход блока сравнения подключены соответственно к группе информационных входов устройства и первому входу первого элемента И, группа разрядных выходов реверсивного счетчика подключена к группе информационных входов блока индикации, вход пуска

блока управления является входом пуска устройства, отличающее- с я тем, что, с целью повьшения достоверности контроля, в устройство введены счетчик, блок оперативной паразрядность входного кода) подключе- на к группе адресных входов блока

мент И, элемент НЕ, элемент задержки, элемент индикации и три сдвоенных переключателя, причем группа выходов счетчика с первого по г-й (где г 0 разрядность входного кода) подключе- на к группе адресных входов блока

5

0

5

оперативной памяти и второй группе входов блока сравнения, выход (г -- + 1)-го разряда счетчика соединен с входом элемента индикации и первым входом первого элемента ИЛИ, второй вход которого объединен с входом разрешения блока индикации и подключен к выходу второго элемента И, первый и второй входы которого соединены соответственно с выходами второго элемента ИЛИ и элемента НЕ, группа разрядных выходов реверсивного счетчика подключена к группе входов вто- 5 рого элемента ИЛИ и группе информационных входов блока оперативной памяти, группа информационных выходов которого подключена к группе информационных входов реверсивного счетчика, суммирующий, вычитающий, синхро- вход и вход сброса которого соединены соответственно с первым и вторым подвижными контактами первого сдвоенного переключателя, первым и вторым подвижными контактами второго сдвоенного переключателя, первый контакт первой пары и второй контакт второй пары контактов первого сдвоенного пе- реключателя объединены и подключены

к выходу первого элемента И, второй контакт первой пары и первый контакт второй пары контактов первого сдвоен

ного переключателя объединены и подключены к шине нулевого потенциала устройства, первый контакт первой пары контактов второго сдвоенного переключателя и второй контакт второй пары контактов третьего сдвоенного пе0

5

51319035

реключателя объединены и подключены к выходу третьего элемента ИЛИ, второй контакт первой пары и первый контакт второй пары контактов второго сдвоенного переключателя объединены 5 и подключены к шине нулевого потенциала устройства, первый выход блока управления через элемент задержки соединен с вторым входом первого элемента И и является выходом разреше- О НИН формирования тестовой последовательности устройства, первый вход третьего элемента ИЛИ объединен с входом сброса счетчика и подключен к

такт которого соединен с входом чтения блока оперативной памяти, блок управления содержит триггер, одновиб- ратор, два элемента И, два элемента ИЛИ, два элемента задержки, счетчик и генератор тактовых импульсов, причем прямой выход триггера соединен с входом одновибратора и nepaiiM входом первого элемента И, второй вход и выход которого подключены соответственно к инверсному выходу одновибратора и входу генератора тактовых импульсов, выход которого соединен со счетным входом счетчика и первым входом

мента И соединен с выходом второго элемента ИЛИ,, входы которого соединевторому выходу блока управления, тре- 15 второго элемента И, вход сброса счет- тий выход которого соединен с вторым чика соединен с выходом первого эле- входрм третьего элемента ИЛИ, первый мента ИЛИ, второй вход второго эле- контакт первой пары контактов третьего сдвоенного переключателя и второй контакт второй пары контактов второ- 20 ны с соответствующими выходами разря- го сдвоенного переключателя подключе- доз счетчика с первого по т-й, (т + ны соответственно к четвертому и пятому выходам блока управления, первый вход которого объединен со счет25

ным входом счетчика и подключен к шестому выходу блока управления, третий вход второго элемента И соединен с четвертым выходом блока управления, второй вход которого соединен с выхо+ 1)-й разрядный выход которого через первый и второй элементы задержки подключен к третьему выходу блока управления, прямой выход одновибратора соединен с первым входом первого элемента ИЛИ и является вторым выходом блока управления, выход второго элемента И, выход (га + 1)-го разрядом первого элемента ИЛИ, второй кон- 30 да счетчика, выход первого элемента такт первой пары и первый контакт второй пары контактов третьего сДво- енного переключателя объединены и подключены к шине нулевого потенциаИЛИ, выход первого элемента задержки являются соответственно первым, четвертым, пятым и шестым выходами блока управления, второй вход первого

ла устройства, вход элемента НЕ сое- 35 элемента ИЛИ и нулевой вход триггера динен с входом записи блока оператив- являются соответственно первым и вторым входами блока управления, единичный вход триггера является входом пуска блока управления.

ной памяти и подключен к первому подвижному контакту третьего сдвоенного переключателя, второй подвижный контакт которого соединен с входом чтения блока оперативной памяти, блок управления содержит триггер, одновиб- ратор, два элемента И, два элемента ИЛИ, два элемента задержки, счетчик и генератор тактовых импульсов, причем прямой выход триггера соединен с входом одновибратора и nepaiiM входом первого элемента И, второй вход и выход которого подключены соответственно к инверсному выходу одновибратора и входу генератора тактовых импульсов, выход которого соединен со счетным входом счетчика и первым входом

мента И соединен с выходом второго элемента ИЛИ,, входы которого соединевторого элемента И, вход сброса счет- чика соединен с выходом первого эле- мента ИЛИ, второй вход второго эле- ны с соответствующими выходами разря- доз счетчика с первого по т-й, (т +

второго элемента И, вход сброса счет- чика соединен с выходом первого эле- мента ИЛИ, второй вход второго эле- ны с соответствующими выходами разря- доз счетчика с первого по т-й, (т +

+ 1)-й разрядный выход которого через первый и второй элементы задержки подключен к третьему выходу блока управления, прямой выход одновибратора соединен с первым входом первого элемента ИЛИ и является вторым выходом блока управления, выход второго элемента И, выход (га + 1)-го разряда счетчика, выход первого элемента

ИЛИ, выход первого элемента задержки являются соответственно первым, четвертым, пятым и шестым выходами блока управления, второй вход первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1987 |

|

SU1483456A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Анализатор законов распределения | 1979 |

|

SU960845A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| АДАПТИВНЫЙ ЭЛЕКТРОСТИМУЛЯТОР | 1998 |

|

RU2155614C2 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1283772A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК С ПАМЯТЬЮ | 2006 |

|

RU2321166C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для поиска неисправностей в блоках ЦВМ. Цель изобретения - повышение достоверности контроля достигается тем, что в, устройство, содержащее блок 1 управления, блок 2 сравнения, реверсивный счетчик 3, первый элемент И 4, блок 5 индикации, введены блок 6 оперативной памяти, первый, второй и третий сдвоенные переключатели 15 - 17, счетчик 7, элемент 8 индикации, элемент 9 задержки, первый, второй и третий элементы ИЛИ 10 - 12, элемент НЕ 13, второй элемент И .14. Контролируются все векторы состояния на выходах контролируемого устройства. I ил. 00 ю 00 ел

| Устройство для контроля логических блоков | 1976 |

|

SU643877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Баран Е.Д | |||

| О достоверности контроля двоичных последовательностей методом счета состояний | |||

| - Автоматика и вычислительная техника, 1982, № 6, с | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-10—Подача