Изобретение относится к области вы числительной техники, в частности к аппаратуре контроля логических вычислительных машин.

Известно устройство для контроля логнческих блоков, основанное на методе сравнения выходных снгналов контролируемого и Эталонного логическ1|х блоков, входные сигналы которых формируются с помощью счетчикя l .

Недостатком этого устройства является ограниченная область прнменения Оно используется для контроля сравнительно простых узлов, имеюшнх небольшое количество входов.

Известно также устройство для контроля логических блоков, в котором для формирования входных сигналов контролируемого и эталонного блоке используется генератор псевдослучайных кодов Грея, что позволяет контролировать логические блоки с любым количеством входов 2 .

Недостатком обоих известных устройств является то, что для проверки логического блока каждого типа необходнм однотипный эталонный блок.

Наиболее близким по техническому решению к данному изобретенню является устройство для контроля логических блоков, содержащее блок управления, генератор псевдослучайных кодов и накапливающий сумматор, причем выходыблока управления соединены с управляющими входами генератора псевдослучайных кодов и накапливающего сумматора, первая группа выходов генератора псевдослучайных кодов соединена со входами контролируемого логического блока .

Недостатком этого устройства является сложность и недостаточное быстродействие вследствне большого количест- ва выходов контролируемого узла.

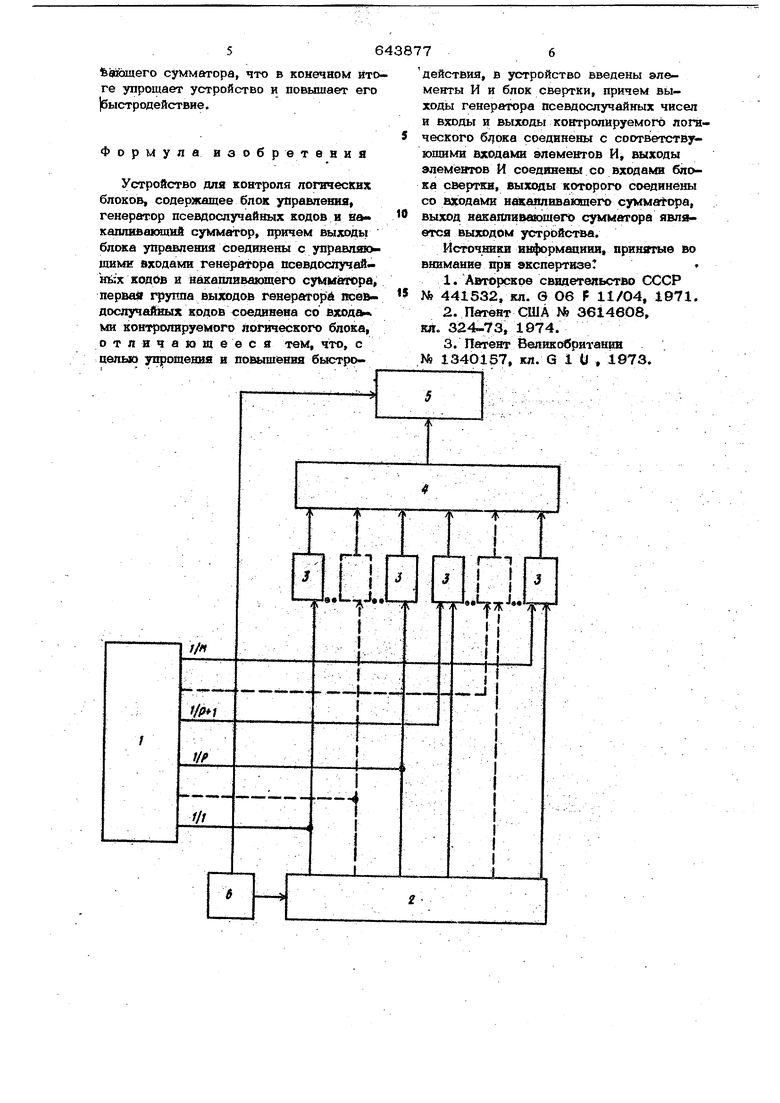

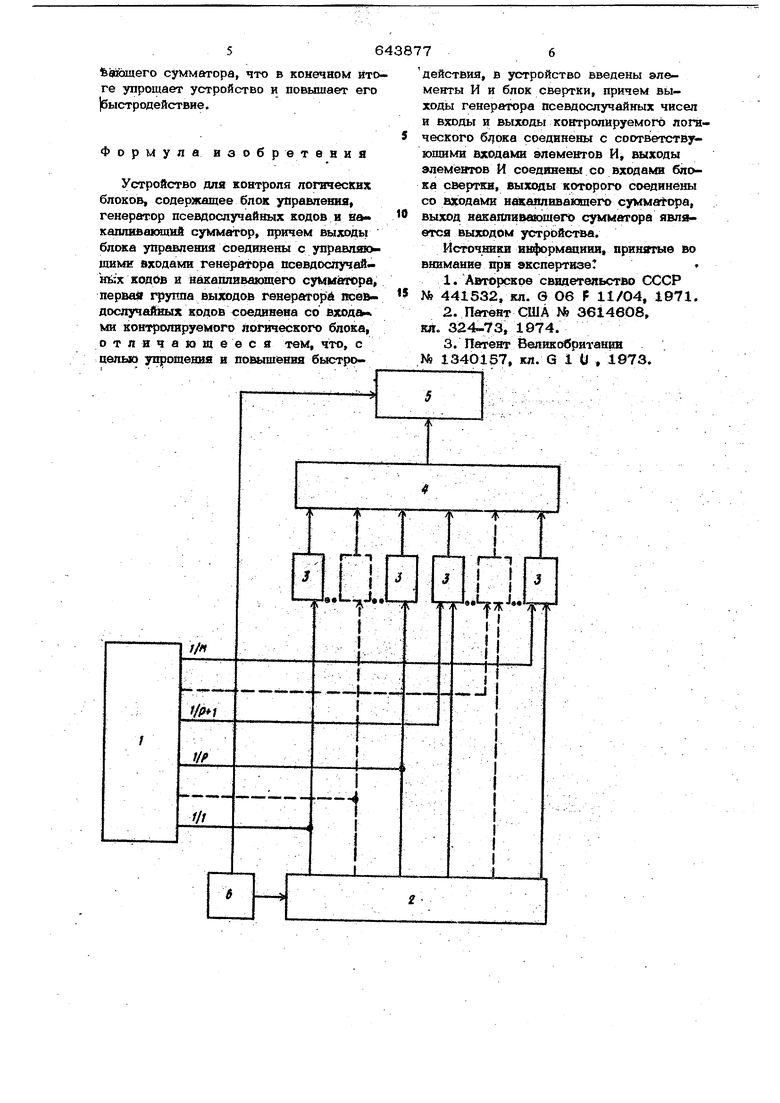

Целью изобретения является упрощение устройства в повышение етч быстродействия. Поставленная цель достигается тем, что Б устройство введены элементы И и блок свертки, причем выходы генератора псевдосЯучайн ых чисел и входы и выходы контролируемого логического бл к а соединены с соответствующими вхо- , дами элементов И, выходы элементов И соединены со входами блока свертки выходы которотч) соединены со входами накапливающего сумматора, выход накаплйвакйаего сумматора является выходом устройства. Блок-схема устройства для контроля логических блоков приведена на чертеже, ... -.. .-. . . . . - . . .. .. ..... . . Выводы контролируемого логического блока 1 обознвчены 1/1,.,. 1/М. Первые р иа этих М выводов являются вхо дами, ос гапыЕые (М-р) выходами. Поскольку любой иэ этих выводов может слу- жить как входом, так в выходсйл логического блока 1, для возможности введения псевдослучайных кодов на любой вывод логического блока 1 генератор псевдр случайных кодов 2 тшсже имеет М разУрядов. Все р входов контролируемого йогйческого блока Д обединёнь с cooiw ьететвуюишми выходвмн генератора 2. Kpov vtfFO, выходы генератора 2 соединены со йсодами элементов И 3. Коявчёс во длемевтов И 3 также равно М т.е. коляпестеу выводов контролируемого логического блсжа. Входы элементов И 3 сЬеяиневы с 1м 1шдамв коатролйруемого логического бп«жа 1. Выходы элемент ИЗ соёдгне сы со входамн блока съвугекя 4; выходы которого поя«якпеюл ко входам нвка йливаюпхего сумматора S. Бяок улрввленвя G соединен с управлякшшш входами генератора 2 и сумматора 5, Устройство работает следующим образЬм. Псевдослучайные коды с выходов гевератора 2 подаются на входы контрсишруемого логического блока 1 и на в13Ебды Элементов И 3. Параллельные коды с выходов логического блока 1, явяякшшеся результатом воздействия на его юсоды псевдослучайных кодов, поступают на входы элементов И. Параллельные коды с выходов элеменгов И, воздействуя на соответствующие входы блока свер-гки 4, Bi ifeaKyr появление на выходах блока 4 паралnenibHbix кодов. Эти коды поступают на входы сумматора 5, в котором прбис ходит сложение их с накопленной суммой и хранение этой суммы. Для достижения повторяемости реультатов проверки генератор 2 перед ачаутом цикла проверки устанавливается в определенное исходное состояие, например в такое, когда на всех го выходах присутствуют логические единицы. Количество параллельных кодов вырабатываемых генератором 2 за время проверки должно быть строго фиксирова ным. Более того, есликонтролируемьй огический блок содержит триггерные узлы, то эти узлы Б начале цикла проверки также должны быть установлены в определенное исходное состояние. С этой 11елью никл проверки блока 1 разбит на дба этапа, последовательность выполнения которых следующая. После того как генератор 2 установлен в исходное cocToaime, блок управления 6 вырабаывает разрешающий сигнал, и йа выходах генератора 2 поа1аляются параллельные коды, частота смены которых определяется в основном быстродействием сумматора 5. Наличие сменяющизвся кодов на взсодах контролируемого логического блока 1 вызывает функционвровште этого блока и возникновение смены кодов на Входахнакапливающего сумматора 5. Однако в течение определенного Количества первых тактов работы генератОра 2, которые составляют первый этап цикла проверки, работа сумматора 5 блокирована сигналом блока управления 6 и суммаровацие не производится В течеийе Этого времени проис цздйт yctuHOiaaKa в исходное состояние триггеров в контротшруемом блоке 1. Поскопысу блок 1 мсжет быть сложным, Еолич ;тво тактов работы генератора 2 для установки в исхоДйое срстойнйв всех триггеров блока 1 дслжйо быть достаточно большим.. Во время второго этапа шш1а проверки генератор 2 продолжает работать, а блйккровка сумматора 5 снамаетсв. Песле окюачания шоша проверки блок управления 6 блокирует своими сигналами работу генератора 2 и сумматора 5. Накопленная за время прове{жй в сумматоре 5 контрольная сумма сравнивается с суммой, полученной в результате авдлогнчной проверки исправного однотипного блока. Конргролируемый логический блок 1 считается исправным, если указанные суммы совпадают., Использование в устройстве блока свертки позволяет в несколько раз сократить количество разрядов вакаплв-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1372324A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1037257A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Устройство для функционального контроля цифровых логических элементов | 1981 |

|

SU1096652A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля цифровых блоков | 1978 |

|

SU706849A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

Авторы

Даты

1979-01-25—Публикация

1976-07-12—Подача