15

Изобретение относится к радиовещательной технике и технике связи, может быть использовано в устройствах цифровой обработки звуковых сигналов и предназначено для сжатия или расширения динамического диапазона звуковых сигналов.

Цель изобретения - уменьшение нелинейных искажений за счет улучшения соотношения сигнал/шум в выходном сигнале при одновременном упрош,ении устройства.

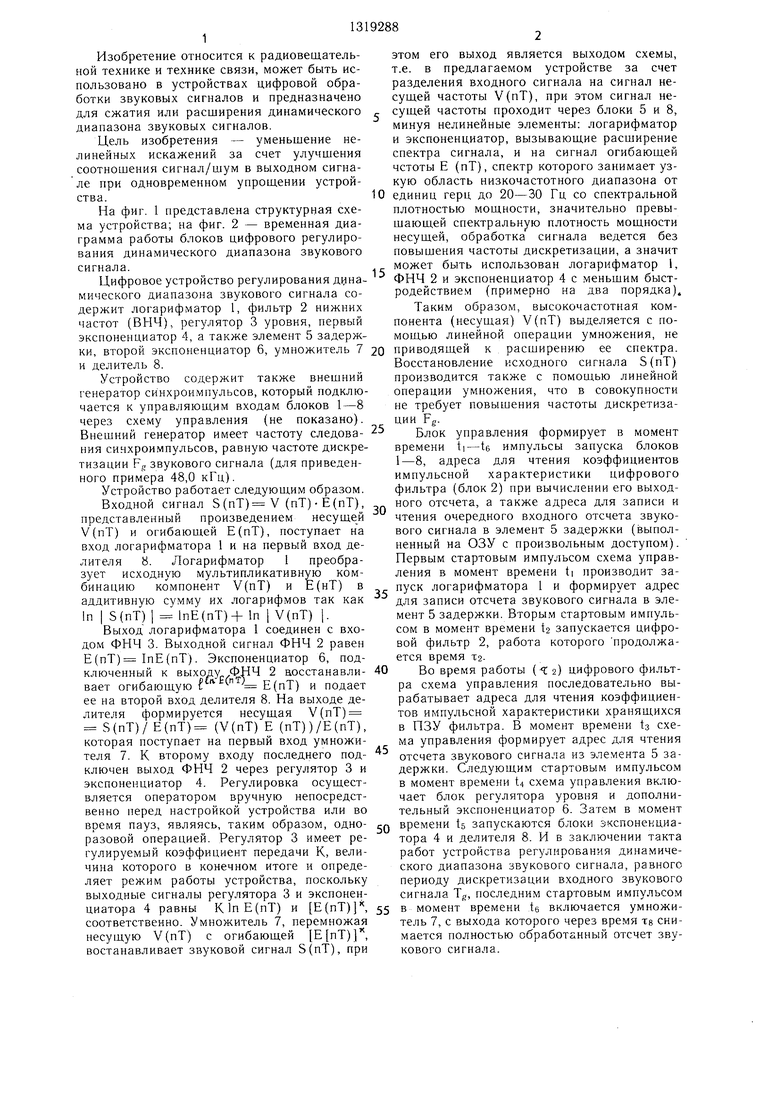

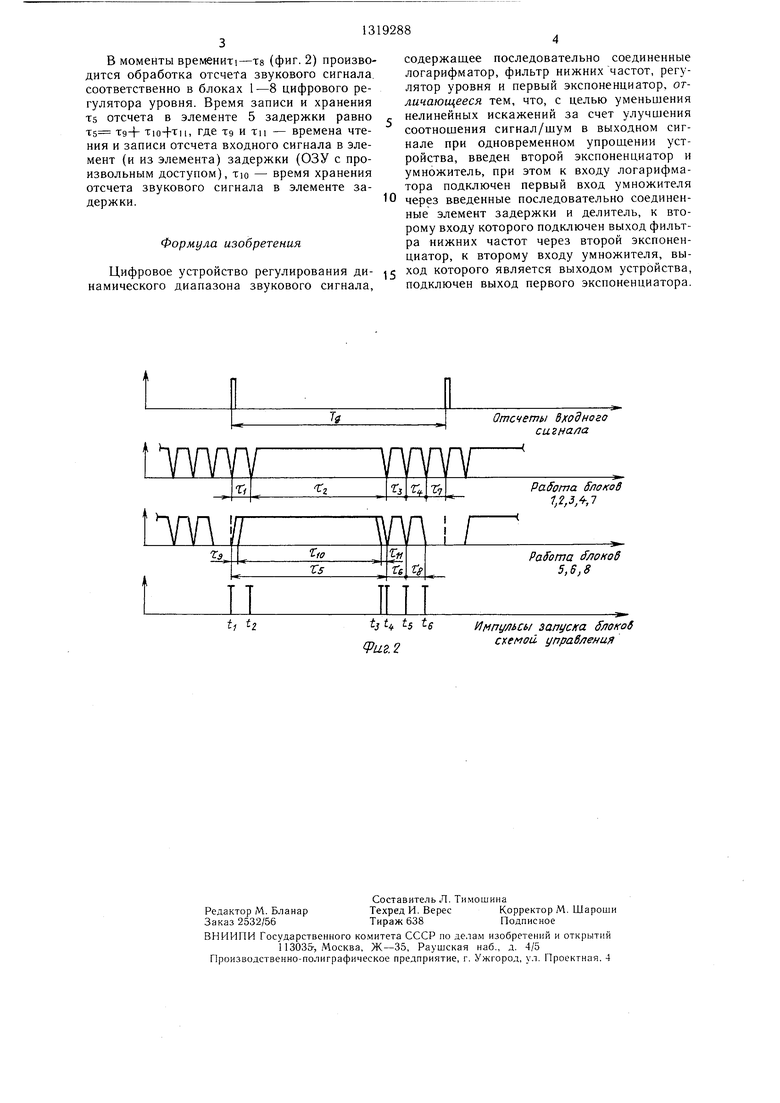

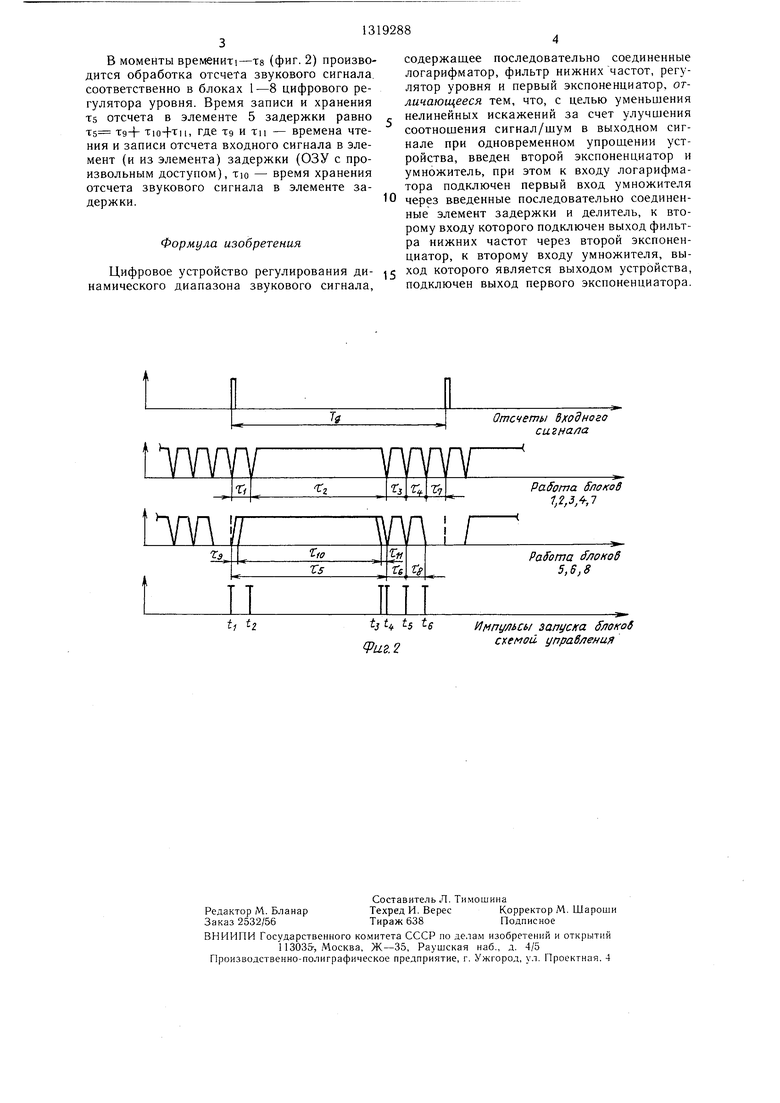

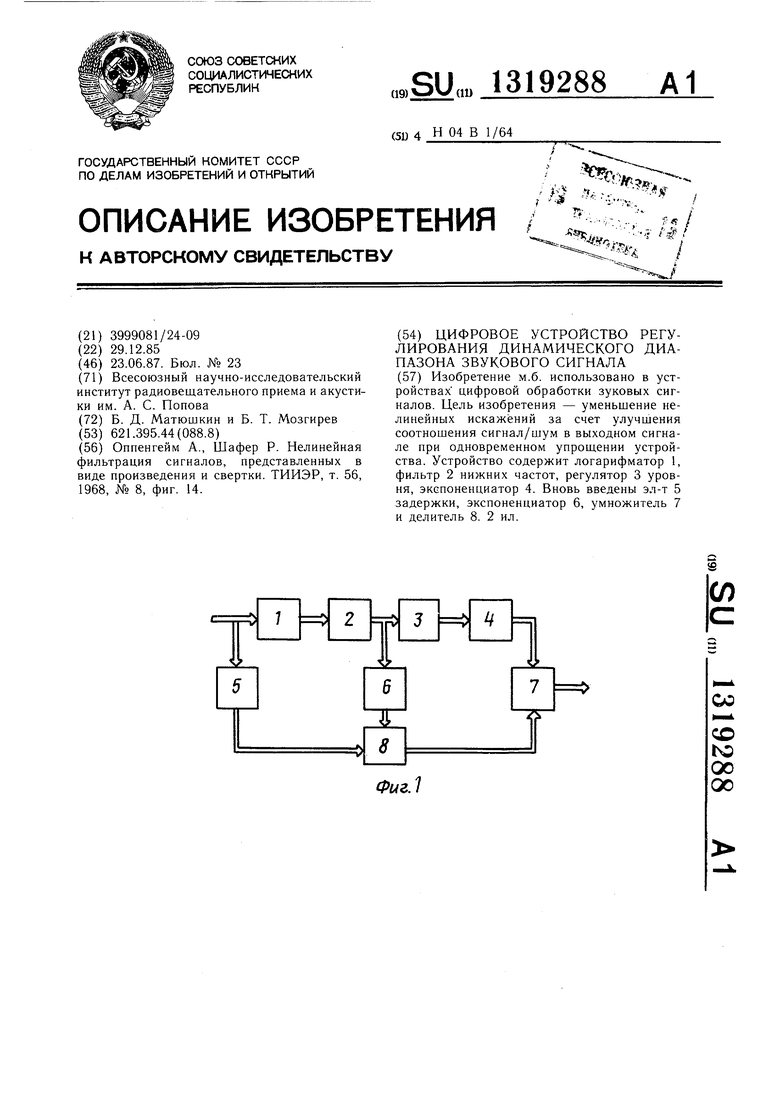

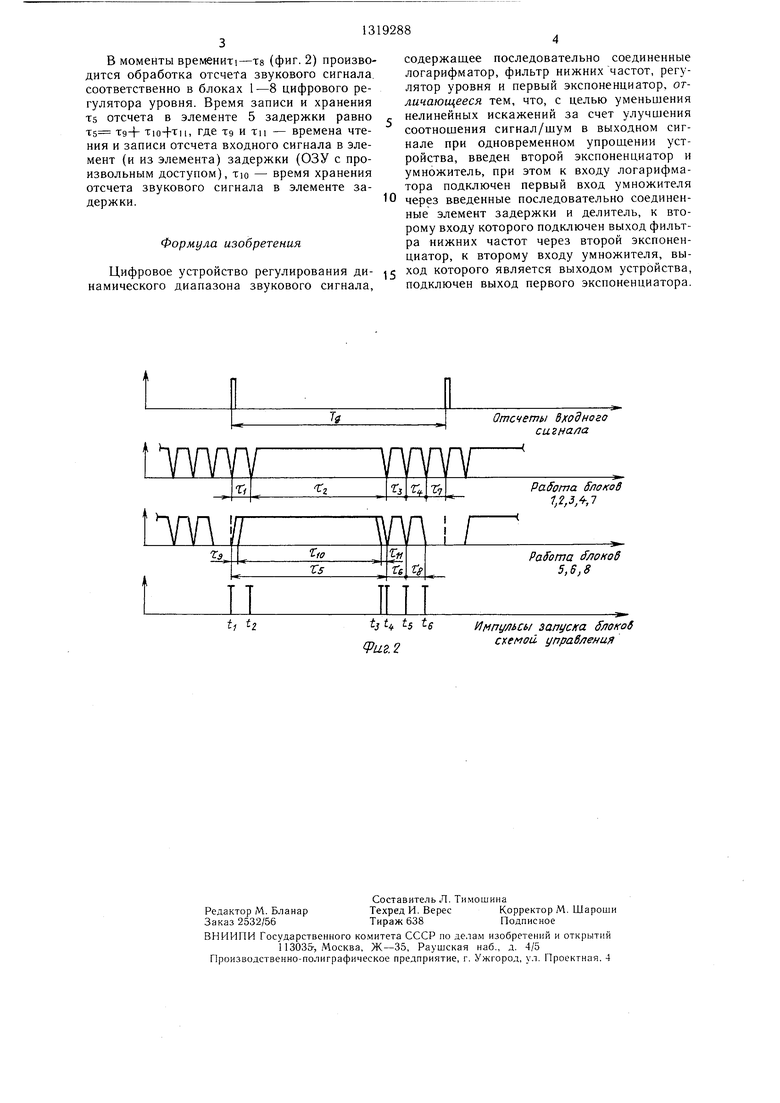

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма работы блоков цифрового регулирования динамического диапазона звукового сигнала.

Цифровое устройство регулирования динамического диапазона звукового сигнала содержит логарифматор 1, фильтр 2 нижних частот (ВНЧ), регулятор 3 уровня, первый экспоненциатор 4, а также элемент 5 задержки, второй экспоненциатор 6, умножитель 7 20 приводящей и делитель 8.

Устройство содержит также внешний генератор синхроимпульсов, который подключается к управляющим входам блоков 1-8 через схему управления (не показано). Внешний генератор имеет частоту следова- 25 ния синхроимпульсов, равную частоте дискретизации Fgзвукового сигнала (для приведенного примера 48,0 кГц).

Устройство работает следуюП1,им образом.

Входной сигнал S (пТ) V (пТ) Е(пТ), представленный произведением несущей V(nT) и огибающей Е(пТ), поступает на вход логарифматора 1 и на первый вход делителя 8. Логарифматор 1 преобразует исходную мультипликативную комбинацию компонент V(nT) и Е(нТ) в аддитивную сумму их логарифмов так как In I S(nT) 1 1пЕ(пТ)+ In 1 V(nT) j.

Выход логарифматора 1 соединен с входом ФНЧ 3. Выходной сигнал ФНЧ 2 равен Е(пТ) InE(nT). Экспоненциатор 6, подключенный к выходу ФНЧ 2 аосстанавлиэтом его выход является выходом схемы, т.е. в предлагаемом устройстве за счет разделения входного сигнала на сигнал несущей частоты V(nT), при этом сигнал не сущей частоты проходит через блоки 5 и 8, минуя нелинейные элементы: логарифматор и экспоненциатор, вызывающие расширение спектра сигнала, и на сигнал огибающей чстоты Е (пТ), спектр которого занимает узкую область низкочастотного диапазона от

10 единиц герц до 20-30 Гц со спектральной плотностью мощности, значительно превышающей спектральную плотность мощности несущей, обработка сигнала ведется без повышения частоты дискретизации, а значит может быть использован логарифматор 1, ФНЧ 2 и экспоненциатор 4 с меньшим быстродействием (примерно на два порядка).

Таким образом, высокочастотная компонента (несущая) V(nT) выделяется с помощью линейной операции умножения, не к расширению ее спектра. Восстановление исходного сигнала S(nT) производится также с помощью линейной операции умножения, что в совокупности не требует повыщения частоты дискретизации Fg.

30

вает огибающую f (. Е(пТ) и подает ее на второй вход делителя 8. На выходе делителя формируется несущая V(nT) S(nT)/ Е(пТ) (V(nT) Е (пТ))/Е(пТ), которая поступает на первый вход умножителя 7. К второму входу последнего подключен выход ФНЧ 2 через регулятор 3 и экспоненциатор 4. Регулировка осуществляется оператором вручную непосредственно перед настройкой устройства или во

Блок управления формирует в момент времени ti-te импульсы запуска блоков 1-8, адреса для чтения коэффициентов импульсной характеристики цифрового фильтра (блок 2) при вычислении его выходного отсчета, а также адреса для записи и чтения очередного входного отсчета звукового сигнала в элемент 5 задержки (выполненный на ОЗУ с произвольным доступом). Цервым стартовым импульсом схема управления в момент времени ti производит за- -. пуск логарифматора 1 и формирует адрес для записи отсчета звукового сигнала в элемент 5 задержки. Вторым стартовым импульсом в момент времени запускается цифровой фильтр 2, работа которого продолжается время Т2.

Во время работы ( 2) цифрового фильтра схема управления последовательно вырабатывает адреса для чтения коэффициентов импульсной характеристики хранящихся в ПЗУ фильтра. В момент времени ts схема управления формирует адрес для чтения отсчета звукового сигнала из элемента 5 задержки. Следующим стартовым импульсом в момент времени t4 схема управления включает блок регулятора уровня и дополнительный экспоненциатор 6. Затем в момент

40

45

время пауз, являясь, таким образом, одно- сп времени ts запускаются блоки экспоненциаразовой операцией. Регулятор 3 имеет регулируемый коэффициент передачи К, величина которого в конечном итоге и определяет режим работы устройства, поскольку выходные сигналы регулятора 3 и экснонен- циатора 4 равны К1пЕ(пТ) и Е(пТ)| соответственно. Умножитель 7, перемножая несущую V(nT) с огибающей ) , востанавливает звуковой сигнал 5(пТ), при

55

тора 4 и делителя 8. И в заключении такта работ устройства регулирования динамического диапазона звукового сигнала, равного периоду дискретизации входного звукового сигнала Tg, последним стартовым импульсом в момент времени ta включается умножитель 7, с выхода которого через время те снимается полностью обработанный отсчет звукового сигнала.

5

0 приводящей

5

этом его выход является выходом схемы, т.е. в предлагаемом устройстве за счет разделения входного сигнала на сигнал несущей частоты V(nT), при этом сигнал несущей частоты проходит через блоки 5 и 8, минуя нелинейные элементы: логарифматор и экспоненциатор, вызывающие расширение спектра сигнала, и на сигнал огибающей чстоты Е (пТ), спектр которого занимает узкую область низкочастотного диапазона от

0 единиц герц до 20-30 Гц со спектральной плотностью мощности, значительно превышающей спектральную плотность мощности несущей, обработка сигнала ведется без повышения частоты дискретизации, а значит может быть использован логарифматор 1, ФНЧ 2 и экспоненциатор 4 с меньшим быстродействием (примерно на два порядка).

Таким образом, высокочастотная компонента (несущая) V(nT) выделяется с помощью линейной операции умножения, не к расширению ее спектра. Восстановление исходного сигнала S(nT) производится также с помощью линейной операции умножения, что в совокупности не требует повыщения частоты дискретизации Fg.

0

Блок управления формирует в момент времени ti-te импульсы запуска блоков 1-8, адреса для чтения коэффициентов импульсной характеристики цифрового фильтра (блок 2) при вычислении его выходного отсчета, а также адреса для записи и чтения очередного входного отсчета звукового сигнала в элемент 5 задержки (выполненный на ОЗУ с произвольным доступом). Цервым стартовым импульсом схема управления в момент времени ti производит за- пуск логарифматора 1 и формирует адрес для записи отсчета звукового сигнала в элемент 5 задержки. Вторым стартовым импульсом в момент времени запускается цифровой фильтр 2, работа которого продолжается время Т2.

Во время работы ( 2) цифрового фильтра схема управления последовательно вырабатывает адреса для чтения коэффициентов импульсной характеристики хранящихся в ПЗУ фильтра. В момент времени ts схема управления формирует адрес для чтения отсчета звукового сигнала из элемента 5 задержки. Следующим стартовым импульсом в момент времени t4 схема управления включает блок регулятора уровня и дополнительный экспоненциатор 6. Затем в момент

0

5

5

тора 4 и делителя 8. И в заключении такта работ устройства регулирования динамического диапазона звукового сигнала, равного периоду дискретизации входного звукового сигнала Tg, последним стартовым импульсом в момент времени ta включается умножитель 7, с выхода которого через время те снимается полностью обработанный отсчет звукового сигнала.

В моменты временит -те (фиг. 2) производится обработка отсчета звукового сигнала, соответственно в блоках 1-8 цифрового регулятора уровня. Время записи и хранения Т5 отсчета в элементе 5 задержки равно Т5 т9-|- Tio-fTu, где Т9 и тп - времена чтения и записи отсчета входного сигнала в элемент (и из элемента) задержки (ОЗУ с произвольным доступом), тю - время хранения отсчета звукового сигнала в элементе задержки.

Формула изобретения

содержащее последовательно соединенные логарифматор, фильтр нижних частот, регулятор уровня и первый экспоненциатор, от- личающееся тем, что, с целью уменьшения нелинейных искажений за счет улучшения соотношения сигнал/шум в выходном сигнале при одновременном упрощении устройства, введен второй экспоненциатор и умножитель, при этом к входу логарифма- тора подключен первый вход умножителя 10 через введенные последовательно соединенные элемент задержки и делитель, к второму входу которого подключен выход фильтра нижних частот через второй экспоненциатор, к второму входу умножителя, вы- Цифровое устройство регулирования ди- ход которого является выходом устройства, намического диапазона звукового сигнала, подключен выход первого экспоненциатора.

содержащее последовательно соединенные логарифматор, фильтр нижних частот, регулятор уровня и первый экспоненциатор, от- личающееся тем, что, с целью уменьшения нелинейных искажений за счет улучшения соотношения сигнал/шум в выходном сигнале при одновременном упрощении устройства, введен второй экспоненциатор и умножитель, при этом к входу логарифма- тора подключен первый вход умножителя через введенные последовательно соединенные элемент задержки и делитель, к второму входу которого подключен выход фильтра нижних частот через второй экспонен

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство регулирования динамического диапазона звукового сигнала | 1987 |

|

SU1480133A2 |

| Нерекурсивный цифровой фильтрдециматор | 1984 |

|

SU1195420A2 |

| Нерекурсивный цифровой фильтр-дециматор | 1982 |

|

SU1109890A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Нерекурсивный цифровой фильтр нижних частот | 1986 |

|

SU1418750A1 |

| ЦИФРОВОЙ АДАПТИВНЫЙ ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2039416C1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Устройство цифровой пространственно-временной фильтрации телевизионного сигнала изображения | 1989 |

|

SU1646074A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1989 |

|

SU1698953A2 |

| Нерекурсивный цифровой фильтр-дециматор | 1986 |

|

SU1354394A1 |

Изобретение м.б. использовано в устройствах цифровой обработки зуковых сигналов. Цель изобретения - уменьшение нелинейных искажений за счет улучшения соотношения сигнал/шум в выходном сигнале при одновременном упрощении устройства. Устройство содержит логарифматор 1, фильтр 2 нижних частот, регулятор 3 уровня, экспоненциатор 4. Вновь введены эл-т 5 задержки, экспоненциатор 6, умножитель 7 и делитель 8. 2 ил. § (Л Фиг.1 со ;о ГчО 00 00

i/ i2

tjU 5 6 us.2

Импульсь/ запуска локоб . управлений

| Оппенгейм А., Шафер Р | |||

| Нелинейная фильтрация сигналов, представленных в виде произведения и свертки | |||

| ТИИЭР, т | |||

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1987-06-23—Публикация

1985-12-29—Подача