Изобретение относится к электросвязи и может быть использовано для прогнозирования качества канала связи в процессе его текущего контроля.

Цель изобретения - сокращение времени.

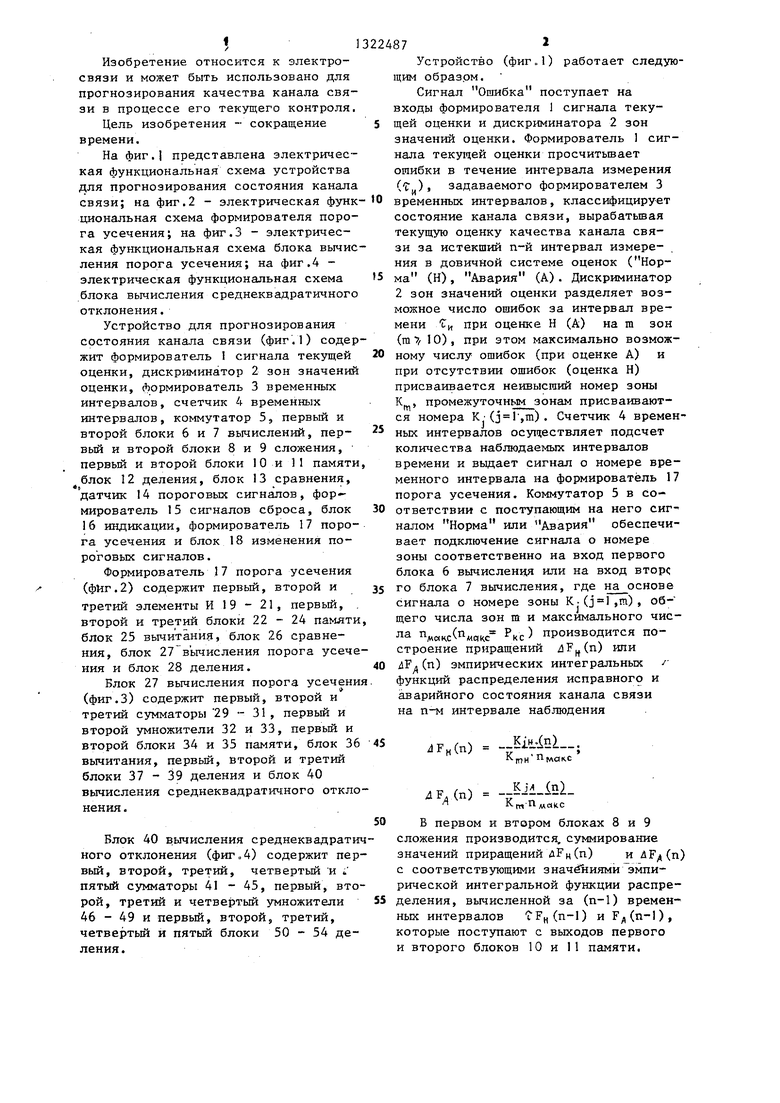

На фиг.1 представлена электрическая функциональная схема устройства для прогнозирования состояния канала

связи; на фиг.2 - электрическая функ- Овременных интервалов, классифицирует

циональная схема формирователя поро-состояние канала связи, вырабатьшая

га усечения; на фиг.З - электричес-текущую оценку качества канала свякая функциональная схема блока вычис-зи за истекший п-й интервал измереления порога усечения; на фиг.4 -ния в довичной системе оценок (Нор 5ма (Н), Авария (А). Дискриминатор

электрическая функциональная схема блока вычисления среднеквадратичного отклонения,

Устройство для прогнозирования состояния канала связи (фиг.1) содержит формирователь 1 сигнала текущей 20 ному числу ошибок (при оценке А) и оценки, дискриминатор 2 зон значений при отсутствии ошибок (оценка Н)

2 зон значений оценки разделяет возможное число ошибок за интервал времени Ти при оценке Н (А) на га зон (т 10), при этом максимально возмож

оценки, формирователь 3 временных интервалов, счетчик 4 временных интервалов, коммутатор 5, первый и второй блоки 6 и 7 вычислений, первый и второй блоки 8 и 9 сложения, первый и второй блоки 10 и 11 памяти блок 12 деления, блок 13 сравнения, датчик 14 пороговых сигналов, формирователь 15 сигналов сброса, блок 16 индикации, формирователь 17 порога усечения и блок 18 изменения пороговых сигналов.

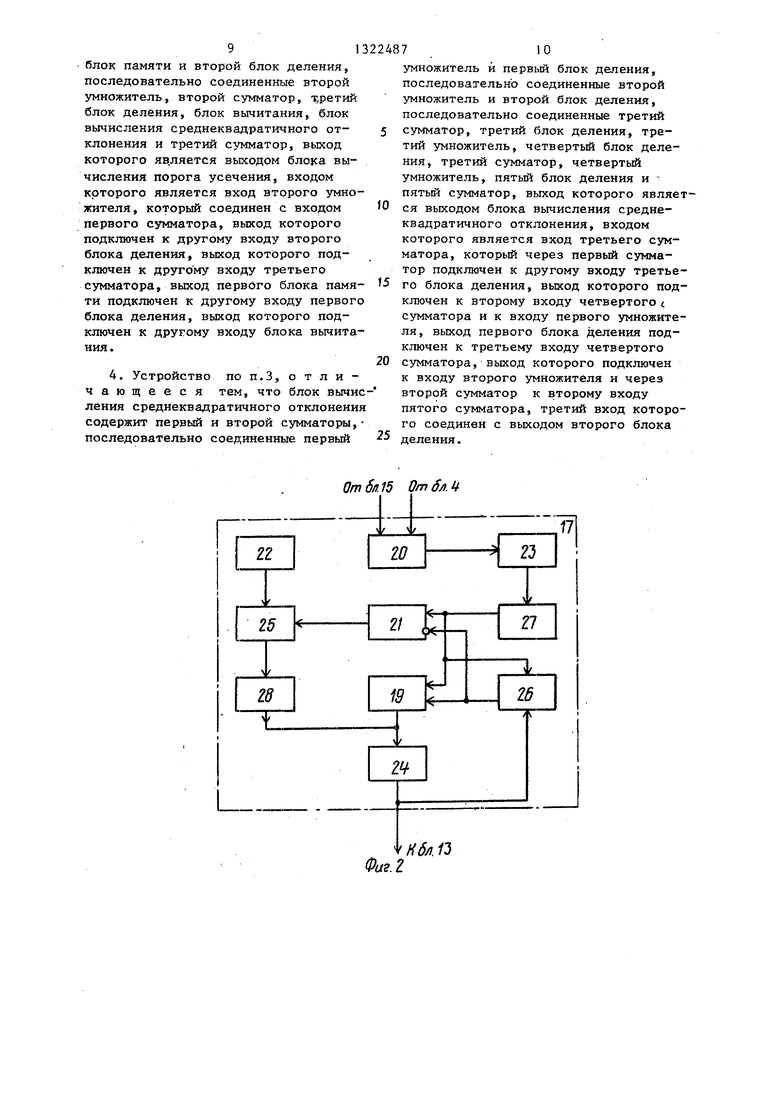

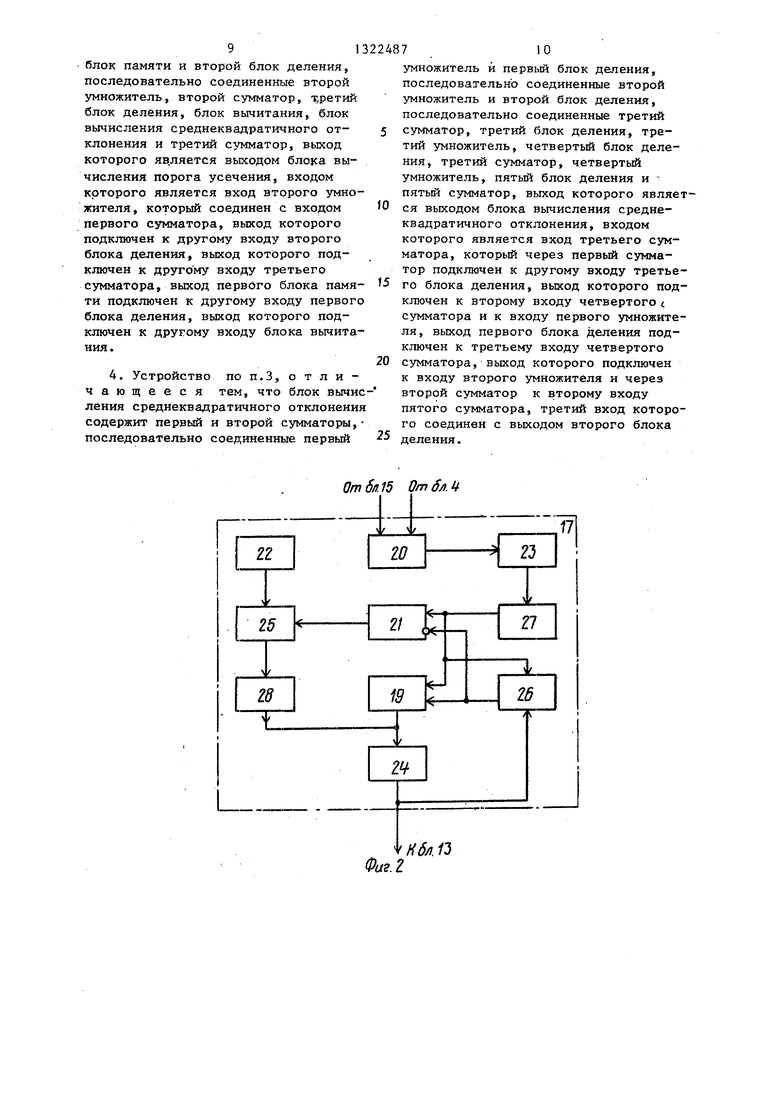

Формирователь 17 порога усечения (фИг.2) содержит первый, второй и третий элементы И 19 - 21, первый, . второй и третий блоки 22 - 24 памяти блок 25 вьиитани, блок 26 сравнения, блок 27 в ычисления порога усечения и блок 28 деления.

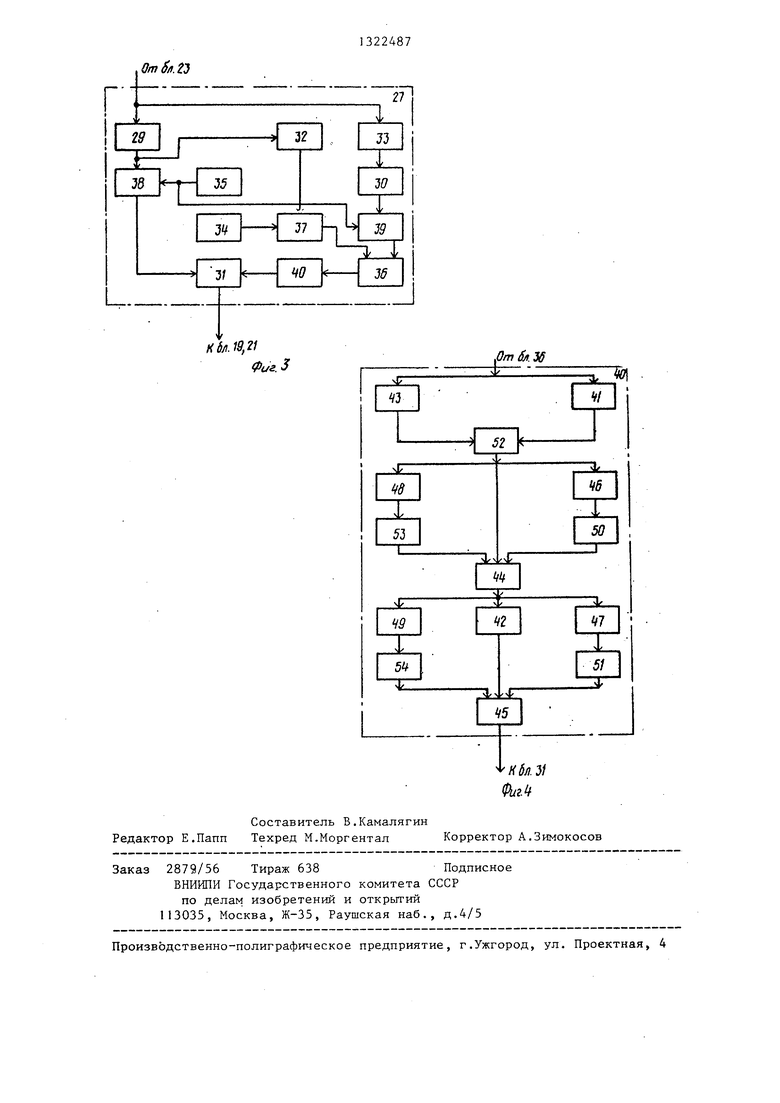

Блок 27 вычисления порога усечени (фиг.З) содержит первый, второй и третий сумматоры 29 - 31 , первый и второй умножители 32 и 33, первый и второй блоки 34 и 35 памяти, блок 36 вычитания, первый, второй и третий блоки 37-39 деления и блок 40 вычисления среднеквадраткч;ного отклонения .

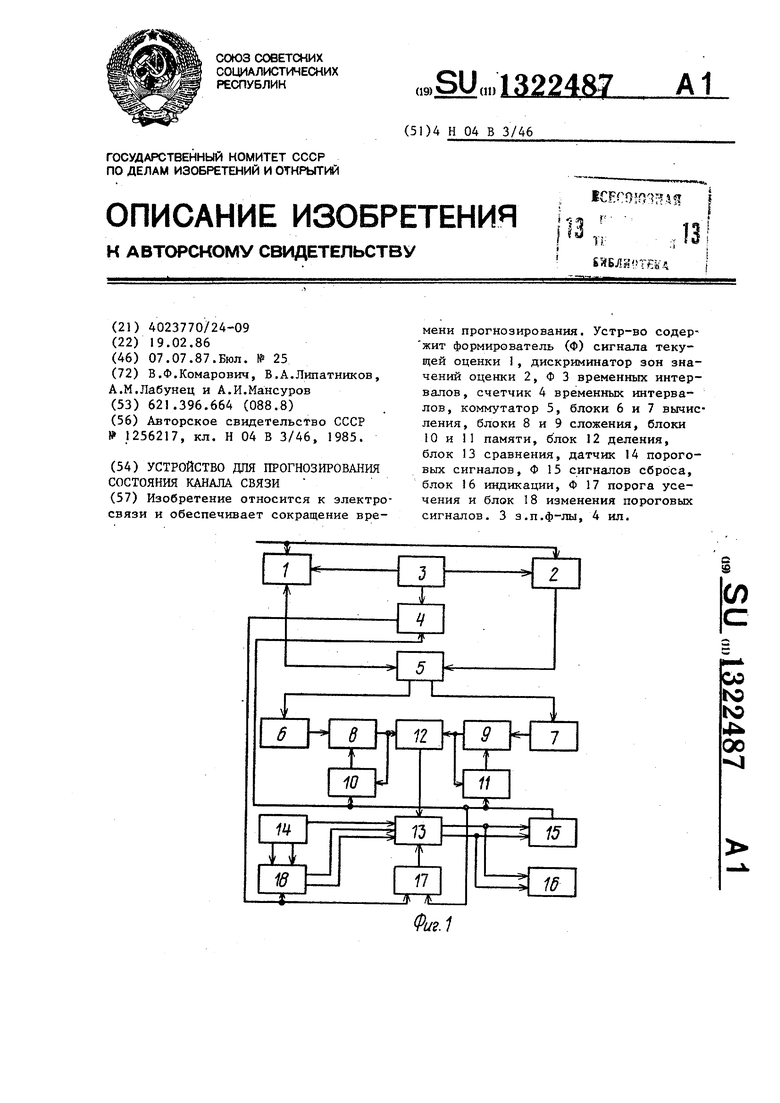

Блок 40 вычисления среднеквадратичного отклонения (фиг„4) содержит первый, второй, третий, четвертый и пятый сумматоры 41 - 45, первый, вто

рой, третий и четвертый умножители 46 - 49 и первьй, второй, третий, четвертый и пятый блоки 50-54 деления.

224872

Устройство (фиг„1) работает следующим образом.

Сигнал Ошибка поступает на входы формирователя 1 сигнала теку- 5 щей оценки и дискриминатора 2 зон значений оценки. Формирователь 1 сигнала текущей оценки просчитьтает ошибки в течение интервала измерения (т ), задаваемого формирователем 3

ному числу ошибок (при оценке А) и при отсутствии ошибок (оценка Н)

2 зон значений оценки разделяет возможное число ошибок за интервал времени Ти при оценке Н (А) на га зон (т 10), при этом максимально возможприсваивается неивысший номер зоны

К.

промежуточным зонам присваивают

ся номера K (j l ,m). Счетчик 4 временных интервалов осуществляет подсчет количества наблюдаемых интервалов времени и вьщает сигнал о номере временного интервала на формирователь 17 порога усечения. Коммутатор 5 в со-

ответствии с поступающим на него сигналом Норма или Авария обеспечивает подключение сигнала о номере зоны соответственно на вход первого блока 6 вычисления или на вход вторс

го блока 7 вычисления, где на основе сигнала о номере зоны K.(,m), об- щего числа зон m и максимального числа п

г(п

микс «акс

Р.,,) производится построение приращений лР|(п) или 4F. (п) эмпирических интегральных / функций распределения исправного и аварийного состояния канала связи на п-м интервале наблюдения

,р(,) . -- itL-M-; макс

4F,(n) - - 1- jN-rr((i.C

В первом и втором блоках 8 и 9 сложения производится, суммирование значений приращений дРц (п) и ЛГд(п) с соответствующими значениями эмпирической интегральной функции распре- деления, вычисленной за (п-1) временных интервалов 1 Гн(п-1) и Fy,(n-l), которые поступают с выходов первого и второго блоков 10 и 11 памяти.

Р„(п) F(n-l) + ); F(n) Тд (n-1) + 4F (n).

Значения F(n) и Fд (n) поступают на входы блока 12 деления и на запись в первый и второй блоки 10 и I1 памяти.

Блок 12 деления осуществляет операцию арифметического деления

-1;§

и вьщачу значения арифметического отношения правдоподобия logl(n) L(n) на вход блока 13 сравнения.

Блок 13 сравнения на основе сравнения L(n) со значениями пороговых сигналов

g,(n) Ci(l-n/n,,) ; g(n) CjCl-n/n c) ,

где --- ;

Г-Г0 и - заданные вероятности ошибок 1-го и 2-го рода;

гиг - параметры, характеризующие начальные значения крутизны сходящихся по- рогов и определяющие скорость приближения процесса к усечению задаваемых из блока 18 изменения пороговых сиг налов,

обеспечивает принятие решения о прогнозируемом состоянии канала связ

Решающее правило записьюается следующим образом: при L(n) g (п) принимается решение Норма ; при L(n)4 g2(n) принимается решение Авария ; при gj(n) L(n) ; ) решение не принимается, наблюдения про должаются на (п+1) интервале (п+1

м«кс кс

После наблюдения п .-го интерваДтоКС

ла, определяемого формирователем 17 порога усечения, сигнал с его выхода поступает в блок 13 сравнения, в котором L(. Р(. ) сравнивается со значением порога С, задаваемого датчиком 14 пороговых сигналов.

0

.,

0

5

0

5 0

.

Решающее правило в этом случае записьшается следующим образом: при L(.) 7 С принимается решение Нор-, ма ; при Ь() С принимается решение Авария.

Сигнал с выхода блока 13 сравнения подается на вход формирователя 15 сигналов сброса, с выхода которого подается сигнал на сброс счетчика 4 временных интервалов, на первый и второй блоки 10 и I1 памяти для перевода их в исходное состояние и на формирователь 17 порога усечения, для формирования нового порога усечения .

Формирователь 17 порога усечения (фиг.2) работает следующим образом.

В процессе реализации .последовательной процедуры номера временных интервалов, выдаваемых счетчиком 4 временных интервалов в такте с .управляющим сигналом Сброс, поступающим от формирователя 15 сигналов сброса в момент принятия решения о качестве канала связи, проключаются вторьм элементом И 20 на второй блок 23 памяти, информация из которого после заполнения считьтается в блок 27 вычисления порога усечения, откуда вновь вычисленное значение порога поступает на блок 26 сравнения, первый и третий элементы И 19 и 21 . В результате сравнения Р--ГО значения порога усечения с Р; -м, хранящимся в третьем блоке 24 памяти, на первый и третий элементы И 19 и 21 поступает 1 или О, означающие соответственно, что Р,- PI или -.., Р,. Единица, поступаюп;ая из блока 26 . сравнения, инвертируясь, закрьшает третий элемент И 21 и открьшает первый элемент И 19, через который значение р. из блока 27 вычисления порога усечения записывается в третий блок 24 памяти, стирая старое значение порога усечения Р . Ноль, поступающий из блока 26 сравнения, закрывает первый элемент И 19, и, инвертируясь, открьтает третий элемент И 21, через который значение Р. поступает на первый блок 25 вычитания. В этом блоке от значения нам .вычитается значение Р , записанное в первом блоке 22 памяти, затем результат делится на два в блоке 28 деления и записьшается в третий блок 24 памяти, стирая старое значение порога усечения Р.т . До тех пор, пока Р :| не

будет заменен описанным способом на

р.

1+Т

в блок I3 сравнения (фиг.1)

будет поступать пороговое значение момента усечения, равное Р .

Блок 27 вычисления порога усече- НИН (фиг.З) работает следующим образом .

Из второго блока 23 памяти (фиг.2) значения Х моментов принятия решения о состоянии канала связи поступают на первый сумматор 29 и второй умножитель 33 (фиг.З). В первом сумматоре 29 накапливается сумма Х,

поступающих значений Х и выдается на второй блок 38 деления и первьш умножитель 32. Во втором блоке 38

деления производится операция деления

«

суммы

2 X на величину М, постуь .. д 1.СЛ. 1 4.WAXJ. -. 9 ллч л j1/4

пающую из второго блока 35 памяти и равную объему второго блока 23 памяти, т.е. происходит вычисление усредненного значения номера интервала принятия решения Хц.

. Во втором умножителе 33 произво- дится операция умножения поступаю- ,,щих значений Хц самих на себя и по- тактовая выдача X.. во второй суммаN

тор 30, где происходит вычисление

м

1

суммы 2 Х„. Полученная таким обра 1

21 Х в третьем блоке 39

деления дeJштcя на величину М, посту25

L

К-1

зом сумма

В третьем сумматоре 31 вьшисляется величина Р. порога усечения, равная сумме величины X,, поступающей из второго блока 38 деления, и 6 , поступающей из блока 40 вьтисления среднеквадратичного отклонения, т.е. Р X + 6 .

Блок 40 вычисления среднеквадратичного отклонения (фиг,4) работает следующим образом.

Вычисленное в блоке 36 вычитания значение дисперсии поступает на пер30 вый и третий сумматоры 41 и 43, где происходит операция сложения соответственно с -1 и +1, т.е. BbRHc- ление (D-1) и (D+J)- Затем в третьем . блоке 52 деления происходит вычисле- пающую из второго блока 35 памяти. 35 ние отношения (D-1)/(D+1) и выдача

результата на первый вход четвертого сумматора 44, первый и третий умножители 46 и 48. В третьем умножителе 48 и в четвертом блоке 53 деления

40 производится последовательное вычисление второго слагаемого разложения InD путем умножения (D-1)/(D+1) самого на себя трижды и деления полученной величины на три, т.е.

(D-l)/(D+l)i .

В первом умножителе 46 и в перв ом блоке 50 деления вычисляется последовательно третий член разложения,

о

равный -p(D-l )/(D+l )- . В четвертом

сумматоре 44 эти три величины складываются, т.е. вьиисляется

InD D-1 (D-1)

у -2-- -5;г 3 (5;Г)-

№-if 5(D-H)5

В первом умножителе32 производится операция умножениявеличины сум- л

мы 21 Х|, полученнойиз первого сумки

матора 29, самой на себя и выдачи

t

Хц)в первый блок 37

результата ( - /ч,

деления. В последяем величина

:1

45

(Z-. Х,,) делится на величину М перКп

вого блока 34 памяти и вьщается на блок 36 вычитания. В последнем вычисляется значение дисперсии D величины X путем вычитания величины L

( 2 Х)/М,поступающей из первого 50

К 1

блока 37 деления, из величины

А

Z X ./м, поступающей из третьего

цц ,

блока 39 деления.„

В блоке 40 вычисления среднеквад- ратичнбго отклонения производится процедура извлече-ния квадратного корня из D путем разложения величины

6 до третьего члена включиьо . 2(2ji .i-(|ii,n

..

+

5 D+1

деления величины InD на два, т.е.

InD У -2 вычисление среднеквадратического отклонения ( разложением

в ряд (до третьего члена включитель

но) величины е

1

-}

ч-1--.

разложения yV2, в

и значение у подается на второй и четвертый умножители 47 и 49, а также на второй сумматор 42. В четвертом умножителе 49 и пятом блоке 54 деления последовательно происходит вьиисление второго члена величины е в ряд, т.е. четвертом умножителе 49 - умножение у самого на себя .а в пятом блоке деления 54 - деление на два. Анало- гично во втором умножителе 47 и во втором блоке 51 деления вычисляется третий член разложения е , т.е. у /6. В пятом сумматоре 45 вычисляеся среднеквадратичное отклонение 6 е- путем сложения сигналов , поступающих по трем входам сумматора, т.е.

б

-У + Х 1 2

ЗТ

Из пятого сумматора 45 величина 6 подается на третий сумматор 31.

Формула изобретения

1. Устройство для прогнозирования состояния канала связи, содержащее первый и второй блоки памяти, датчик пороговых сигналов, блок индикации, дискриминатор зон значений оценки и формирователь временных интервалов, последовательно соединенные первый блок вычислений и первый блок сложения, последовательно соединенные формирователь сигнала текущей оценки, коммутатор, второй блок вычислений, второй блок сложения, блок деления, блок сравнения, формирователь сигналов сброса, счетчик временных интервалов и блок измерения пороговых сигналов, выходы которого подключены к второму и третьему входам блока сравнения, четвертый вход которого соеди нен с первым выходом датчика пороговых сигналов, второй и третий вьпсо- ды которого подключены к второму и третьему входам блока измерения пороговых сигналов, выход блока сравнения подключен к блоку индикации, а выход формирователя сигнала сброса подключен к первым входам первого и второго бло1еов памяти, выход первого блока сложения подключен к другому входу блока деления и к второму входу первого блока памяти, выход которого подключен к другому входу первого блока сложения, выход второго

0

5

0

5

0

0

5

блока сложения подключен к другому входу второгоблока памяти, выход которого подключен к другому входу второго блока сложения, другой выход коммутатора подключен к входу первого блока вычислений, а другой вход соединен с выходом дискриминатора зон значений оценки, первьм вход которого является входом устройства и соединен с первым входом формирователя сигнала текущей оценки, второй вход которого соединен с первым выходом формирователя временных интервалов, второй выход которого подключен к другому входу счетчика временных интервалов, третий выход подключен к второму входу дискриминатора зон значений оценки, отличающее- с я тем, что, с целью сокращения времени, введен формирователь порога усечения, выход которого подключен к пятому входу блока сравнения, первый вход соединен с выходом счетчика временных интервалов, а второй вход соединен с выходом формирователя сигналов сброса.

2.Устройство по П.1, о т л и - чаюр;ееся тем, что формирователь порога усечения содержит первый блок памяти, блок сравнения и первый элемент И, последовательно соединенные второй элемент И, второй блок памяти, блок вычисления порога усечения, третий элемент И, блок вычитаний, блок делений и третий блок памяти, выход которого является выходом формирователя порога усечения, первым и вторым входом которого являются первый и второй входы второго элемента И, выход первого блока памяти подключен к другому входу блока вычитаний, выход первого элемента И подключен к входу третьего блока памяти, первьм вход соединен с выходом блока вычисления порога усечения и с первым входом блока сравнения, выход которого подключен к инверсному входу третьего элемента И и второму входу первого элемента И, а второй вход соединен с выходом третьего блока памяти.

3.Устройство по п.2, о т .л и - чающееся тем, что блок вычисления порога усечения содержит первый блок памяти, последовательно соединенные первый сумматор, первый умножитель и первый блок деления, последовательно соединенные .второй

блок памяти и второй блок деления, последовательно соединеншае второй умножитель, второй сумматор, т ретий блок деления, блок вычитания, блок вычисления среднеквадратичного отклонения и третий сумматор, вькод которого яв.ляется выходом блока вычисления порога усечения, входом которого является вход второго умножителя, который соединен с входом первого сумматора, выход которого подключен к другому входу второго блока деления, выход которого подключен к другому входу третьего сумматора, выход первдго блока памяти подключен к другому входу первого блока деления, выход которого подключен к другому входу блока вычитания.

4. Устройство по п.З, о т л и - чающееся тем, что блок вычис ления среднеквадратичного отклонения содержит первый и второй сумматоры,- последовательно соединенные первый

Отбл15 ОтблЛ

0

5

0

5

умножитель и первгзй блок деления, последовательно соединенные второй умножитель и второй блок деления, последовательно соединенные третий сумматор, третий блок деления, третий умножитель, четвертьй блок деления, третий сумматор, четвертый умножитель, пятый блок деления и пятый сумматор, выход которого является выходом блока вычисления среднеквадратичного отклонения, входом которого является вход третьего сумматора, который через первый сумматор подключен к другому входу третьего блока деления, выход которого подключен к второму входу четвертого сумматора и к входу первого умножителя, выход первого блока деления подключен к третьему входу четвертого сумматора, выход которого подключен к входу второго умножителя и через второй сумматор к второму входу пятого сумматора, третий вход которого соединен с выходом второго блока деления.

Фаг. г

Нбл. /3

OmS/i.tS

Г

Hdfl.lS,

Фиг.З

21

n

iE

:i

/)т&1.36

Iff

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| Устройство для прогнозирования состояния канала связи | 1985 |

|

SU1256217A2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Устройство для прогнозирования состояния канала связи | 1984 |

|

SU1195456A1 |

| Устройство для определения статистических характеристик случайного процесса | 1986 |

|

SU1341652A1 |

| СПОСОБ ФОРМИРОВАНИЯ ТЕКУЩЕГО ЭНЕРГЕТИЧЕСКОГО СПЕКТРА ВЫХОДНОГО СИГНАЛА ПРИЕМНИКА, УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ И СПОСОБ ИЗМЕРЕНИЯ ДАЛЬНОСТИ | 2007 |

|

RU2371736C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2004 |

|

RU2281549C1 |

| УСТРОЙСТВО КОНТРОЛЯ ЭНЕРГИИ, ПЕРЕДАВАЕМОЙ ПО ВОЛОКОННО-ОПТИЧЕСКИМ ЛИНИЯМ СВЯЗИ (ВАРИАНТЫ) | 1999 |

|

RU2152133C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

Изобретение относится к электросвязи и обеспечивает сокращение времени прогнозирования. Устр-во содер- жит формирователь (Ф) сигнала текущей оценки 1, дискриминатор зон значений оценки 2, Ф 3 временных интервалов, счетчик 4 временных интервалов, коммутатор 5, блоки 6 и 7 вычисления, блоки 8 и 9 сложения, блоки 10 и П памяти, блок 12 деления, блок 13 сравнения, датчик 14 пороговых сигналов, Ф 15 сигналов сброса, блок 16 индикации, Ф 17 порога усечения и блок 18 изменения пороговых сигналов. 3 з.п.ф-лы, 4 ил.

Редактор Е.Папп

Составитель Б.Камалягин

Техред М.Моргентал Корректор А,Зимокосов

Заказ 2879/56 Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Л (5л3/ Фиг. It

| Устройство для прогнозирования состояния канала связи | 1985 |

|

SU1256217A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-19—Подача