Фиг.1

I

Изобретение относится к элект}к измер 1- тельной технике и предназначено для измерения сопротивления изоляции электрических сетей переменного, постоя1шого и неременно-постоянного тока, находящихся под рабочим напряжением или обесточенных и имеющих значительные емкости фаз (полюсов) относительно корпуса.

Цель изобретения - расширение функциональных возможностей за счет обеспечения измерения сопроти ления изоляции сетей постоянного, переменного и постоянно- переменного тока, находящимся под рабочим напряжением или обесточенных и имеющ,их емкости полюсов (фаз) относительно корпуса, при одновременном повьпнемии и сохранении быстродействия.

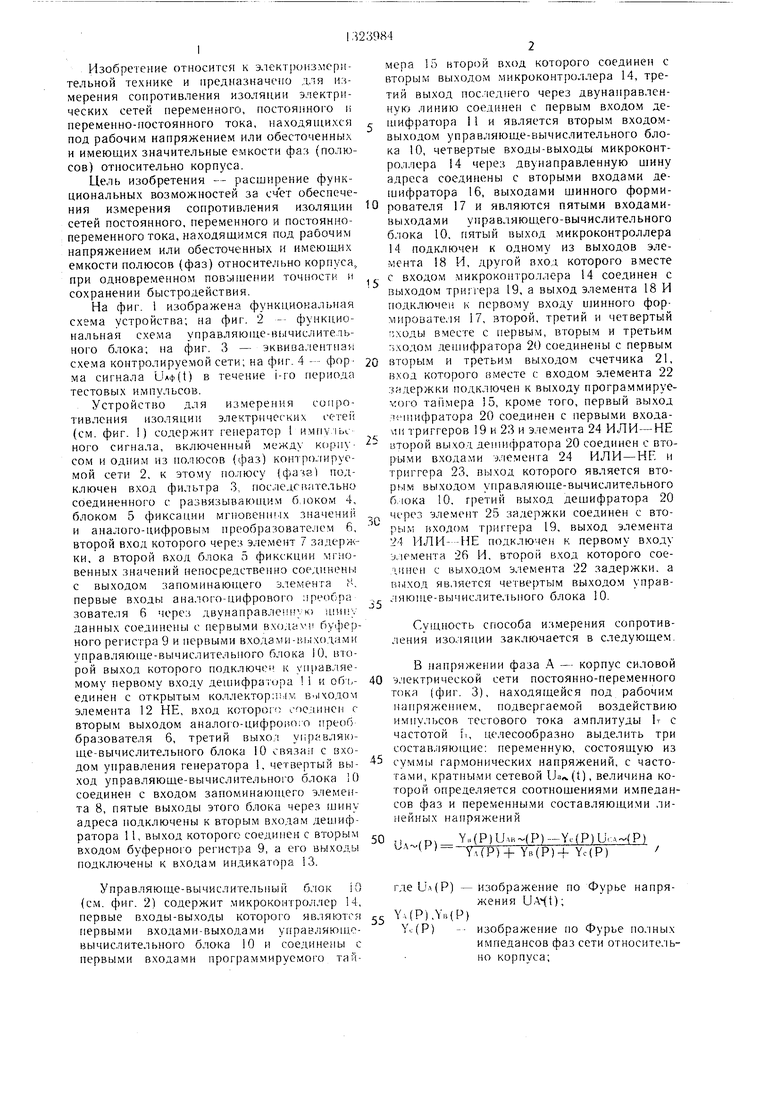

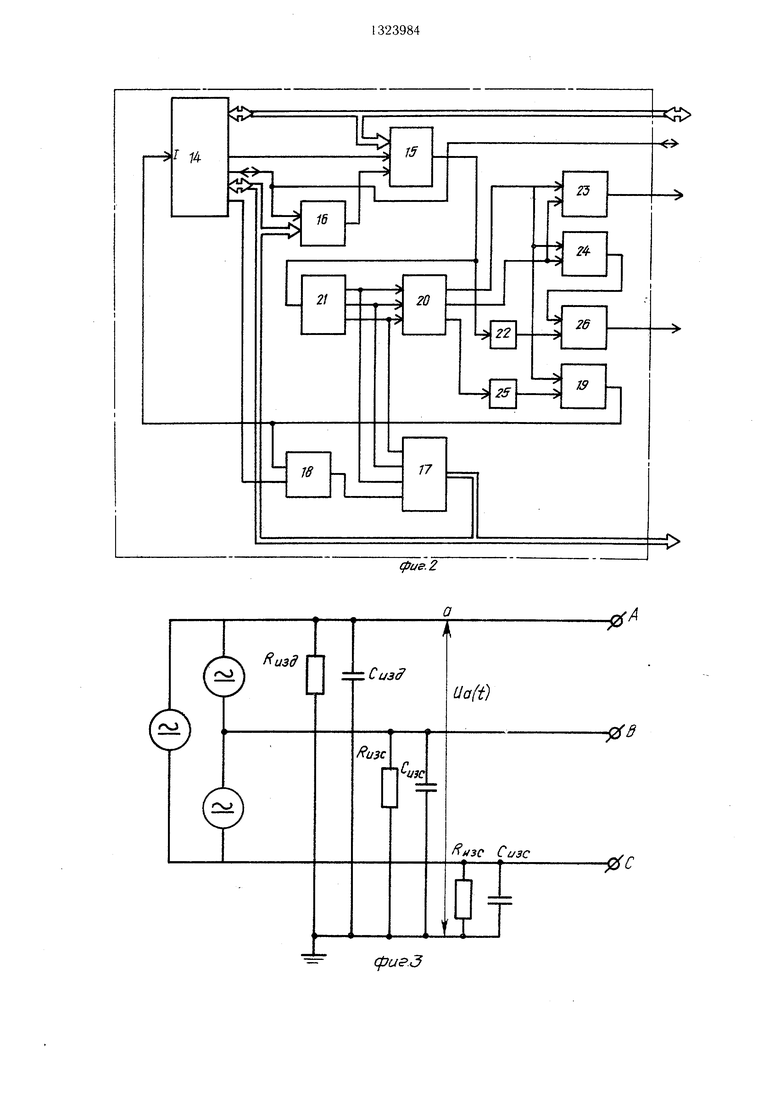

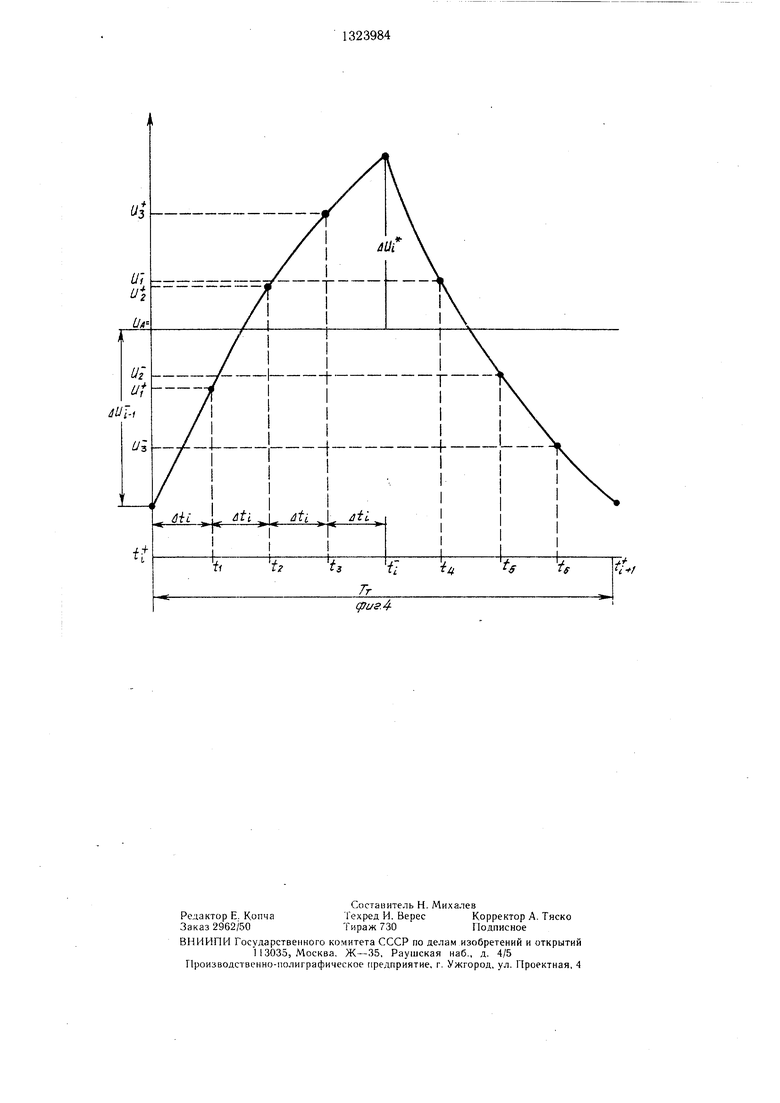

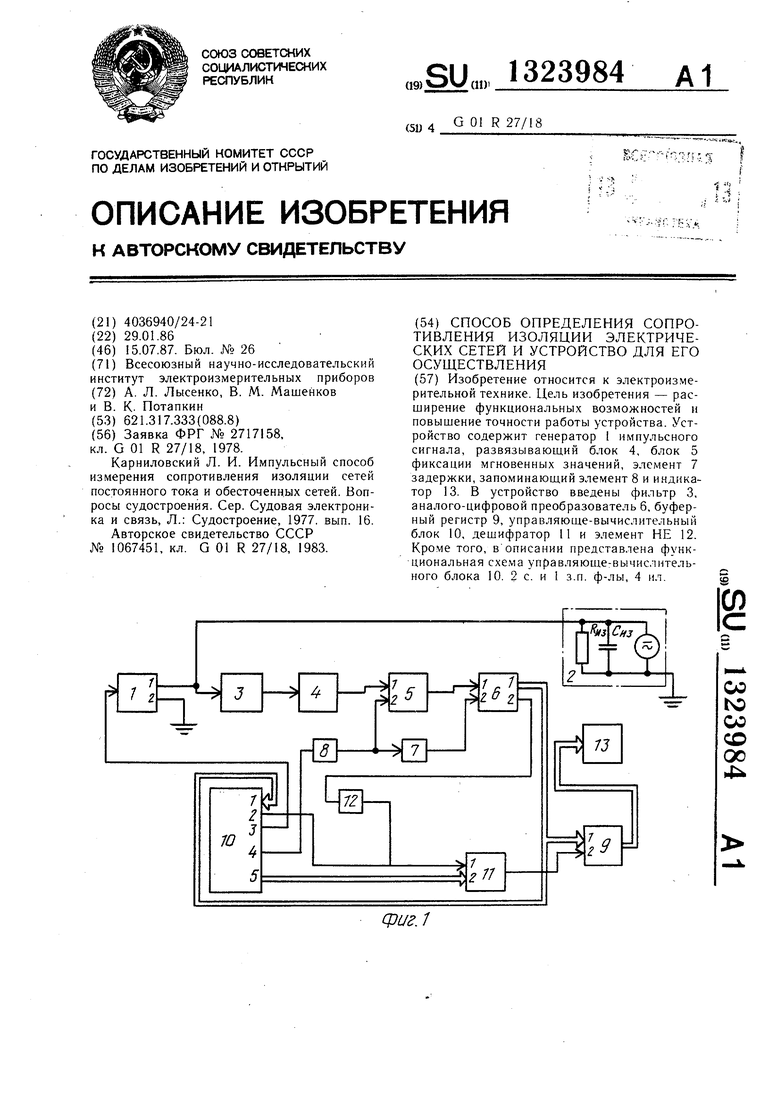

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема управляюнге-вычислитель- ного блока; на фиг. 3 - эквивалентная схема контролируемой сети; на фиг. 4 --- форма сигнала илф(1) в течение i-ro периода тестовых импульсов.

Устройство для измерения сопротивления изоляции электрических ccTeii (см. фиг. 1) содержит генератор I импу 1Ьс ного сигнала, включеннь.т между корпусом и одним из полюсов (4 аз) конп ро.;|ируе- мой сети 2, к этому полюсу (фаза) подключен вход фильтра 3, последовательно соединенного с развизываюищм блоком 4, блоком 5 фиксации мгновенных значений и аналого-цифровым преобразователем 6, второй вход которого через элемент 7 задержки, а второй вход блока 5 фикскции мгновенных значений непосредственно сорд1 нены с выходом запоминающего элемента , первые входы аналого-цифрового iipeoopa зователя 6 через двунаправлеи1г к тип-, данных соединены с первыми в.ходауи буферного регистра 9 и первыми входа ми-р,. 1,амн управляюще-вычислителыюго блока 10, вю- рой выход которого подключен к управ;1яе- мому первому входу дешифратора i и объединен с открытым КОЛЛеКТОр; Ь М Вч1ХО.ДОМ

элемента 12 НЕ, вход которого -оединем с вторь м выходом анало1Т)-цифро; о; о гфеоб бразователя 6, третий выхол управляю- ще-вычислительного блока 10 связан с входом управления генератора 1, четвертый выход управляюще-вычислительного блока 10 соединен с входом запомннаюн|,его элемента 8, пятые выходы этого блока через шину адреса подключены к вторым входам дешифратора i 1, выход которого соединен с вторым входом буферно1 о регистра 9, а его выходы подключены к входам индикатора 13.

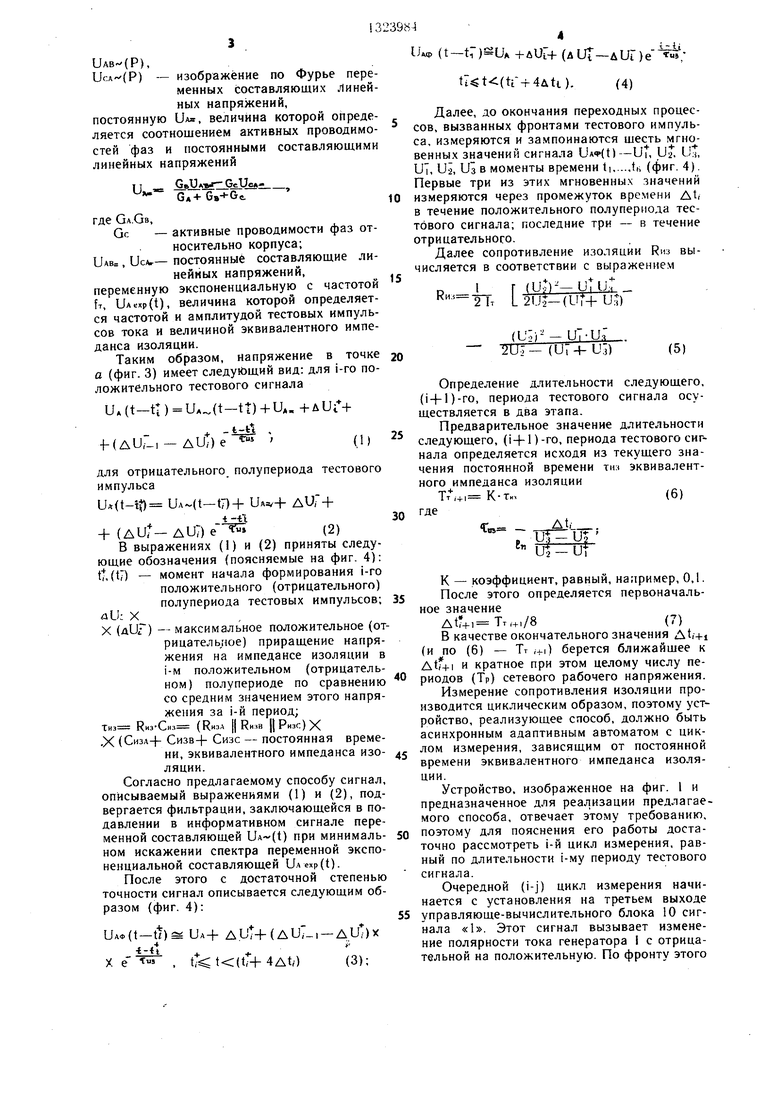

Управляюще-вычислительный блок iO (см. фиг. 2) содержит микроконтроллер 14, первые входы-выходы которого являются первыми входами-выходами управляюплс- вычислительного блока 10 и соединены с первыми входами программируемого тай

23984

2

мера 15 второй вход которого соединен с вторым выходом микроконтроллера 14, третий выход пос.чедиего через двунаправленную линию соединен с первым входом де- с шифратора i 1 и является вторым входом- выходом управляюще-вычислительного блока 10, четвертые входы-выходы микроконтроллера 14 через двунаправленную тину адреса соединены с вторыми входами дешифратора 16, выходами щинного форми10 рователя 17 и являются пятыми входами- выходами управляющего-вычислительного блока 10, пятый выход микроконтроллера 14 подключен к одному из выходов элемента 8 И, другой вход которого вместе

,г с входом микроконтроллера 14 соединен с выходом триггера 19, а выход элемента 18 И подключен к первому входу ujHHHoro формирователя 17, второй, третий и четвертый ;ходы вместе с первым, вторым и третьим оходом де1пифратора 2() соединены с первым

20 вторым и третьим выходом счетчика 21, вход которого вместе с входом элемента 22 задержки подключен к выходу програ.ммируе- Yoro таймера 15, кроме того, первый выход . шифратора 20 соединен с первыми входами триггеров 19 и 23 и элемента 24 ИЛИ-НЕ

второй выход дешифратора 20 соединен с вторыми входами элемента 24 ИЛИ-НЕ и триггера 23, выход которого является вто- ры.м выходом управляюнхе-вычислительного б/юка 10, гретий выход дешифратора 20

,„ через элемент 25 задержки соединен с вторым входом триггера 19, выход элемента 24 ИЛИ- -НЕ подключе} к первому входу элемента 26 И, второй вход которого сое- /UineH с выходом элемента 22 задержки, а выход является четвертым выходом управ- ляю1це-вычислите, ьного блока 10.

35

Сущность способа измерения сопротивления изо. заключается в следующем.

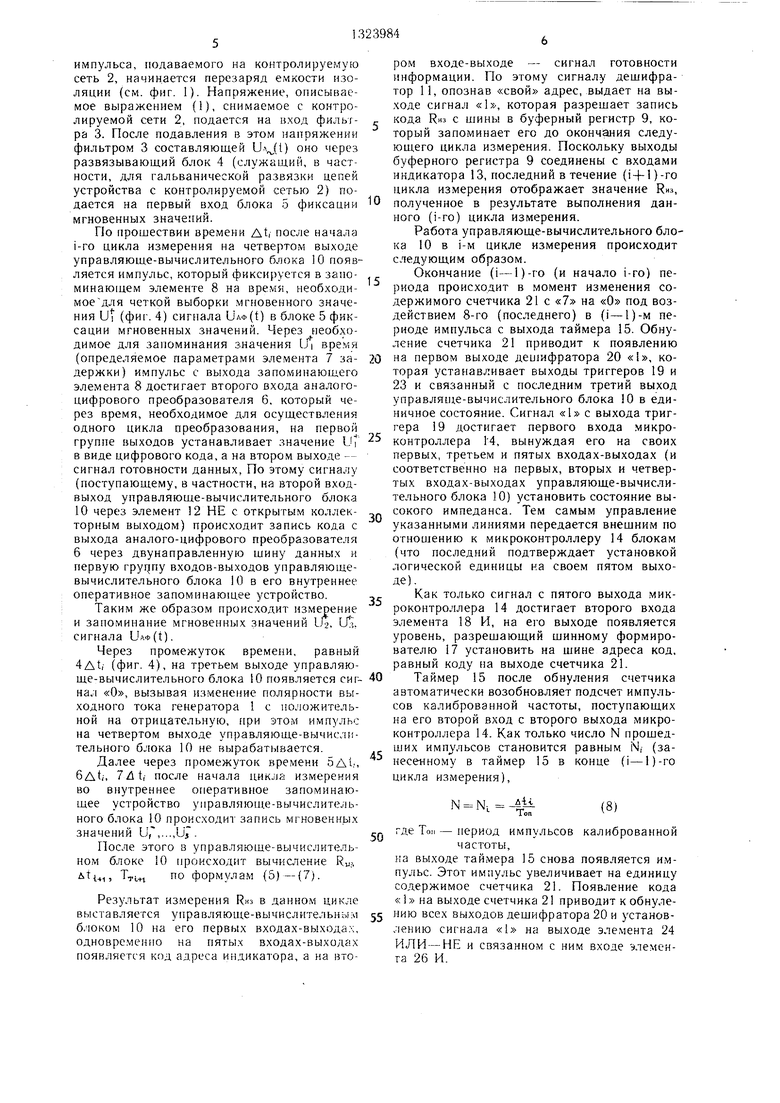

В напряжении фаза А - корпус силовой 40 электрической сети постоянно-переменного токя (фиг. 3), находящейся под рабочим напряжением, подвергаемой воздействию импульсов тестового тока амплитуды 1т с частотой Ь, целесообразно выделить три составляющие: переменную, состоящую из -45 суммы гармонических напряжений, с частотами, кратными сетевой Ua(t), величина которой определяется соотношениями импедан- сов фаз и переменными составляющими линейных напряжений

50 п..,р Y..(P))-Yc(P)U,....4P) ЬА (Г 7ГГР)4-YB(P)-f Yc(P)/

где UA(P) - изображение по Фурье напряжения LJ/Ht); Ул/Р),Ув(Р)

Vt(P) -- изображение по Фурье полных импедансов фаз сети относительно корпуса;

UAB (P),

UcA - (P) - изображение no Фурье переменных составляющих ;1иней- ных напряжений,

постоянную илл, величина которой определяется соотношением активных проводимо- стей фаз и постоянными составляющими линейных напряжений

- B B-Y-- где GA.GB,

GC -- активные проводимости фаз относительно корпуса;

UAB , Ucv- постоянные составляющие линейных напряжений,

переменную экспоненциальную с частотой т, UA«p(t), величина которой определяется частотой и амплитудой тестовых импульсов тока и величиной эквивалентного импеданса изоляции.

Таким образом, напряжение в точке а (фиг. 3) имеет следующий вид: для i-ro положительного тестового сигнала

и (t-tl) U(t-tt) + U, +AUi4

- t-tt

f (ли,, - ди,-)е

Т5Г

ДЛЯ отрицательного полупериода тестового импульса

UA(t-l) UA(t-17)+ UAv-f ли -f

+ (диГ-дШе (2)

В выражениях (1) и (2) приняты следующие обозначения (поясняемые на фиг. 4): tt(t7) - момент начала формирования i-ro положительного (отрицательного) полупериода тестовых импульсов; all; X

X (диГ) - максимальное положительное (от- рицателцмое) приращение напряжения на импедансе изоляции в i-M положительном (отрицательном) полупериоде по сравнению со средним значением этого напряжения за i-й период;

Тиз РИЗ-С..З (RHJA ЦКи.в || Ризс) X

Х (СизА-|-- Сизв- -- Сизс - постоянная времени, эквивалентного импеданса изоляции.

Согласно предлагаемому способу сигнал, описываемый выражениями (1) и (2), подвергается фильтрации, заключающейся в подавлении в информативном сигнале переменной составляющей UA-(t) при минимальном искажении спектра переменной экспоненциальной составляющей UAexp(t).

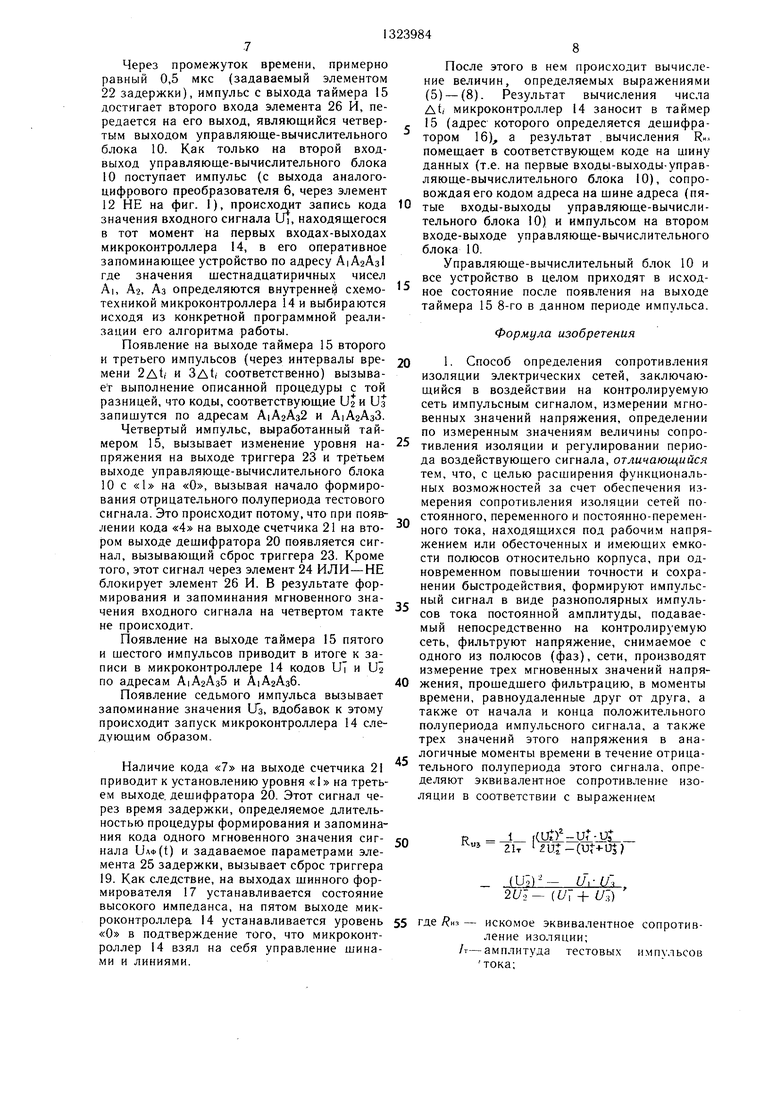

После этого с достаточной степенью точности сигнал описывается следующим образом (фиг. 4):

UA«(t-tt) UA+ диТ+(ди7.-1-ди)х

.±А

X е т,., , t, t(t,)(3);

и.Ф (t-tr)UA +uUr-f (лиТ-лиГ)

(tr + 4uti).

(4)

Далее, до окончания переходных процес- сов, вызванных фронтами тестового импульса, измеряются и зампоинаются щесть мгно- венны х значений сигнала UA4(t)-Ut, и. U-t,

Ub Us, Us в моменты времени t|tn (фиг. 4).

Первые три из этих мгновенны.х значений измеряются через промежуток времени Д1, в течение положительного полупериода тестового сигнала; последние три - в течение отрицательного.

Далее сопротивление изоляции Низ вычисляется в соответствии с выражением

о„,1 Г 1и)--у - 2 1т L 2UJ-(Ur

(U.;).t ,

2UJ-(Ur+ UJ)

20

(Uoi--uT-u.;.

- 2UJ- (Ur-4-из)

(5)

Определение длительности следующего, (i-i-l)-ro, периода тестового сигнала осуществляется в два этапа.

Предварительное значение длительности следующего, (i-+-1) -го, периода тестового сигнала определяется исходя из текущего значения постоянной времени тип эквивалентного импеданса изоляции

Тт, К-т.,(6)

30 гД

С„ - Р„ Цз - Ug

« ui-uf

к - коэффициент, равный, нагтример, 0,1. После этого определяется первоначальное значение

Тт,+,/8(7)

В качестве окончательного значения Д t,+i

(и по (6) - Тт i-i-i) берется ближайщее к

Д(+| и кратное при этом целому числу периодов (Тр) сетевого рабочего напряжения.

Измерение сопротивления изоляции производится циклическим образом, поэтому устройство, реализующее способ, должно быть асинхронным адаптивным автоматом с цик- лом измерения, зависящим от постоянной времени эквивалентного импеданса изоляции.

Устройство, изображенное на фиг. I и предназначенное для реализации предлагаемого способа, отвечает этому требованию, поэтому для пояснения его работы достаточно рассмотреть i-й цикл измерения, равный по длительности i-му периоду тестового сигнала.

Очередной (i-j) цикл измерения начинается с установления на третьем выходе управляюще-вычислительного блока 10 сигнала «1. Этот сигнал вызывает изменение полярности тока генератора I с отрицательной на положительную. По фронту этого

импульса, подаваемого на контролируемую сеть 2, начинается перезаряд емкости изоляции (см. фиг. 1). Напряжение, описываемое выражением (1), снимаемое с контролируемой сети 2, подается на в.ход фильтра 3. После подавления в этом напряжении фильтром 3 составляющей UA(I) оно через развязывающий блок 4 (служащий, в частности, для гальванической развязки цепей устройства с контролируемой сетью 2) подается на первый вход блока 5 фиксации мгновенных значений.

По прошествии времени At, после начала i-ro цикла измерения на четвертом выходе управляюще-вычислительного блока 10 появляется импульс, который фиксируется в запоминающем элементе 8 на время, необходимое для четкой выборки мгновенного значения Ut (фиг. 4) сигнала UAo(t) в блоке 5 фиксации мгновенных значений. Через необходимое для запоминания значения Ь| время (определяемое параметрами элемента 7 задержки) импульс с выхода запоминающего элемента 8 достигает второго входа аналого- цифрового преобразователя 6, который через время, необходимое для осуществления одного цикла преобразования, на первой группе выходов устанавливает значение УГ в виде цифрового кода, а на втором выходе - сигнал готовности данных, По этому сигналу (поступающему, в частности, на второй вход- выход управляюще-вычислительного блока 10 через элемент 12 НЕ с открытым коллекторным выходом) происходит запись кода с выхода аналого-цифрового преобразователя 6 через двунаправленную щи ну данны.х и первую груцпу входов-выходов управляюще- вычислительного блока 10 в его внутреннее оперативное запоминающее устройство.

Таким же образом происходит измерение и запоминание мгновенных значений 1. Ш. сигнала иАф(1).

Через промежуток времени, равный 4At,- (фиг. 4), на третьем выходе управляюще-вычислительного блока 10 появляется сигнал «О, вызывая изменение полярности выходного тока генератора 1 с положительной на отрицательнуво, при это.м импульс на четвертом выходе управляюще-вычислительного блока 10 не вырабатывается.

Далее через промежуток времени 5At.,, 6д(;, 7 Л t,- после начала цикла измерения во внутреннее оперативное запоминающее устройство управляюще-вычислительного блока 10 происходит запись мгновенн.ых значений U, ,...,ij7.

После этого в управляюще-вычислитель- ном блоке iO происходит вычисление R.r i tui, TTUI по формулам (5) -(7).

Результат измерения Циз в данном цикле выставляется управляюще-вычислительны.м 6, юком 10 на его первых входах-выходах, одновременно на пятых входах-выходах появляется код адреса индикатора, а на вто

0

5

0

5

0

5

ром входе-выходе - сигнал готовности информации. По этому сигналу дещифра- тор 11, опознав «свой адрес, выдает на выходе сигнал «1, которая разрещает запись кода RHS с щины в буферный регистр 9, который запоминает его до окончания следующего цикла измерения. Поскольку выходы буферного регистра 9 соединены с входами индикатора 13, последний в течение (i-f-l)-ro цикла измерения отображает значение Низ, полученное в результате выполнения данного (i-ro) цикла измерения.

Работа управляюще-вычислительного блока 10 в i-M цикле измерения происходит следующим образом.

Окончание (i-1)-го (и начало i-ro) периода происходит в момент изменения содержимого счетчика 21 с «7 на «О под воздействием 8-го (последнего) в (i-1)-м периоде импульса с выхода таймера 15. Обнуление счетчика 21 приводит к появлению на первом выходе деи1ифратора 20 «1, которая устанавливает выходы триггеров 19 и 23 и связанный с последним третий выход управляще-вычислительного блока 0 в единичное состояние. Сигнал «1 с выхода триггера 19 достигает первого входа микроконтроллера 14, вынуждая его на своих первых, третьем и пятых входах-выходах (и соответственно на первых, вторых и четвертых входах-выходах управляюще-вычислительного блока 10) установить состояние высокого импеданса. Тем самым управление указанными линиями передается внещним но отношению к микроконтроллеру 14 блокам (что последний подтверждает установкой логической единицы на своем пятом выходе).

Как только сигнал с пятого выхода микроконтроллера 14 достигает второго входа элемента 18 И, на его выходе появляется уровень, разрещающий щинному формирователю 17 установить на шине адреса код, равный коду на выходе счетчика 21.

Таймер 15 после обнуления счетчика автоматически возобновляет подсчет импульсов калиброванной частоты, поступающих на его второй вход с второго выхода микроконтроллера 14. Как только число N прощед- ших импульсов становится равным 1,- (занесенному в таймер 15 в конце (i-1)-го цикла измерения).

N N,4;

(8)

где Том - период импульсов калиброванной

частоты,

ка выходе таймера 15 снова появляется импульс. Этот импульс увеличивает на единицу содержимое счетчика 21. Появление кода «1 на выходе счетчика 21 приводит к обнулению всех выходов дешифратора 20 и установлению сигнала «1 на выходе элемента 24 ИЛИ-НЕ и связанном с ним входе элемента 26 И.

Через промежуток времени, примерно равный 0,5 МКС (задаваемый элементом 22 задержки), импульс с выхода таймера 15 достигает второго входа элемента 26 И, передается на его выход, являющийся четвертым выходом управляюще-вычислительного блока 10. Как только на второй вход- выход управляюще-вычислительного блока 10 поступает импульс (с выхода аналого- цифрового преобразователя 6, через элемент 12 НЕ на фиг. 1), происходит запись кода значения входного сигнала Ut, находящегося в тот момент на первых входах-выходах микроконтроллера 14, в его оперативное запоминающее устройство по адресу AiAgAsl где значения щестнадцатиричных чисел АЬ АЗ, АЗ определяются внутренней схемо- техникой микроконтроллера 14 и выбираются исходя из конкретной программной реализации его алгоритма работы.

Появление на выходе таймера 15 второго и третьего импульсов (через интервалы вре- мени 2At, и ЗД1, соответственно) вызывает выполнение описанной процедуры с той разницей, что коды, соответствующие U2 и Uj запишутся по адресам А1А2Аз2 и А|А2АзЗ.

Четвертый импульс, выработанный таймером 15, вызывает изменение уровня на- пряжения на выходе триггера 23 и третьем выходе управляюще-вычислительного блока 10 с «1 на «О, вызывая начало формирования отрицательного полупериода тестового сигнала. Это происходит потому, что при появлении кода «4 на выходе счетчика 21 на вто- ром выходе дешифратора 20 появляется сигнал, вызывающий сброс триггера 23. Кроме того, этот сигнал через элемент 24 ИЛИ-НЕ блокирует элемент 26 И. В результате формирования и запоминания мгновенного значения входного сигнала на четвертом такте не происходит.

Появление на выходе таймера 15 пятого и шестого импульсов приводит в итоге к записи в микроконтроллере 14 кодов U7 и Uz по адресам А|А2Аз5 и А|А2Аз6.

Появление седьмого импульса вызывает запоминание значения Ш, вдобавок к этому происходит запуск микроконтроллера 14 следующим образом.

Наличие кода «7 на выходе счетчика 21 при водит к установлению уровня «1 на третьем выходе, дешифратора 20. Этот сигнал через время задержки, определяемое длительностью процедуры формирования и запоминания кода одного мгновенного значения сиг

нала иАФ(1) и задаваемое параметрами элемента 25 задержки, вызывает сброс триггера 19. Как следствие, на выходах шинного формирователя 17 устанавливается состояние высокого импеданса, на пятом выходе микроконтроллера 14 устанавливается уровень «О в подтверждение того, что микроконтроллер 14 взял на себя управление ш ина- ми и линиями.

10

0

5

0

5

После этого в нем происходит вычисление величин, определяемых выражениями (5)-(8). Результат вычисления числа At, микроконтроллер 14 заносит в таймер 15 (адрес которого определяется дешифратором 16), а результат .вычисления RH. помещает в соответствующем коде на шину данных (т.е. на первые входы-выходы-управляюще-вычислительного блока 10), сопровождая его кодом адреса на щине адреса (пятые входы-выходы управляюще-вычислительного блока 10) и импульсом на втором входе-выходе управляюще-вычислительного блока 10.

Управляюще-вычислительный блок 10 и все устройство в целом приходят в исходное состояние после появления на выходе таймера 15 8-го в данном периоде импульса.

Формула изобретения

1. Способ определения сопротивления изоляции электрических сетей, заключающийся в воздействии на контролируемую сеть импульсным сигналом, измерении мгновенных значений напряжения, определении по измеренным значениям величины сопротивления изоляции и регулировании периода воздействующего сигнала, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения измерения сопротивления изоляции сетей постоянного, переменного и постоянно-переменного тока, находящихся под рабочим напряжением или обесточенных и имеющих емкости полюсов относительно корпуса, при одновременном повышении точности и сохранении быстродействия, формируют импульсный сигнал в виде разнополярных импульсов тока постоянной амплитуды, подаваемый непосредственно на контролируемую сеть, фильтруют напряжение, снимаемое с одного из полюсов (фаз), сети, производят измерение трех мгновенных значений напряжения, прошедшего фильтрацию, в моменты времени, равноудаленные друг от друга, а также от начала и конца положительного полупериода импульсного сигнала, а также трех значений этого напряжения в аналогичные моменты времени в течение отрицательного полупериода этого сигнала, определяют эквивалентное сопротивление изоляции в соответствии с выражением

50

55 где

R - fOZ J2LiU 21т 2Ut-(

. (Ш)WuJZL,

2t/.J- (,)

искомое эквивалентное сопротивление изоляции;

амплитуда тестовы.х импульсов тока;

uf...u;x

X (U, ...ц ) - значения напряжения, прошедшего фильтрацию в указанные BbjQie моменты epejVieHH в течение положительного (отрица- тельного) тестового сигнала, определяют значение постоянной времени эквивалентного импеданса изоляции в соответствии с выражением

Cuj -- - - tr,

л,

с/./- щ

детиз- искомая постоянная времени эквивалентного импеданса изоляции; д1, - промежуток времени между измерениями значений напряжения, прошедшего фильтрацию, пределяют длительность следующего пеиода воздействующего сигнала как велиину, пропорциональную постоянной вре- 20 еци эквивалентного импеданса и равную елому числу периодов переменной составяющей рабочего напряжения сети.

2. Устройство для определения сопротивления изоляции электрических сетей, со- 25 держащее генератор импульсного сигнала, индикатор, развязывающий блок, блок фиксации мгновенных значений, элемент задержки, причем первый вход блока фиксации гновенных значений соединен с выходом запоминающего элемента, отличающееся тем, 30 что с целью расширения функциональных возможностей, в него дополнительно введены фильтр, аналого-цифровой преобразователь, элемент НЕ с открытым коллекторным выходом, дешифратор, буферный регистр, управляюще-вычислительный блок, 35 причем один выход генератора импульсного сигнала объединен с входом фильтра и подключен непосредственно к одному из полюсов (фаз) контролируемой сети, другой выход генератора импульсного сигнала соеди- 40 нен с корпусом, причем генератор импульсного сигн ала представляет собой генератор разнополярных импульсов тока, выход фильтра соединен с входом развязывающего блока, выход блока фиксации мгновенных значений подключен к первому вхо- 45 ду аналого-цифрового преобразователя, второй вход которого соединен через элемент задержки с выходом запоминающего элемента, первые выходы аналого-цифрового преобразователя соединены через двунаправленную шину данных с объединенными меж- 0 ду собой первыми входами буферного регистра и первыми входами-выходами управ- ляюше-вычислительного блока, а второй выход аналого-цифрового преобразователя через элемент НЕ с открытым коллектор- - ным выходом подключен к двунаправленной линии, соединяющей первый вход дешифратора и второй вход-выход управляюще-вычис лительного блока, третий выход которого подключен к входу управления генератора импульсного сигнала, четвертый выход соединен с входом запоминающего элемента, а пятые выходы через щину адреса подключены к вторым входам дешифратора, выход которого связан с вторым входом буферного регистра, выходы которого подключены к входам индикатора.

3. Устройство по п. 2, отличающееся тем, что управляюще-вычислительный блок содержит микроконтроллер, два дешифратора, программируемый таймер, два триггера, элемент ИЛИ-НЕ, два элемента задержки, два элемента И, счетчик, шииный формирователь, причем первые входы-выходы микроконтроллера объединены с первыми входами программируемого таймера через двунаправленную щину данных и являются первыми входами-выходами управляюще-вычисли- тельного блока, второй выход микроконтроллера соединен с вторым входом программируемого таймера, третий вход последнего соединен с выходом первого дешифратора, первый вход которого через двунаправленную линию соединен с третьим выходом микроконтроллера и является вторым входом-выходом управляюще-вычислительного блока, вторые входы первого дешифратора соединены через двунаправленную щину адреса с выходами шинного формирователя и четвертыми входами-выходами микроконтроллера, которые являются пятыми входами-выходами управляюще-вычислителького блока, пятый выход микроконтроллера соединен с одним входом первого элемента И, другой вход которого объединен с входом микроконтроллера и подключается к выходу первого триггера, а выход первого элемента И соединен с первым входом шинного формирователя, второй, третий четвертый входы которого объединены с первым, вторым, третьим входами второго дешифратора и подклю- чень к первому, второму, третьему выходам счетчика, вход которого объединен с входом первого элемента задержки и подключен к выходу программируемого таймера, первый выход второго дешифратора соединен с первыми входами первого и второго триггера соответственно и одним из входов элемента ИЛИ-НЕ, второй выход второго дешифратора соединен с другим входом элемента ИЛИ-НЕ и вторым входом второго триггера выход которого является вторым выходом управляюше-вычислительного блока, третий выход второго дешифратора через второй элемент задержки соединен с вторым входом первого триггера, выход элемета ИЛИ-НЕ подключен к первому входу второго элемента И. второй вход которого соединен с выходом второго элемента задержки, а выход является четвертым выходом управляюще-вычислительного блока.

(риг.З

/

(pijs.4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения передаточной функции динамического звена | 1987 |

|

SU1432466A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| СПОСОБ КОНТРОЛЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ И ЗАЩИТЫ ЭЛЕКТРИЧЕСКОЙ СЕТИ | 1998 |

|

RU2144679C1 |

| Способ измерения сопротивления изоляции и емкости электрических сетей | 1990 |

|

SU1758592A1 |

| Способ стабилизации толщины изоляции кабеля и устройство для его реализации | 1982 |

|

SU1302248A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для тестовой проверки узлов контроля каналов ввода-вывода | 1979 |

|

SU922752A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Устройство предварительного автоматического контроля изоляции участка электрической сети | 1989 |

|

SU1661686A2 |

Изобретение относится к электроизмерительной технике. Цель изобретения - расширение функциональных возможностей и повышение точности работы устройства. Устройство содержит генератор импульсного сигнала, развязываюш,ий блок 4, блок 5 фиксации мгновенных значений, элемент 7 задержки, запоминаюш,ий элемент 8 и индикатор 13. В устройство введены фильтр 3, аналого-цифровой преобразователь 6, буферный регистр 9, управляюще-вычислительный блок 10, дешифратор 11 и элемент НЕ 12. Кроме того, в описании представлена функциональная схема управляюще-вычислитель- ного блока 10. 2 с. и 1 з.п. ф-лы, 4 ил. 1СЛ со to со СО ОО

| Неорганический поликристаллический сцинтиллятор на основе Sc, Er:ИАГ и способ его получения | 2019 |

|

RU2717158C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карниловский Л | |||

| И | |||

| Импульсный способ измерения сопротивления изоляции сетей постоянного тока и обесточенных сетей | |||

| Вопросы судостроения | |||

| Сер | |||

| Судовая электроника и связь | |||

| Л.: Судостроение, 1977 | |||

| вып | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Устройство для измерения сопротивления изоляции электрических сетей | 1981 |

|

SU1067451A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-07-15—Публикация

1986-01-29—Подача