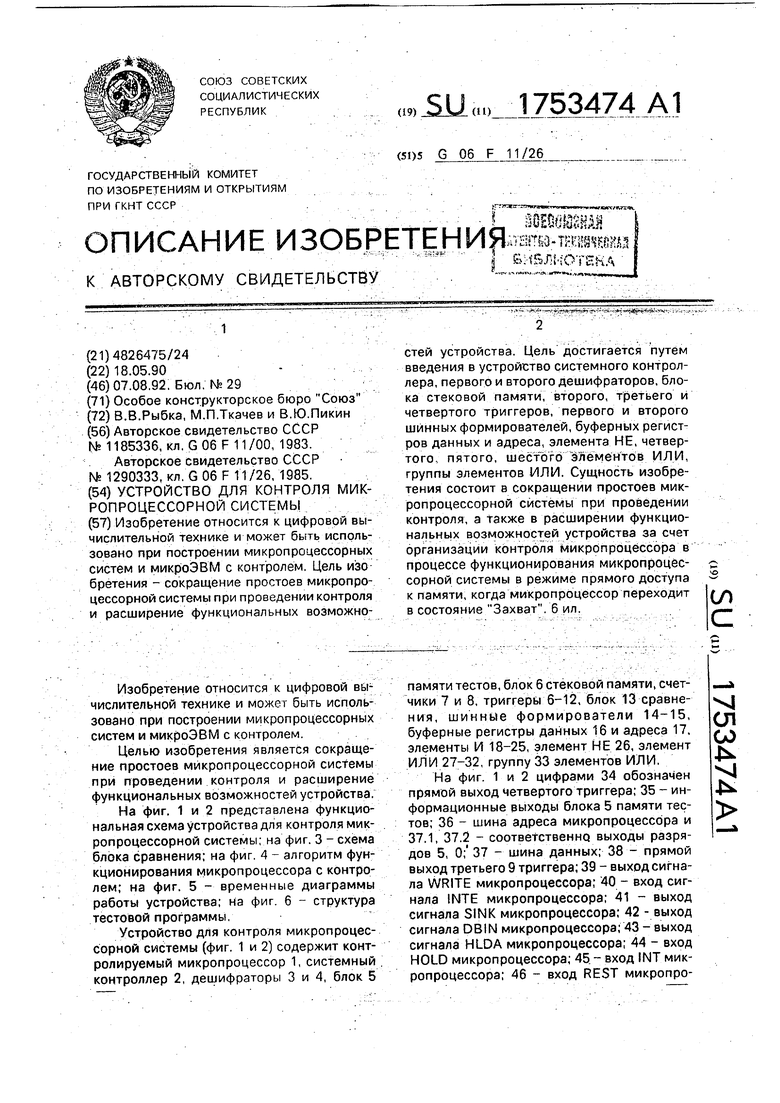

цессора; 47-51 - соответственно входы устройства с первого по пятый; 52 - группа управляющих выходов системного контроллера 2; 53 - второй выход первого 3 дешифратора; 54 - первый выход первого 3 дешифратора; 55 - выходы второго 8 счетчика; 56 - выход третьего элемента ИЛИ; 57 - выходы второго 14 шинного формирователя; 58 - выходы первого 15 шинного формирователя; 59-65 - соответственно пятый, второй, шестой, седьмой, первый, четвертый и третий выходы устройства.

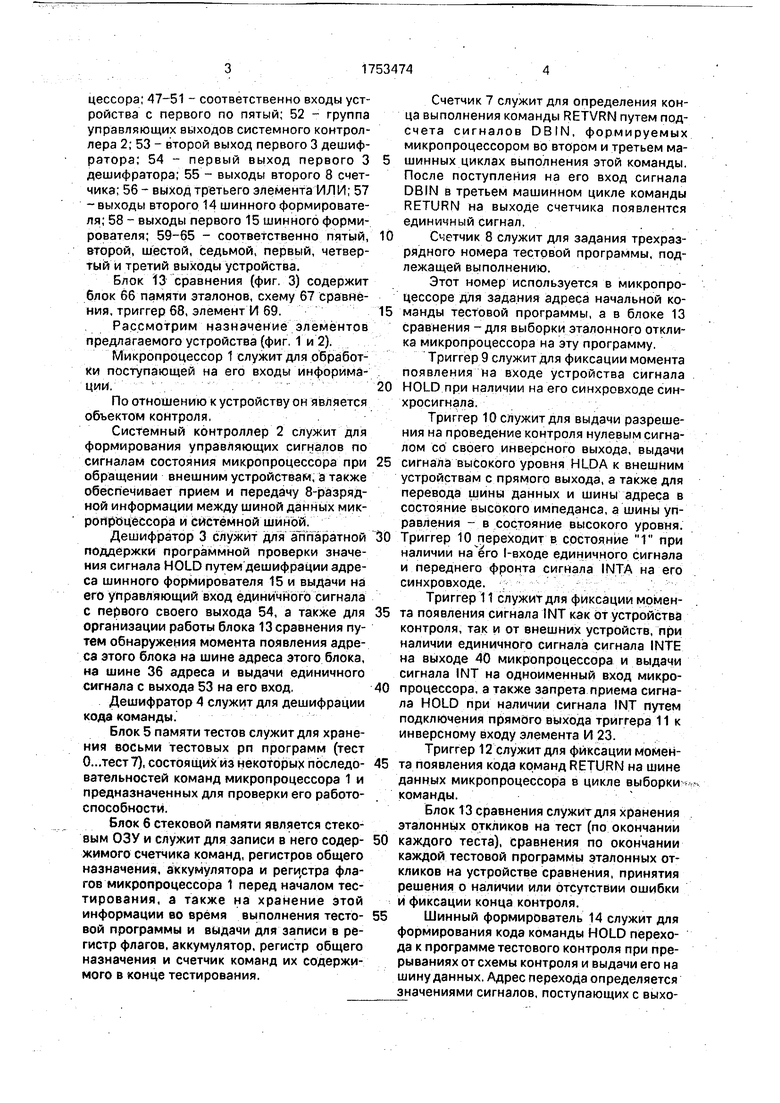

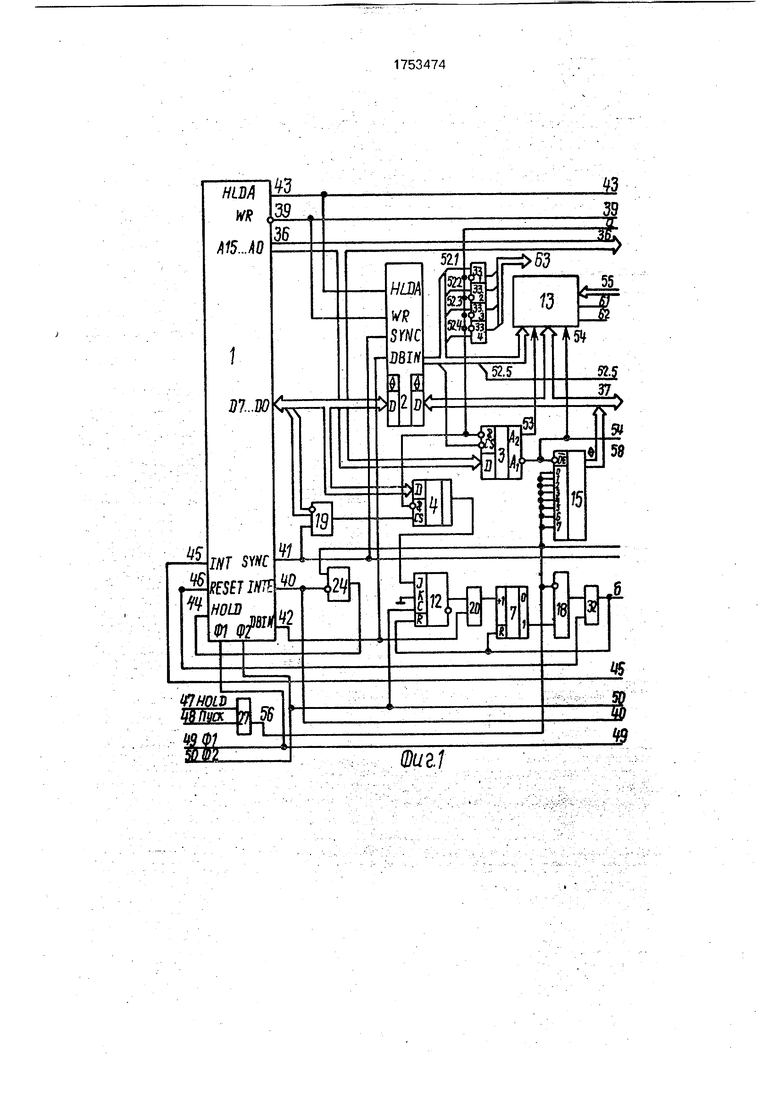

Блок 13 сравнения (фиг. 3) содержит блок 66 памяти эталонов, схему 67 сравнения, триггер 68, элемент И 69,

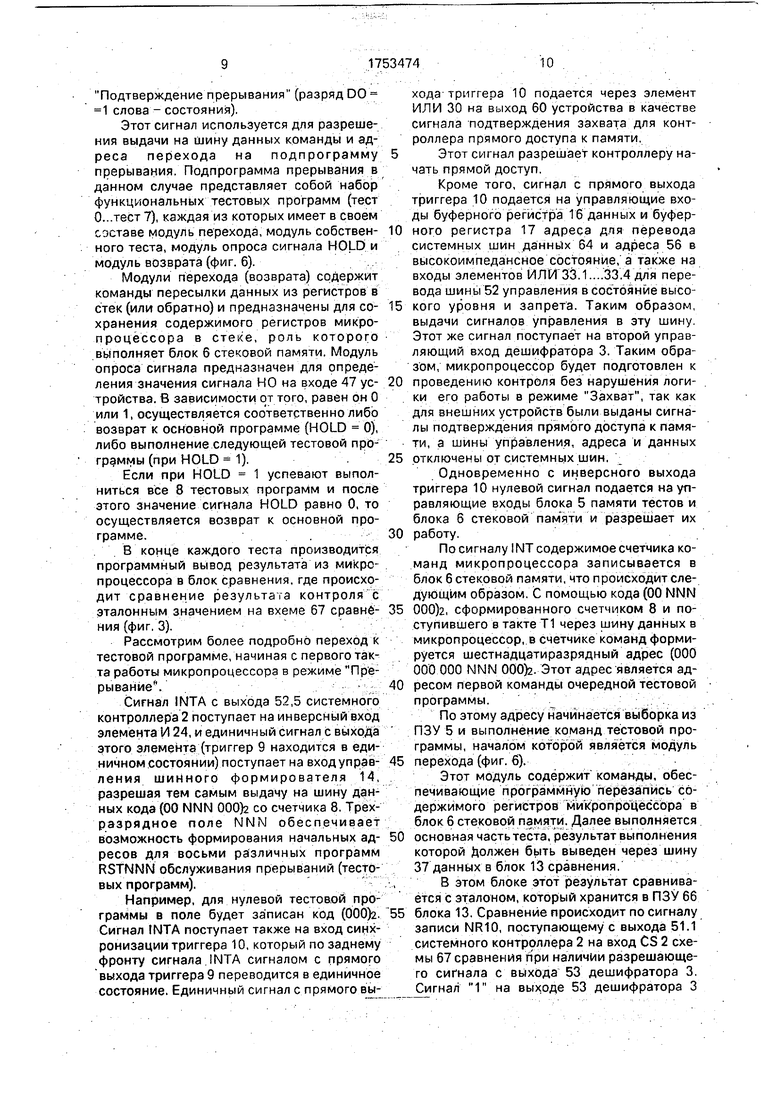

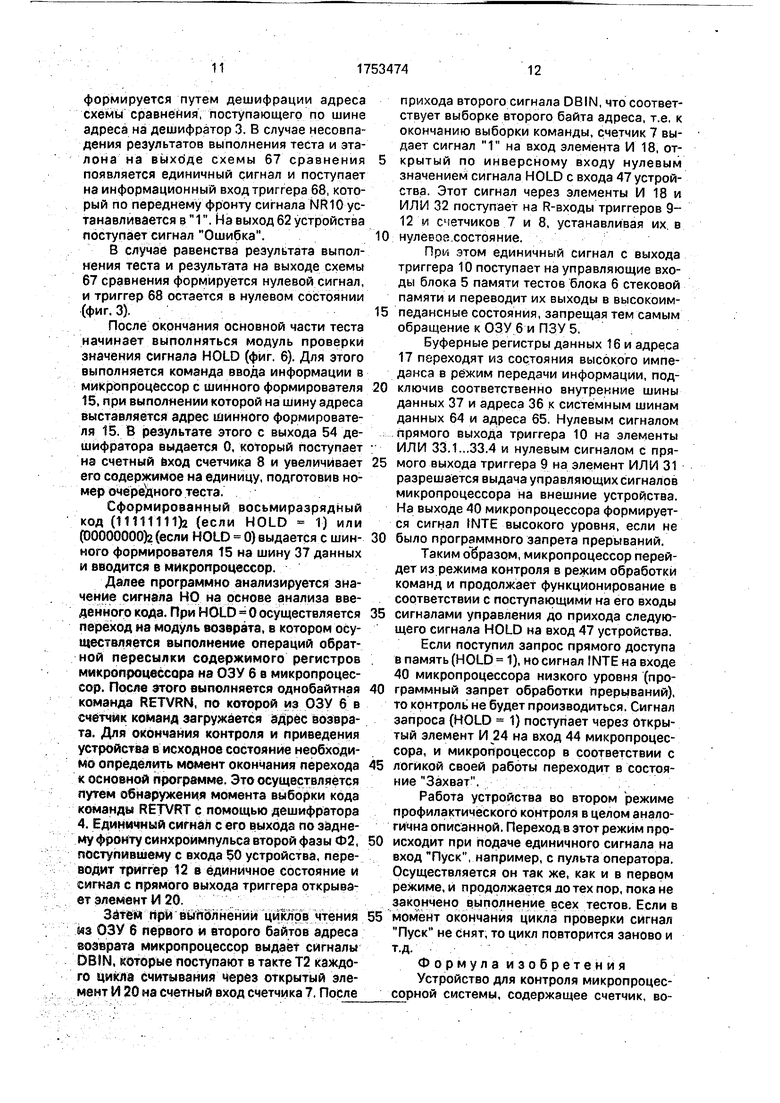

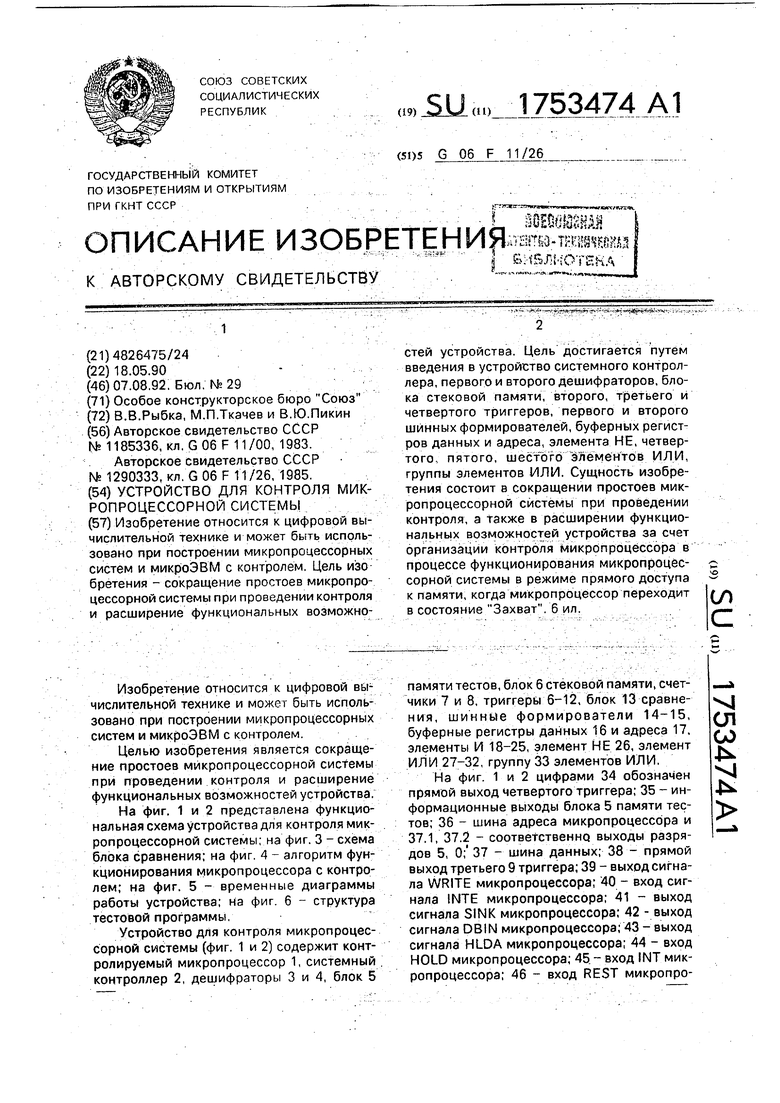

Рассмотрим назначение элементов предлагаемого устройства (фиг, 1 и 2).

Микропроцессор 1 служит для обработки поступающей на его входы инфорима- ции.

По отношению к устройству он является объектом контроля,

Системный контроллер 2 служит для формирования управляющих сигналов по сигналам состояния микропроцессора при обращении внешним устройствам, а также обеспечивает прием и передачу 8-разрядной информации между шиной данных микропроцессора и системной шиной.

Дешифратор 3 служит для аппаратной поддержки программной проверки значения сигнала HOLD путем дешифрации адреса шинного формирователя 15 и выдачи на его управляющий вход единичного сигнала с первого своего выхода 54, а также для организации работы блока 13 сравнения путем обнаружения момента появления адреса этого блока на шине адреса этого блока, на шине 36 адреса и выдачи единичного сигнала с выхода 53 на его вход,

Дешифратор 4 служит для дешифрации кода команды.

Блок 5 памяти тестов служит для хранения восьми тестовых рп программ (тест 0...тест 7), состоящих из некоторых последовательностей команд микропроцессора 1 и предназначенных для проверки его работоспособности.

Блок 6 стековой памяти является стековым ОЗУ и служит для записи в него содержимого счетчика команд, регистров общего назначения, аккумулятора и регистра флагов микропроцессора 1 перед началом тестирования, а также на хранение этой информации во время выполнения тестовой программы и выдачи для записи в регистр флагов, аккумулятор, регистр общего назначения и счетчик команд их содержимого в конце тестирования.

Счетчик 7 служит для определения конца выполнения команды RETVRN путем подсчета сигналов DBIN, формируемых микропроцессором во втором и третьем машинных циклах выполнения этой команды. После поступления на его вход сигнала DBIN в третьем машинном цикле команды RETURN на выходе счетчика появлентся единичный сигнал.

0 Счетчик 8 служит для задания трехразрядного номера тестовой программы, подлежащей выполнению.

Этот номер используется в микропроцессоре для задания адреса начальной ко5 манды тестовой программы, а в блоке 13 сравнения - для выборки эталонного отклика микропроцессора на эту программу.

Триггер 9 служит для фиксации момента появления на входе устройства сигнала

0 HOLD при наличии на его синхровходе синхросигнала.

Триггер 10 служит для выдачи разрешения на проведение контроля нулевым сигналом со своего инверсного выхода, выдачи

5 сигнала высокого уровня HLDA к внешним устройствам с прямого выхода, а также для перевода шины данных и шины адреса в состояние высокого импеданса, а шины управления - в состояние высокого уровня.

0 Триггер 10 переходит в состояние 1 при наличии на его 1-входе единичного сигнала и переднего фронта сигнала INTA на его синхровходе.

Триггер 11 служит для фиксации момен5 та появления сигнала INT как от устройства контроля, так и от внешних устройств, при наличии единичного сигнала сигнала INTE на выходе 40 микропроцессора и выдачи сигнала INT на одноименный вход микро0 процессора, а также запрета приема сигнала HOLD при наличии сигнала INT путем подключения прямого выхода триггера 11 к инверсному входу элемента И 23.

Триггер 12 служит для фиксации момен5 та появления кода команд RETURN на шине данных микропроцессора в цикле выборки команды.

Блок 13 сравнения служит для хранения эталонных откликов на тест (по окончании

0 каждого теста), сравнения по окончании каждой тестовой программы эталонных откликов на устройстве сравнения, принятия решения о наличии или отсутствии ошибки и фиксации конца контроля.

5 Шинный формирователь 14 служит для формирования кода команды HOLD перехода к программе тестового контроля при прерываниях от схемы контроля и выдачи его на шину данных. Адрес перехода определяется значениями сигналов, поступающих с выходов счетчика на 3-5-е разряды шинного формирователя.

Шинный формирователь 15 служит для формирования на шине данных кода (11111111)2 при проведении контроля зна- чения сигнала HOLD в конце каждого теста, если сигнал HOLD высокого уровня и кода (ОООООООО)а и если сигнал HOLD низкого уровня.

Буферный регистр 16 данных служит для перевода шины данных в состояние высокого импеданса при появлении на прямом выходе триггера 10 сигнала высокого уровня.

Кроме того, он обеспечивает изменение направления передача данных по шине данных в соответствии с управляющими сигналами микропроцессора

Буферный регистр 17 адреса служит для перевода шины адреса в состояние высоко- го импеданса при появлении на прямом выходе триггера 10 устройства сигнала высокого уровня.

Элемент И 18 служит для формирования сигнала Сброс путем коммутации единич- ного значения сигнала с выхода счетчика 7 и инверсного значения сигнала HOLD на входе 47 устройства.

Элемент И 19 служит для обнаружения начала машинного цикла М1 путем анализа поступающих на его входы сигналов SINC, D5, 56.

Элемент И 21 служит для коммутации сигналов прямого выхода триггера 9 и сигнала INTA с выхода системного контроллера 2 и выдачи сигнала на управляющий вход шинного формирователя 14

Элемент И 20 служит для формирования сигнала на счетном входе счетчика 7 по сигналу DBIN на выходе 42 микропроцессора в процессе выборки кода команды RETURN,

Элемент И 22 служит для выдачи на I- вход триггера 11 единичного сигнала только при единичном значении сигнала INTE микропроцессора и сигнала INT.

Элемент И 23 служит для коммутации сигналов HOLD, INTE, SINC и инверсного значения сигнала с прямого выхода триггера 11 и выдачи их на вход триггера 9.

Элемент И 24 служит для формирования единичного сигнала на входе HOLD микропроцессора при нулевом значении сигнала INTE с его выхода и наличии внешнего сигнала HOLD на входе 47 устройства,

Элемент И 25 служит для формирования сигнала запроса прерывания INT от устройства контроля путем коммутации сигналов с прямого выхода триггера 9 и инверсного выхода триггера 10.

Элемент НЕ 26 служит для выдачи на вход Т выбора направления передачи буферного регистра 16даншых инвертированного значения сигнала WR для управления буферным регистром 16 данных.

Элемент ИЛИ 27 служит для организации профилактического контроля с помощью сигнала Пуск с входа 48 устройства,

Элемент ИЛИ 28 служит для формирования сигнала I NT путем логического суммирования значения сигнала INT от внешних устройств и сигнала INT, сформированного устройством контроля.

Элемент ИЛИ 29 служит для организации установки триггера 11 в О как по сигналу INTE 0 с входа 40 микропроцессора, так и по сигналу высокого уровня с входа 46 устройства.

Элемент ИЛИ 30 служит для выдачи на выход устройства сигнала HLDA, сформированного как устройством контроля, так и самим микропроцессором,

Элемент ИЛИ 31 служит для запрета выдачи сигнала низкого уровня сигнала INTA на выход устройства в режиме контроля.

Элемент ИЛИ 32 служит для организации установки в О триггеров 9, 10 и 12 и счетчика 7 как по сигналу окончания тестового контроля, так и по единичному сигналу на входе 46 устройства.

Группа элементов ИЛИ 33.1 ... 33.4 служит для запрета выдачи управляющих сиг- налов низкого уровня RD, WR, RD10 на группу выходов 63 устройста при наличии нулевого значения сигнала на инверсном выходе триггера 10.

Рассмотрим назначение элементов бло- ка 13 сравнения (фиг. 3)

Блок 66 памяти эталонов является постоянным ЗУ и служит для хранения эталонных значений результата выполнения каждого теста микропроцессора (отклика на тест), а также для выдачи этих эталонных значений на вхемы сравнения при подаче на адресные выходы блока номера соответствующего теста.

Схема 67 сравнения служит для сравнения фактических результатов контроля с эталонными значениями.

Триггер 68 служит для фиксации ошибки при тестировании и выдаче сигнала об ошибке на выход устройства.

Элемент И 69 служит для формирования сигнала об окончании выполнения всех тестов (с нулевого по седьмой) и начала нового цикла выполнения тестов. Этот сигнал может использоваться для оповещения оператора, контролирующего работу системы

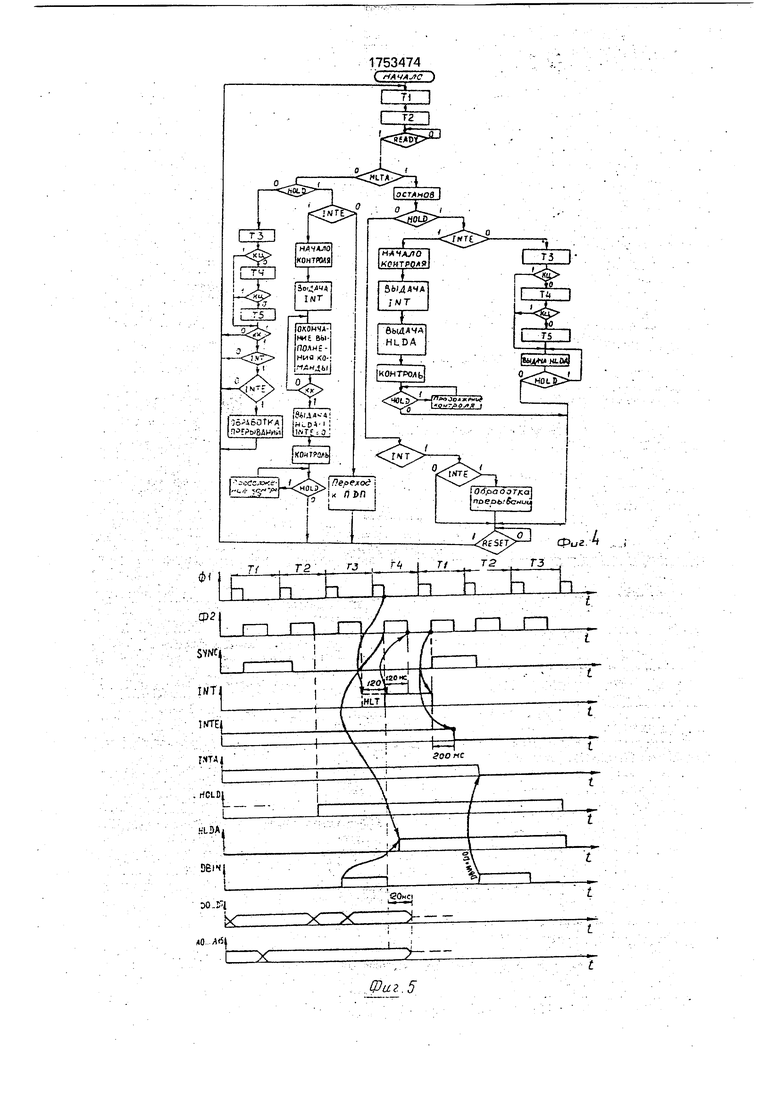

Рассмотрим работу предлагаемого устройства.

Устройство может работать в двух режимах.

Первый режим - контроль без остановки функционирования микропроцессорной системы, осуществляемой в моменты ее работы в режиме прямого доступа в память и инициируемый сигналом HOLD на входе 47, поступающим от контроллера прямого доступа к памяти,

Второй режим - профилактический контроль, для проведения которого требуется приостановка работы системы. Этот режим инициирцется подачей сигнала на вход 48 Пуск от таймера или от пульта оператора.

Рассмотрим работу устройства в первом режиме - режиме контроля в процессе функционирования.

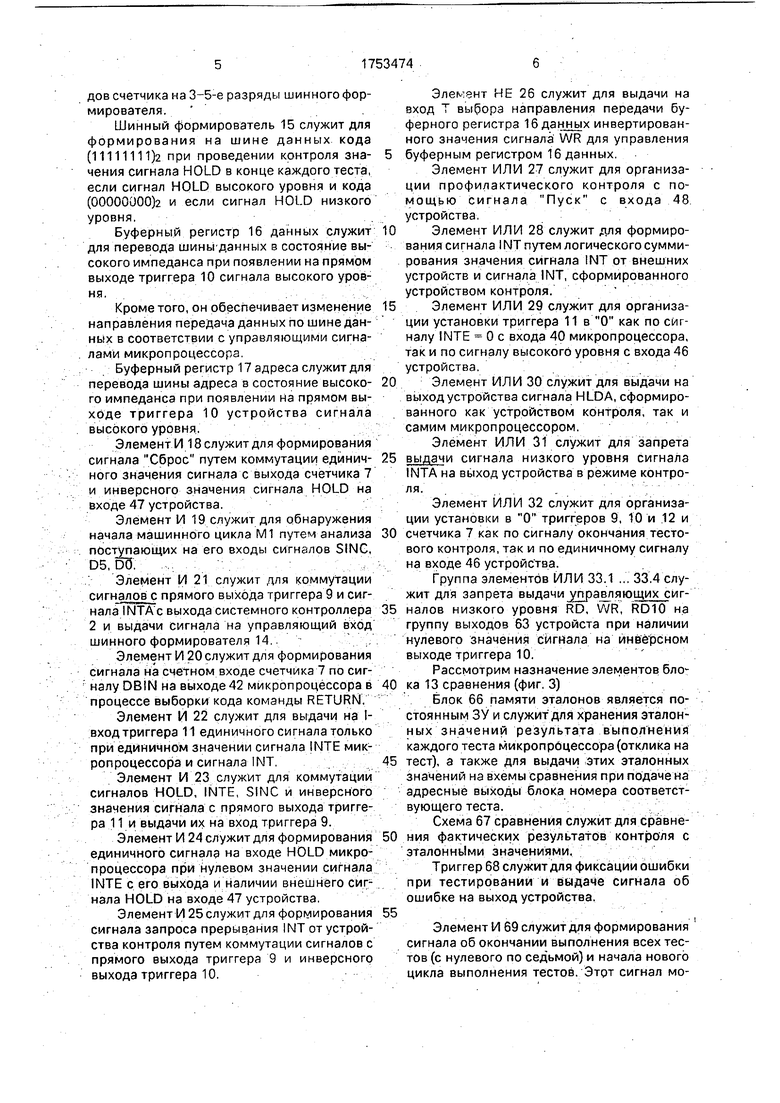

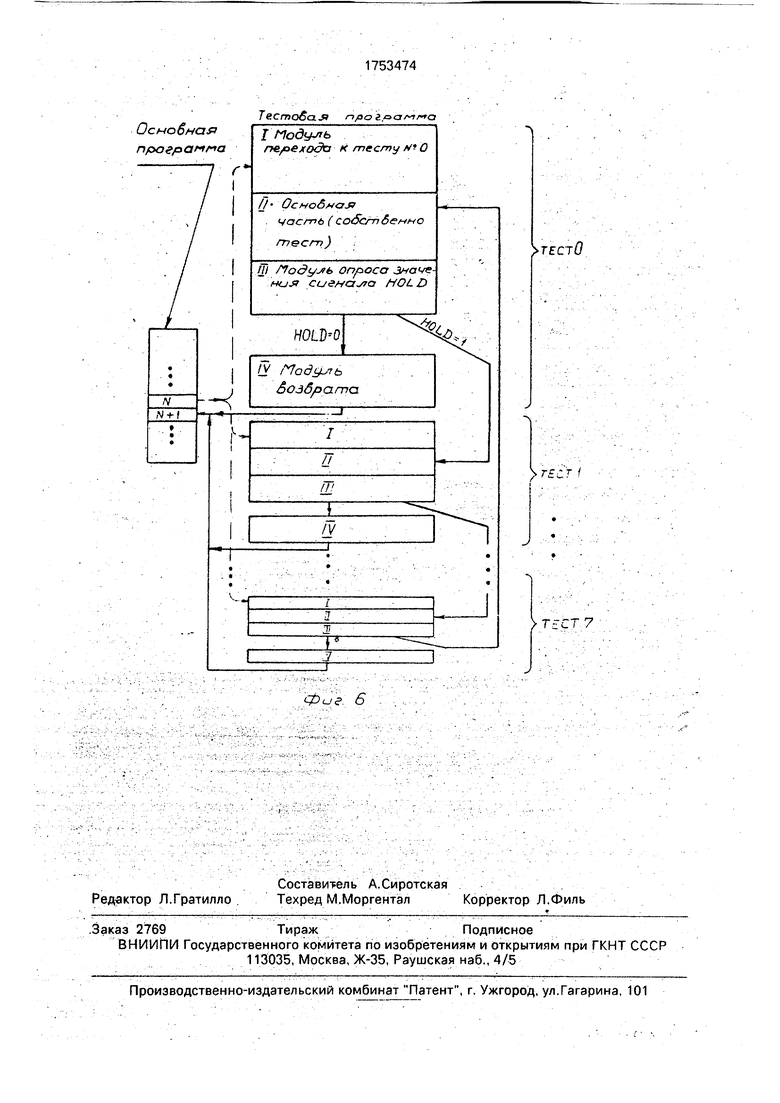

После подачи на вход 46 устройства сигнала RESET начальной установки (высокого уровня) длительностью не менее трех периодов тактовой частоты микропроцессор 1 устанавливается в исходное состояние. По этому сигналу триггера 9-12 и счетчики 7 и 8 устанавливаются в нулевое состояние, информационные выходы ПЗУ 5 и ПЗУ 6 переходят в состояние высокого импеданса, буферные регистры данных 16 и адреса 17 готовы к передаче информации, выходы шинных формирователей 14 и 15 переведены в высокоимпедансное состояние. Микропроцессор переходит к выполнению команд рабочей программы. Коды этих команд хранятся в системном ПЗУ, подключенном к системным шинам 63-65. При отсутствии сигнала HOLD на входе 47 его работа не отличается от обычной (фиг. 4). В первом такте Т1) микропроцессор выдает на шину 36 адреса адрес ячейки памяти системного ПЗУ, в которой хранится код команды, а на шину 37 данных выдает слово состояния, которое дешифруется в системном контроллере 2.

В такте Т2 анализируются состояния сигналов на входе микропроцессора READY (не показан), на входе 47 устройства сигналов HOLD, а также значение разряда D3 слова состояния (значение сигнала HLTA (подтверждение останова).

Если сигнал READY 0 (фиг. 4), то микропроцессор переходит в состояние ожидания и находится в нем до тех пор, пока на вход READY не поступит сигнал высокого уровня. Если READY 1 и сигнал HLTA 1, то микропроцессор переходит в состояние останова. В этом состоянии микропроцессор может выполнять циклы прерывания и

циклы захвата, но выйти из состояния останова он может лишь по сигналу Сброс, поступающему на вход 46 устройства.

Если сигналы READY и HLTA имеют значения соответственно 1 и 0, то анализируется значение сигнала HOLD (Захват) на входе 47 устройства. Если сигнал HOLD - низкого уровня, то микропроцессор переходит к такту ТЗ ваыполнения команды.

Efv« сигнал HOLD высокого уровня, то

в зависимости от значения сигнала INTE на выходе 0 микропроцессора последний переходит в режим захвата (INTE 0, элемент И 24 открыт и на вход 44 микропроцессора

поступает единичный сигнал) или в режим контроля (INTE 1, элемент И 24 закрыт).

Для того, чтобы не нарушать логику работы микропроцессорной системы при переходе к режиму контроля, необходимо

выдать для внешних устройств сигналы, соответствующие режиму Захват микропроцессора, а также перевести в состояние высокого импеданса шину адреса и шину данных, а шину управления перевести в состояние высокого уровня. Это происходит следующим образом.

При INTE 1 по сигналам HOLD и SINC единичный сигнал через элемент И 23 подается на вход установки в 1 триггера 9 и по

импульсу Ф2, поступающему с входа 50 устройства на вход синхронизации триггера 9, переводит его в единичное состояние.

Единичный сигнал с прямого выхода триггера 9 через открытый единичным сигналом с инверсного выхода триггера 10 элемент И 25, через элемент ИЛИ 28 и открытый сигналом INTE с выхода 40 микропроцессора элемент И 22 поступает на вход установки в 1 триггера 11, который по заднему фронту импульса Ф1 с входа 49 устройства устанавливается в единичное состояние.

Кроме того, сигнал с прямого выхода триггера 9 поступает на вход элемента ИЛИ

31, запрещая тем самым выдачу сигнала внешним устройствам. Сигнал с прямого выхода триггера 11 поступает на вход 45 микропроцессора, который идентифицирует его как сигнал INT - Запрос прерывания, а

сам продолжает выполнение текущей команды, так как значение сигнала на входе анализируется им после окончания выполнения текущей команды. Если текущая команда окончена, то микропроцессор

переходит с такта Т1 к выполнению машинного цикла М8 - Прерывание. При этом в такте Т1 сигнал INTE с выхода 40 микропроцессора равен О и микропроцессор выдает по шине данных сигнал состояния INTA

Подтверждение прерывания (разряд DO 1 слова - состояния).

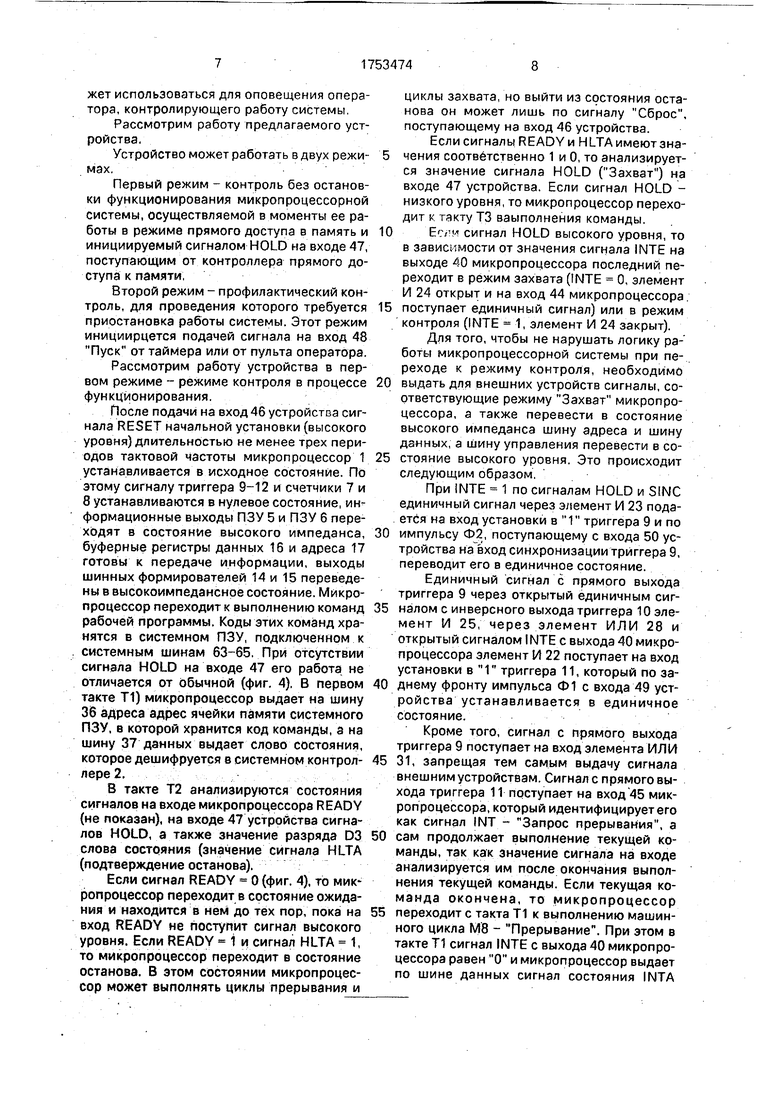

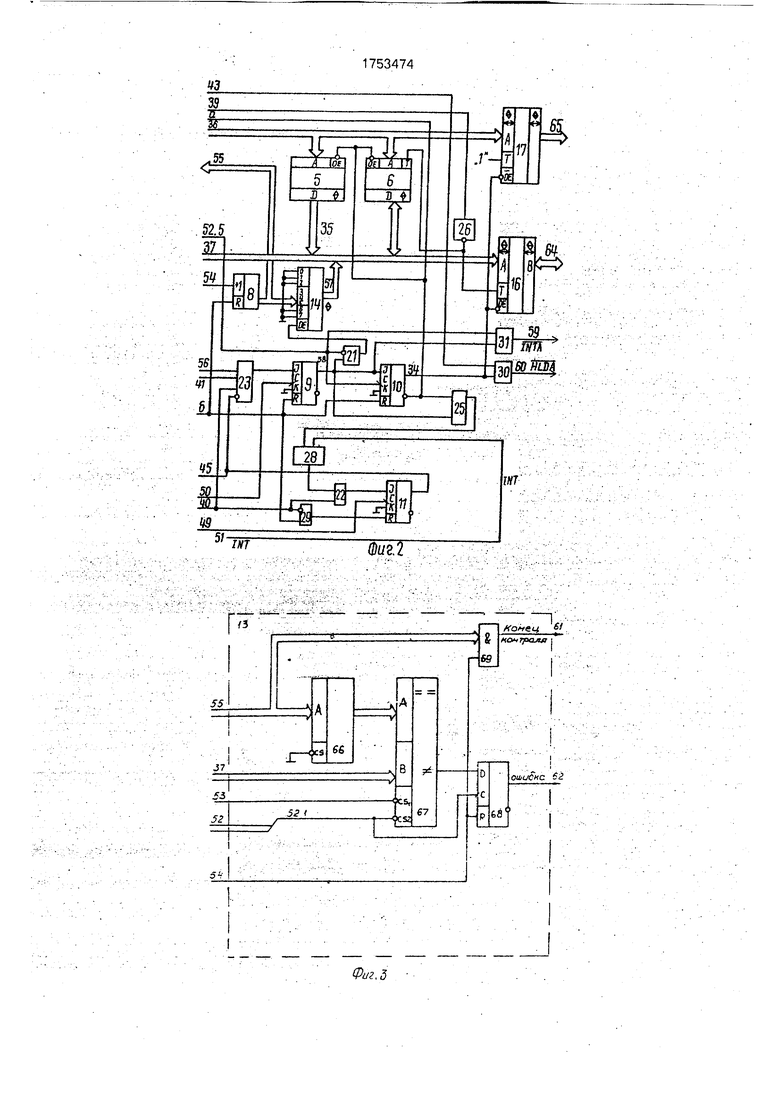

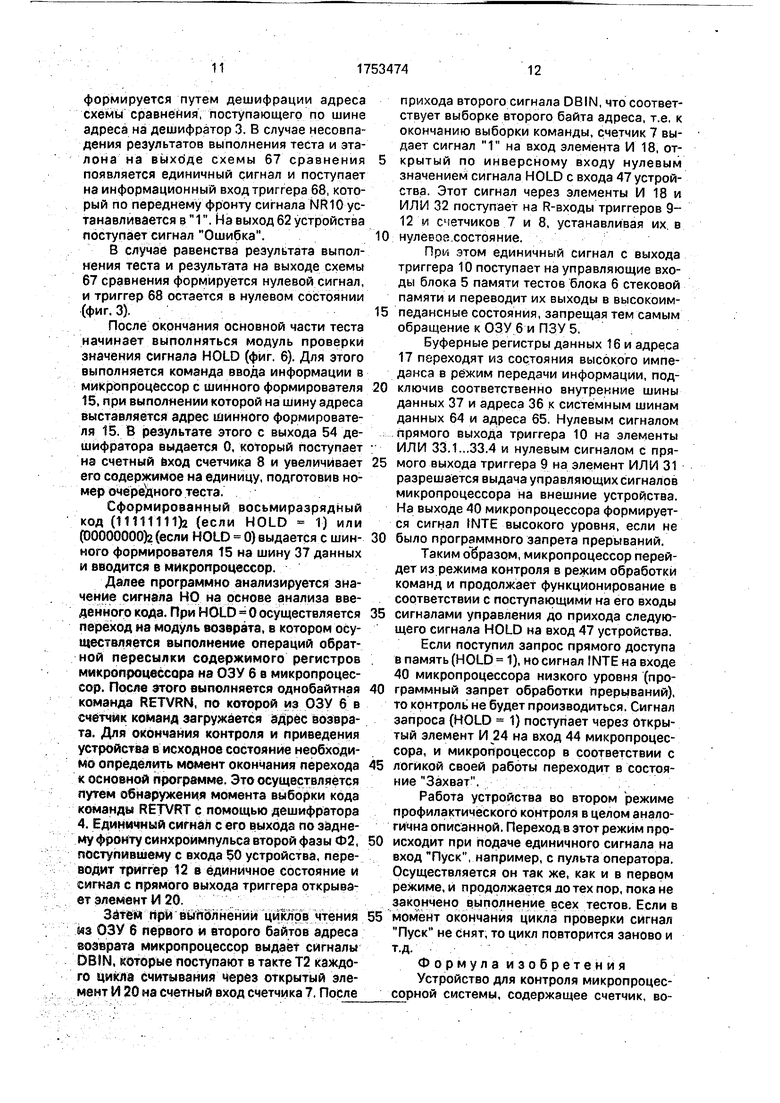

Этот сигнал используется для разрешения выдачи на шину данных команды и адреса перехода на подпрограмму прерывания. Подпрограмма прерывания в данном случае представляет собой набор функциональных тестовых программ (тест О...тест 7), каждая из которых имеет в своем составе модуль перехода, модуль собственного теста, модуль опроса сигнала HOLD и модуль возврата (фиг. 6).

Модули перехода (возврата) содержит команды пересылки данных из регистров в стек (или обратно) и предназначены для сохранения содержимого регистров микропроцессора в стеке, роль которого выполняет блок 6 стековой памяти. Модуль опроса сигнала предназначен для определения значения сигнала НО на входе 47 устройства. В зависимости от того, равен он О или 1, осуществляется соответственно либо возврат к основной программе (HOLD 0), либо выполнение следующей тестовой программы (при HOLD 1).

Если при HOLD 1 успевают выполниться все 8 тестовых программ и после этого значение сигнала HOLD равно 0, то осуществляется возврат к основной программе.

В конце каждого теста производится программный вывод результата из микропроцессора в блок сравнения, где происходит сравнение результата контроля с эталонным значением на вхеме 67 сравнения (фиг. 3).

Рассмотрим более подробно переход к тестовой программе, начиная с первого такта работы микропроцессора в режиме Прерывание.

Сигнал INTA с выхода 52,5 системного контроллера 2 поступает на инверсный вход элемента И 24, и единичный сигнал с выхода этого элемента (триггер 9 находится в единичном состоянии) поступает на вход управления шинного формирователя 14, разрешая тем самым выдачу на шину данных кода (00 NNN 000)2 со счетчика 8. Трехразрядное поле NNM обеспечивает возможность формирования начальных адресов для восьми различных программ RSTNNN обслуживания прерываний (тестовых программ).

Например, для нулевой тестовой программы в поле будет записан код (000)2. Сигнал INTA поступает также на вход синхронизации триггера 10, который по заднему фронту сигнала INTA сигналом с прямого выхода триггера 9 переводится в единичное состояние. Единичный сигнал с прямого выхода триггера 10 подается через элемент ИЛИ 30 на выход 60 устройства в качестве сигнала подтверждения захвата для контроллера прямого доступа к памяти. Этот сигнал разрешает контроллеру начать прямой доступ.

Кроме того, сигнал с прямого выхода триггера 10 подается на управляющие входы буферного регистра 16 данных и буфер0 ного регистра 17 адреса дня перевода системных шин данных 64 и адреса 56 в высокоимпедансное состояние, а также на входы элементов ИЛИ 33.1....33.4 для перевода шины 52 управления в состояние высо5 кого уровня и запрета. Таким образом, выдачи сигналов управления в эту шину Этот же сигнал поступает на второй управляющий вход дешифратора 3. Таким образом, микропроцессор будет подготовлен к

0 проведению контроля без нарушения логики его работы в режиме Захват, так как для внешних устройств были выданы сигналы подтверждения прямого доступа к памяти, а шины управления, адреса и данных

5 отключены от системных шин,

Одновременно с инверсного выхода триггера 10 нулевой сигнал подается на управляющие входы блока 5 памяти тестов и блока б стековой памяти и разрешает их

0 работу.

По сигналу I NT содержимое счетчика команд микропроцессора записывается в блок 6 стековой памяти, что происходит следующим образом. С помощью кода (00 NNN

5 000)2, сформированного счетчиком 8 и поступившего в такте Т1 через шину данных в микропроцессор, в счетчике команд формируется шестнадцатиразрядный адрес (000 000 000 NNN 000)2. Этот адрес является ад0 ресом первой команды очередной тестовой программы.

По этому адресу начинается выборка из ПЗУ 5 и выполнение команд тестовой программы, началом которой является модуль

5 перехода (фиг. б).

Этот модуль содержит команды, обеспечивающие программную перезапись содержимого регистров микропроцессора в блок 6 стековой памяти. Далее выполняется

0 основная часть теста, результат выполнения которой должен быть выведен через шину 37 данных в блок 13 сравнения.

В этом блоке этот результат сравнивается с эталоном, который хранится в ПЗУ 66

5 блока 13, Сравнение происходит по сигналу записи NR10, поступающему с выхода 51.1 системного контроллера 2 на вход CS 2 схемы 67 сравнения при наличии разрешающего сигнала с выхода 53 дешифратора 3. Сигнал 1 на выходе 53 дешифратора 3

формируется путем дешифрации адреса схемы сравнения, поступающего по шине адреса на дешифратор 3. В случае несовпадения результатов выполнения теста и эталона на выхо де схемы 67 сравнения появляется единичный сигнал и поступает на информационный вход триггера 68, который по переднему фронту сигнала NR10 устанавливается в 1. На выход 62 устройства поступает сигнал Ошибка.

В случае равенства результата выполнения теста и результата на выходе схемы 67 сравнения формируется нулевой сигнал, и триггер 68 остается в нулевом состоянии (фиг. 3).

После окончания основной части теста начинает выполняться модуль проверки значения сигнала HOLD (фиг. 6). Для этого выполняется команда ввода информации в микропроцессор с шинного формирователя 15, при выполнении которой на шину адреса выставляется адрес шинного формирователя 15. В результате этого с выхода 54 дешифратора выдается 0, который поступает на счетный вход счетчика 8 и увеличивает его содержимое на единицу, подготовив номер очередного теста.

Сформированный восьмиразрядный код (11111111)2 (если HOLD 1} или (00000000)2 (если HOLD 0) выдается с шин- кого формирователя 15 на шину 37 данных и вводится в микропроцессор.

Далее программно анализируется значение сигнала НО на основе анализа введенного кода. При HOLD 0 осуществляется переход на модуль возврата, в котором осуществляется выполнение операций обратной пересылки содержимого регистров микропроцессора на ОЗУ 6 в микропроцессор. После этого выполняется однобайтная команда RETVRN, по которой из ОЗУ 6 в счетчик команд загружается адрес возврата. Для окончания контроля и приведения устройства в исходное состояние необходимо определить момент окончания перехода к основной программе. Эта осуществляется путем обнаружения момента выборки кода команды RETVRT с помощью дешифратора 4. Единичный сигнал с его выхода по заднему фронту синхроимпульса второй фазы Ф2, поступившему с входа 50 устройства, переводит триггер 12 в единичное состояние и сигнал с прямого выхода триггера открывает элемент И 20.

Затем при выполнении циклов чтения из ОЗУ 6 первого и второго байтов адреса возврата микропроцессор выдает сигналы DBIN, которые поступают в такте Т2 каждого цикла считывания через открытый элемент И 20 на счетный вход счетчика 7. После

прихода второго сигнала DBIN, что соответствует выборке второго байта адреса, т.е. к окончанию выборки команды, счетчик 7 выдает сигнал 1 на вход элемента И 18, открытый по инверсному входу нулевым значением сигнала HOLD с входа 47 устройства. Этот сигнал через элементы И 18 и ИЛИ 32 поступает на R-входы триггеров 9- 12 и счетчиков 7 и 8, устанавливая их в нулевое состояние.

При этом единичный сигнал с выхода триггера 10 поступает на управляющие входы блока 5 памяти тестов блока 6 стековой памяти и переводит их выходы в высокоим- педансные состояния, запрещая тем самым обращение к ОЗУ 6 и ПЗУ 5.

Буферные регистры данных 16 и адреса 17 переходят из состояния высокого импеданса в режим передачи информации, подключив соответственно внутренние шины данных 37 и адреса 36 к системным шинам данных 64 и адреса 65, Нулевым сигналом прямого выхода триггера 10 на элементы ИЛИ 33.1...33.4 и нулевым сигналом с прямого выхода триггера 9 на элемент ИЛИ 31 разрешается выдача управляющих сигналов микропроцессора на внешние устройства. На выходе 40 микропроцессора формируется сигнал INTE высокого уровня, если не было программного запрета прерываний.

Таким образом, микропроцессор перейдет из режима контроля в режим обработки команд и продолжает функционирование в соответствии с поступающими на его входы сигналами управления до прихода следующего сигнала HOLD на вход 47 устройства.

Если поступил запрос прямого доступа в память (HOLD 1), но сигнал INTE на входе 40 микропроцессора низкого уровня (программный запрет обработки прерываний), то контроль не будет производиться. Сигнал запроса (HOLD 1) поступает через открытый элемент И 24 на вход 44 микропроцессора, и микропроцессор в соответствии с логикой своей работы переходит в состояние Захват.

Работа устройства во втором режиме профилактического контроля в целом аналогична описанной. Переход в этот режим происходит при подаче единичного сигнала на вход Пуск, например, с пульта оператора. Осуществляется он так же, как и в первом режиме, и продолжается до тех пор, пока не закончено выполнение всех тестов. Если в момент окончания цикла проверки сигнал Пуск не снят, то цикл повторится заново и т.д.

Формула изобретения

Устройство для контроля микропроцессорной системы, содержащее счетчик, восемь элементов И, первый триггер, три элемента ИЛИ, блок сравнения, блок памяти тестов, причем прямой выход первого триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, выход сигнала синхронизации контролируемого микропроцессора подключен к первому входу второго элемента И, выход сигнала разрешения прерывания контролируемого процессора соединен с первым инверсным входом третьего элемента И, вход начальной установки устройства соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом сброса второго счетчика, выход четвертого элемента И соединен с первым входом второго элемента ИЛИ, вход запроса захвата устройства соединен с первым входом третьего элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей и уменьшения времени простоя при проведении контроля, введены дополнительно системный контроллер, два дешифратора, блок стековой памяти, второй, третий и четвертый триггеры, два шины формирователя, беферный регистр данных, буферный регистр адреса, элемент НЕ, четвертый, пятый, шестой элементы ИЛИ, группа элементов ИЛИ, выходы которой со- единены в шину управления, которая является первой группой выходов устройства третий вход устройства является входом подачи команды Пуск иеоединен с вторым входом третьего элемента ИЛИ, выход кото- рого соединен с первым инверсным входом Пятого элемента И, с группой информационных входов первого шинного формирователя, с первым входом шестого элемента И с вторым входом третьего элемента И, выход которого соединен с входом запроса захвата контролируемого микропроцессора, первый синхровход устройства соединен с входом синхронизации первого триггера и с первым входом синхронизации контролиру- емого микропроцессора, второй вход синхронизации устройства соединен с входом синхронизации контролируемого микропроцессора и с входами синхронизации второго и третьего триггера, прямой выход третьего триггера соединен с первым входом четвертого элемента И, с входом установки четвертого триггера, с первым входом седьмого элемента И и первым входом четвертого элемента ИЛИ, вход сигнала запро- са прерывания от внешних источников устройства соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом восьмого элемента И, выход сигнала синхронизации контролируемого микропроцессора соединен с вторым входом системного контроллера; выход разрешения прерывания контролируемого микропроцессора соединен также с третьим входом шестого элемента И, с первым инверсным входом пятого элемента ИЛИ и с вторым входом восьмого элемента И, выход которого соединен с входом установки второго триггера, выход пятого элемента И соединен с вторым входом первого элемента ИЛИ, выход которого соединен также входами сброса первого счетчика, первого, третьего, четвертого триггеров, а также с вторым входом пятого элемента ИЛИ, выход пятого элемента ИЛИ подключен к входу сброса второго триггера, прямой выход которого соединен с входом запроса прерывания контролируемого микропроцессора и с четвертым инверсным входом шестого элемента И, выход шестого элемента И подключен к входу установки третьего триггера, выход разрешения приема информации контролируемого микропроцессора соединен с вторым входом первого элемента И и с одноименным входом системного контроллера, выход подтверждения состояния захвата контролируемого микропроцессора соединен с одноименным входом шестого элемента ИЛИ, выход которого является одноименным выходом для подключения к од- ноименному входу контролируемого микропроцессора устройства, выход разрешения выдачи информации контролируемого микропроцессора соединен с одноименным входом системного контроллера и через элемент НЕ соединен с входами выбора направления передачи блока стековой памяти и буферного регистра данных, адресная группа выходов контролируемого микропроцессора соединена с группой информационных входов первого дешифратора, с адресной группой входов блоков памяти тестов и блока стековой памяти, а также с группой информационных входов буферного регистра адреса, выходы которого образуют группу адресных выходов устройства, группа выходов шины дан- ных контролируемого процессора соединена с информационной группой входов второго дешифратора, а также соединена через одноименные входы системного контроллера с первой группой информационных входов блока сравнения и группой информационных входов блока стековой памяти, с группой информационных входов первого и второго шинных формирователей и блока памяти тестов, а также с группой информационных входов буферного регистра данных, группа выходов которого является группой выходов шины данных

устройства, первый и второй выходы разрядов которого соединены соответственно с вторым и третьим инверсным входами второго элемента И, выход которого соединен с первым управляющим входом второго дешифратора, группа управляющих выходов системного контроллера соединена с второй группой информационных входов блока сравнения, а выходы сигналов записи ввода/вывода, записи в память, чтения из памяти группы управляющих выходов системного контроллера соединены с первыми входами первого, второго, третьего элементов ИЛИ группы элементов ИЛИ соответственно, выход сигнала чтения ввода/вывода группы управляющих выходов системного контроллера соединен с первым инверсным управляющим входом первого дешифратора и первым входом четвертого элемента ИЛИ группы элементов ИЛИ, выход сигнала подтверждения запроса прерывания группы управляющих выходов системного контроллера соединен с вторым инверсным входом седьмого элемента И, входом синхонизации четвертого триггера и с вторым входом четвертого элемента ИЛИ, выход которого является одноименным выходом устройства, выход седьмого элемента И соединен с входом управления перевода выходов второго шинного формирователя в высокоимпедансное состояние, инверсный выход четвертого триггера соединен с вторым входом четвертого элемента И, с входами управления перевода в состояние высокого импеданса информационных выходов блока памяти тестов и блока стековой памяти, с инверсными входами первого, второго, третьего и четвертого элементов

ИЛИ группы элементов ИЛИ, с вторым и инверсным входом управления первого и второго дешифраторов, первый инверсный выход первого дешифратора соединен с

входом управления перевода первого шинного формирователя в состояние высокого импеданса, со счетным входом второго счетчика, с входом синхронизации блока сравнения, второй выход первого дешифратора

соединен с входом разрешения блока сравнения, группа разрядных выходов второго счетчика соединена с группой информационных входов второго шинного формирователя и с третьей группой входов разрешения

поразрядного сравнения блока сравнения, выходы +Равно и Не равно которого являются соответственно выходами ошибки устройства, прямой выход четвертого триг: гера соединен с вторым входом шестого

элемента ИЛИ, а также с входами управления перевода в высокоимпедансное состоя ние буферного регистра адреса и регистра данных, выход второго дешифратора соединен с 1-входом первого триггера, разрядный

выход первого счетчика соединен с вторым входом пятого элемента И, вторая группа информационных входов второго шинного формирователя подключена к шине логического нуля устройства, на К-е входы первого,

второго, третьего, четвертого триггеров поданы сигналы логического нуля устройства, вход выбора направления передачи буферного регистра адреса подключен к шине логической единицы устройства, вход начальной установки устройства соединен с входом начальной установки контролируемого микропроцессора.

а/г/

t

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

J5

рГГГТГ

45

5/

.

s

W7

Фиг 2

ф

Ф2

HCLDI

D6I4

ЭО-Р1

40 ЛЙ

а %

СОмС

J.

Фиг 5

Тестобал npoioar r a

I Модуль

ле/оехода к тесту л О

// OcHo6 ctJ

часть ( ccx5cm6e/-tHO

тест)

П1 Модуль опроса jYcrve r-Kjjr сиенала HOLD

HOLfrO

/V

N-H

Фиг 6

ГЕСТО

rЈjT /

ТГСТ7

Авторы

Даты

1992-08-07—Публикация

1990-05-18—Подача