Изобретение относится к накоплению информации, а именно к устройствам для воспроизведения цифровой магнитной записи. Целью изобретения является снижение погрешности воспроизведения за счет уменьшения межсимвольных помех.

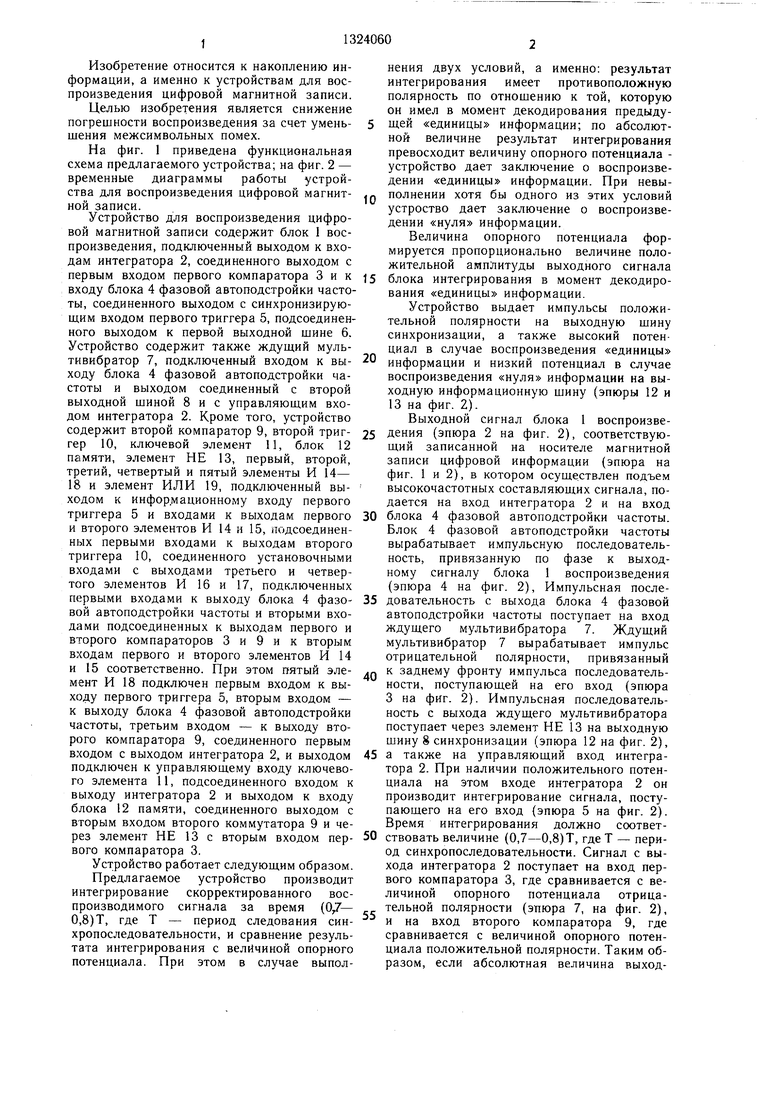

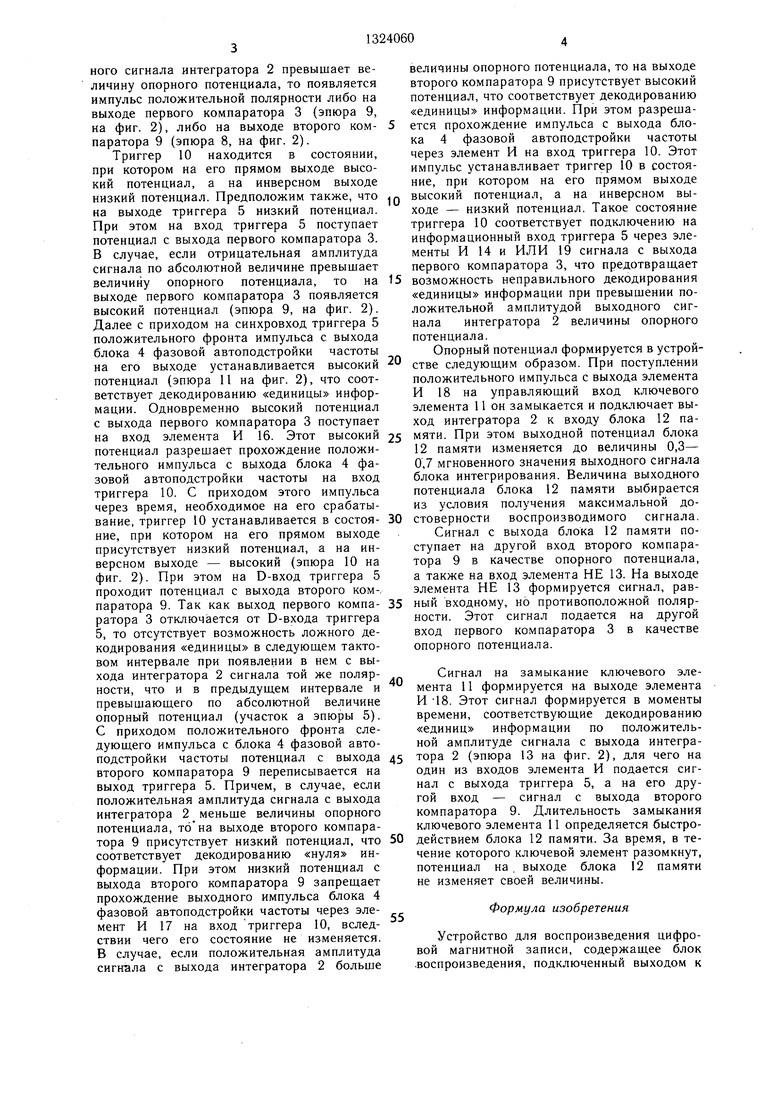

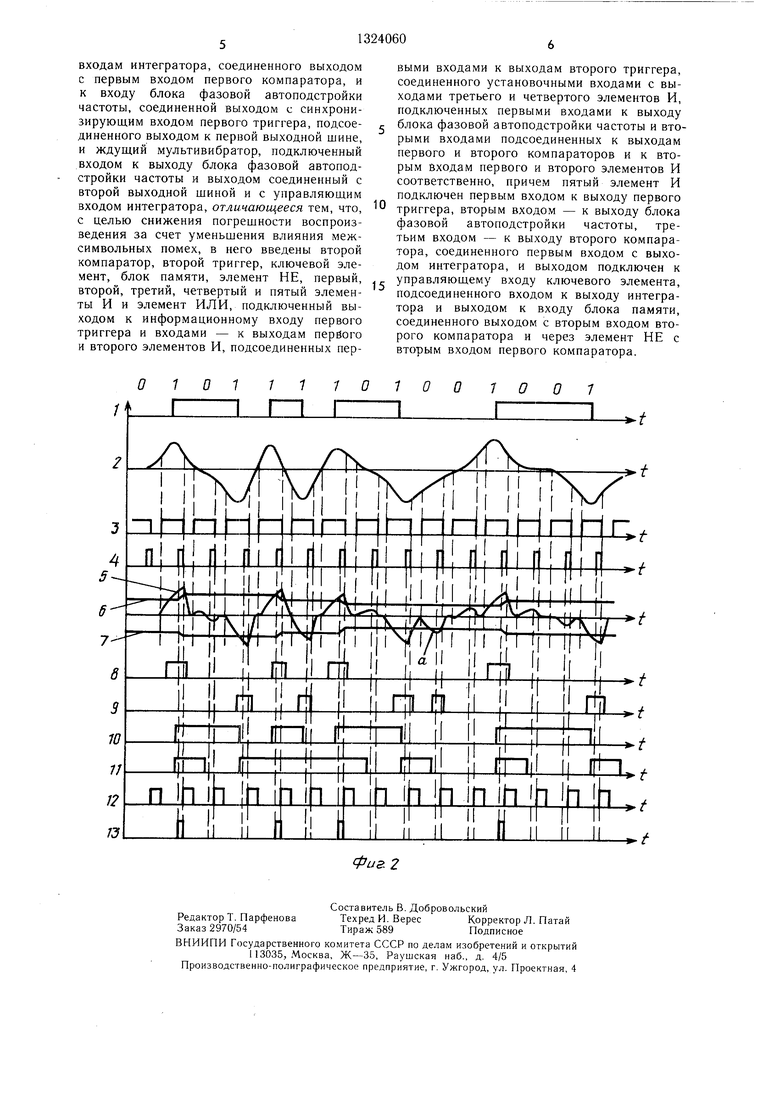

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства для воспроизведения цифровой магнитной записи.

Устройство для воспроизведения цифровой магнитной записи содержит блок 1 воспроизведения, подключенный выходом к входам интегратора 2, соединенного выходом с первым входом первого компаратора 3 и к входу блока 4 фазовой автоподстройки частоты, соединенного выходом с синхронизирую- шим входом первого триггера 5, подсоединенного выходом к первой выходной шине 6. Устройство содержит также ждущий мультивибратор 7, подключенный входом к выходу блока 4 фазовой автоподстройки частоты и выходом соединенный с второй выходной шиной 8 и с управляющим входом интегратора 2. Кроме того, устройство содержит второй компаратор 9, второй триггер 10, ключевой элемент 11, блок 12 памяти, элемент НЕ 13, первый, второй, третий, четвертый и пятый элементы И 14- 18 и элемент ИЛИ 19, подключенный выходом к информационному входу первого триггера 5 и входами к выходам первого и второго элементов И 14 и 15, подсоединенных первыми входами к выходам второго триггера 10, соединенного установочными входами с выходами третьего и четвертого элементов И 16 и 17, подключенных первыми входами к выходу блока 4 фазовой автоподстройки частоты и вторыми входами подсоединенных к выходам первого и второго компараторов 3 и 9 и к вторым входам первого и второго элементов И 14 и 15 соответственно. При этом пятый элемент И 18 подключен первым входом к выходу первого триггера 5, вторым входом - к выходу блока 4 фазовой автоподстройки частоты, третьим входом - к выходу второго компаратора 9, соединенного первым входом с выходом интегратора 2, и выходом подключен к управляющему входу ключевого элемента 11, подсоединенного входом к выходу интегратора 2 и выходом к входу блока 12 памяти, соединенного выходом с вторым входом второго коммутатора 9 и через элемент НЕ 13 с вторым входом первого компаратора 3.

Устройство работает следующим образом. Предлагаемое устройство производит интегрирование скорректированного воспроизводимого сигнала за время (О/- 0,8) Т, где Т - период следования син- хропоследовательности, и сравнение результата интегрирования с величиной опорного потенциала. При этом в случае выполнения двух условий, а именно: результат интегрирования имеет противоположную полярность по отношению к той, которую он имел в момент декодирования предыдущей «единицы информации; по абсолютной величине результат интегрирования превосходит величину опорного потенциала - устройство дает заключение о воспроизведении «единицы информации. При невыQ полнении хотя бы одного из этих условий устроство дает заключение о воспроизведении «нуля информации.

Величина опорного потенциала формируется пропорционально величине положительной амплитуды выходного сигнала

5 блока интегрирования в момент декодирования «единицы информации.

Устройство выдает импульсы положительной полярности на выходную шину синхронизации, а также высокий потенциал в случае воспроизведения «единицы

информации и низкий потенциал в случае воспроизведения «нуля информации на выходную информационную шину (эпюры 12 и 13 на фиг. 2).

Выходной сигнал блока 1 воспроизве5 дения (эпюра 2 на фиг. 2), соответствующий записанной на носителе магнитной записи цифровой информации (эпюра на фиг. 1 и 2), в котором осуще.ствлен подъем высокочастотных составляющих сигнала, подается на вход интегратора 2 и на вход

0 блока 4 фазовой автоподстройки частоты. Блок 4 фазовой автоподстройки частоты вырабатывает импульсную последовательность, привязанную по фазе к выходному сигналу блока 1 воспроизведения (эпюра 4 на фиг. 2), Импульсная после5 довательность с выхода блока 4 фазовой автоподстройки частоты поступает на вход ждущего мультивибратора 7. Ждущий мультивибратор 7 вырабатывает импульс отрицательной полярности, привязанный Q К заднему фронту импульса последовательности, поступающей на его вход (эпюра 3 на фиг. 2). Импульсная последовательность с выхода ждущего мультивибратора поступает через элемент НЕ 13 на выходную шину 8 синхронизации (эпюра 12 на фиг. 2),

5 а также на управляющий вход интегратора 2. При наличии положительного потенциала на этом входе интегратора 2 он производит интегрирование сигнала, поступающего на его вход (эпюра 5 на фиг. 2). Время интегрирования должно соответ0 ствовать величине (0,7-0,8) Т, где Т - период синхропоследовательности. Сигнал с выхода интегратора 2 поступает на вход первого компаратора 3, где сравнивается с величиной опорного потенциала отрицательной полярности (эпюра 7, на фиг. 2), и на вход второго компаратора 9, где сравнивается с величиной опорного потенциала положительной полярности. Таким образом, если абсолютная величина выход5

ного сигнала интегратора 2 превышает величину опорного потенциала, то появляется импульс положительной полярности либо на выходе первого компаратора 3 (эпюра 9, на фиг. 2), либо на выходе второго компаратора 9 (эпюра 8, на фиг. 2).

Триггер 10 находится в состоянии, при котором на его прямом выходе высокий потенциал, а на инверсном выходе низкий потенциал. Предположим также, что на выходе триггера 5 низкий потенциал. При этом на вход триггера 5 поступает потенциал с выхода первого компаратора 3. В случае, если отрицательная амплитуда сигнала по абсолютной величине превышает величину опорного потенциала, то на выходе первого компаратора 3 появляется высокий потенциал (эпюра 9, на фиг. 2). Далее с приходом на синхровход триггера 5 положительного фронта импульса с выхода блока 4 фазовой автоподстройки частоты на его выходе устанавливается высокий потенциал (эпюра 11 на фиг. 2), что соответствует декодированию «единицы информации. Одновременно высокий потенциал с выхода первого компаратора 3 поступает на вход элемента И 16. Этот высокий потенциал разрешает прохождение положительного импульса с выхода блока 4 фазовой автоподстройки частоты на вход триггера 10. С приходом этого импульса через время, необходимое на его срабатывание, триггер 10 устанавливается в состояние, при котором на его прямом выходе присутствует низкий потенциал, а на инверсном выходе - высокий (эпюра 10 на фиг. 2). При этом на D-вход триггера 5 проходит потенциал с выхода второго ком-, паратора 9. Так как выход первого компаратора 3 отключается от D-входа триггера 5, то отсутствует возможность ложного декодирования «единицы в следующем тактовом интервале при появлении в нем с выхода интегратора 2 сигнала той же полярности, что и в предыдуш.ем интервале и превышающего по абсолютной величине опорный потенциал (участок а эпюры 5). С приходом положительного фронта следующего импульса с блока 4 фазовой автоподстройки частоты потенциал с выхода второго компаратора 9 переписывается на выход триггера 5. Причем, в случае, если положительная амплитуда сигнала с выхода интегратора 2 меньше величины опорного потенциала, то на выходе второго компаратора 9 присутствует низкий потенциал, что соответствует декодированию «нуля информации. При этом низкий потенциал с выхода второго компаратора 9 запрещает прохождение выходного импульса блока 4 фазовой автоподстройки частоты через элемент И 17 на вход триггера 10, вслед- ствии чего его состояние не изменяется. В случае, если положительная амплитуда сигнала с выхода интегратора 2 больше

0

5

0

5

0

5

0

5

0

5

величины опорного потенциала, то на выходе второго компаратора 9 присутствует высокий потенциал, что соответствует декодированию «единицы информации. При этом разрешается прохождение импульса с выхода блока 4 фазовой автоподстройки частоты через элемент И на вход триггера 10. Этот импульс устанавливает триггер 10 в состояние, при котором на его прямом выходе высокий потенциал, а на инверсном выходе - низкий потенциал. Такое состояние триггера 10 соответствует подключению на информационный вход триггера 5 через элементы И 14 и ИЛИ 19 сигнала с выхода первого компаратора 3, что предотвращает возможность неправильного декодирования «единицы информации при превышении положительной амплитудой выходного сигнала интегратора 2 величины опорного потенциала.

Опорный потенциал формируется в устройстве следующим образом. При поступлении положительного импульса с выхода элемента И 18 на управляющий вход ключевого элемента 11 он замыкается и подключает выход интегратора 2 к входу блока 12 памяти. При этом выходной потенциал блока 12 памяти изменяется до величины 0,3- 0,7 мгновенного значения выходного сигнала блока интегрирования. Величина выходного потенциала блока 12 памяти выбирается из условия получения максимальной достоверности воспроизводимого сигнала.

Сигнал с выхода блока 12 памяти поступает на другой вход второго компаратора 9 в качестве опорного потенциала, а также на вход элемента НЕ 13. На выходе элемента НЕ 13 формируется сигнал, равный входному, но противоположной полярности. Этот сигнал подается на другой вход первого компаратора 3 в качестве опорного потенциала.

Сигнал на замыкание ключевого элемента 11 формируется на выходе элемента И -18. Этот сигнал формируется в моменты времени, соответствующие декодированию «единиц информации по положительной амплитуде сигнала с выхода интегратора 2 (эпюра 13 на фиг. 2), для чего на один из входов элемента И подается сигнал с выхода триггера 5, а на его другой вход - сигнал с выхода второго компаратора 9. Длительность замыкания ключевого элемента 11 определяется быстродействием блока 12 памяти. За время, в течение которого ключевой элемент разомкнут, потенциал на , выходе блока 12 памяти не изменяет своей величины.

Формула изобретения

Устройство для воспроизведения цифровой магнитной записи, содержащее блок .воспроизведения, подключенный выходом к

входам интегратора, соединенного выходом с первым входом первого компаратора, и к входу блока фазовой автоподстройки частоты, соединенной выходом с синхронизирующим входом первого триггера, подсоединенного выходом к первой выходной шине, и ждущий мультивибратор, подключенный входом к выходу блока фазовой автоподстройки частоты и выходом соединенный с второй выходной шиной и с управляющим входом интегратора, отличающееся тем, что, с целью снижения погрешности воспроизведения за счет уменьшения влияния межсимвольных помех, в него введены второй компаратор, второй триггер, ключевой элемент, блок памяти, элемент НЕ, первый, второй, третий, четвертый и пятый элементы И и элемент ИЛИ, подключенный выходом к информационному входу первого триггера и входами - к выходам первого и второго элементов И, подсоединенных пер0101 11 10100 Т001

Редактор Т. Парфенова Заказ 2970/54

Составитель В. Добровольский Техред И. ВересКорректор Л. Патай

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производствеино-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

выми входами к выходам второго триггера, соединенного установочными входами с выходами третьего и четвертого элементов И, подключенных первыми входами к выходу блока фазовой автоподстройки частоты и вторыми входами подсоединенных к выходам первого и второго компараторов и к вторым Входам первого и второго элементов И соответственно, причем пятый элемент И подключен первым входом к выходу первого триггера, вторым входом - к выходу блока фазовой автоподстройки частоты, третьим входом - к выходу второго компаратора, соединенного первым входом с выходом интегратора, и выходом подключен к управляющему входу ключевого элемента, подсоединенного входом к выходу интегратора и выходом к входу блока памяти, соединенного выходом с вторым входом второго компаратора и через элемент НЕ с вторым входом первого компаратора.

0

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| Устройство автоматической стабилизации скорости движения носителя магнитной записи | 1983 |

|

SU1115102A1 |

| Устройство для синхронизации воспроизведения цифровой информации | 1990 |

|

SU1764085A1 |

| СПОСОБ МАГНИТНОЙ ВИДЕОЗАПИСИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1989 |

|

RU2013023C1 |

| Устройство для счета движущихся объектов | 1985 |

|

SU1312623A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1989 |

|

SU1635278A1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

Изобретение относится к накоплению информации. Цель изобретения - снижение погрешности воспроизведения за счет уменьшения межсимвольных помех. Устройство содержит блок 1 воспроизведения, интегратор 2, компараторы 3 и 9, блок 4 фазовой автоподстройки частоты, триггеры 5 и 10, ждущий мультивибратор 7, ключевой элемент 11, блок 12 памяти, элемент НЕ 13, элементы И 14-18 и элемент ИЛИ 19. Введение новых элементов и образование новых связей между элементами устройства позволяет производить интегрирование скорректированного воспроизводимого сигнала за время (0,7-0,8) Т, где Т - период следования синхропоследовательности, и сравнение результата интегрирования с величиной опорного потенциала. Необходимо выполнение условий: результат интегрирования имеет противоположную полярность по отношению к той, которую он имел в момент декодирования предыдущей «единицы информации; по абсолютной величине результат интегрирования превосходит величину опорного потенциала. При невыполнении условий устройство дает заключение о воспроизведении «нуля информации. 2 ил. S О) со 1чЭ 4 О О5

| Устройство записи и воспроизведения цифровой информации | 1976 |

|

SU590808A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для записи и воспроизведения цифровой информации на магнитном носителе | 1976 |

|

SU585523A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-15—Публикация

1986-02-18—Подача