Фиг. 1

1

1325400

10

15

20

f

25

30

Изобретение может быть использова- . Ho-i электроизмерительной и вычисли- ; ; тейьмЬй технике.

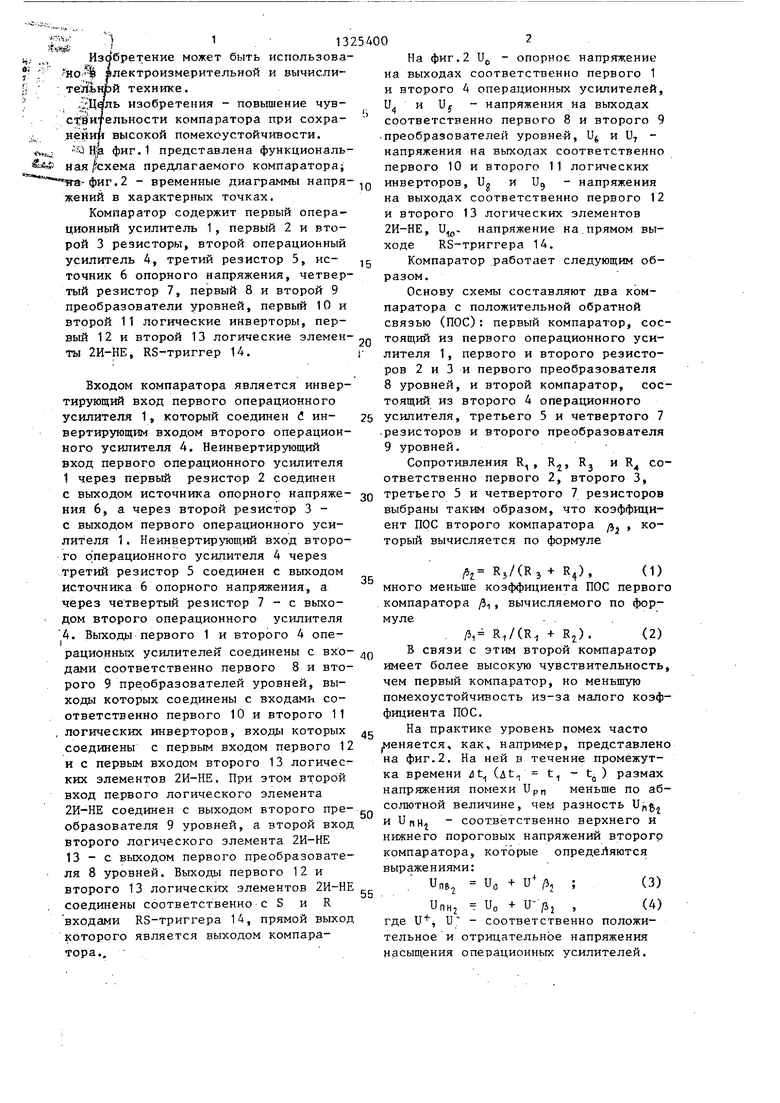

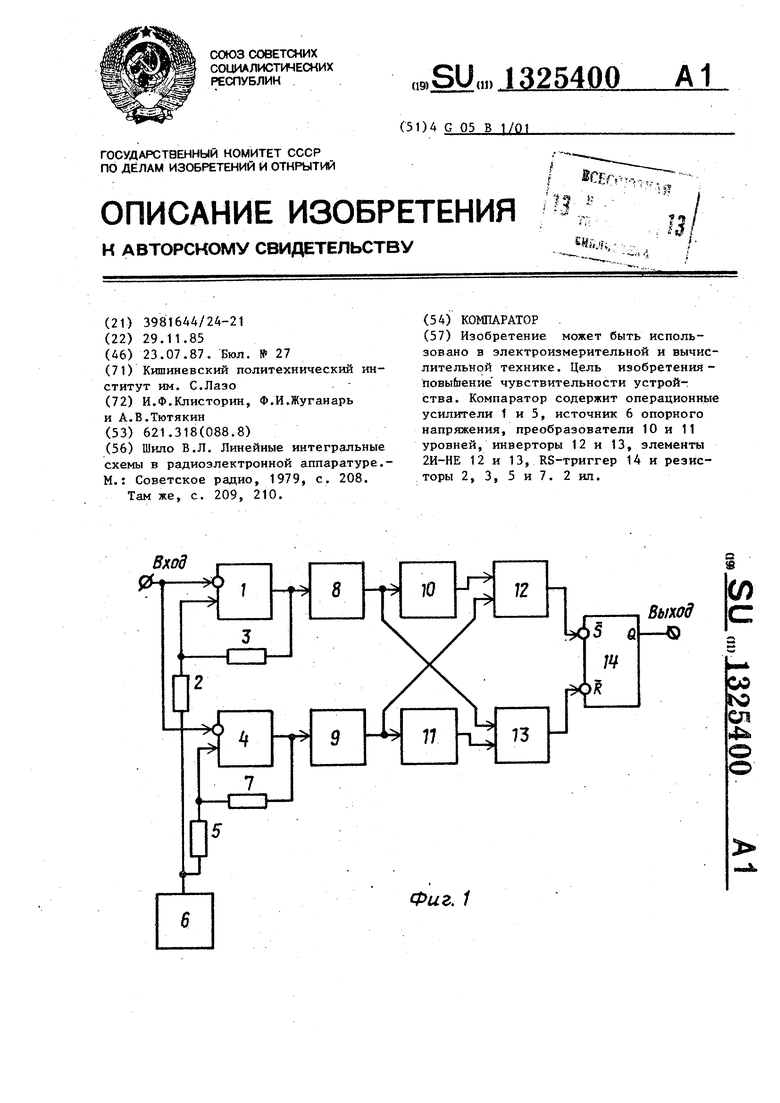

:Цвль изобретения - повышение чув- с|г;Э ительности компаратора при сохра- ;, не:йии высокой помехоустойчивости. Ц; фиг. 1 представлена функциональ- и ная|схема предлагаемого компаратора; wa:-фиг. 2 - временные диаграммы напряжений в характерных точках.

Компаратор содержит первый операционный усилитель 1, первый 2 и второй 3 резисторы, второй операционный усилитель 4, третий резистор 5, источник 6 опорного напряжения, четвертый резистор 7, первый 8 и второй 9 преобразователи уровней, первый 10 и второй 11 логические инверторы, первый 12 и второй 13 логические элементы 2И-НЕ, RS-триггер 14.

Входом компаратора является инвертирующий вход первого операционного усилителя 1, который соединен инвертирующим входом второго операционного усилителя 4. Неинвертирующий вход первого операционного усилителя 1 через первый резистор 2 соединен с выходом источника опорного напряжения 6, а через второй резистор 3 - с выходом первого операционного усилителя 1. Неинвертирующий вход второго о перационного усилителя 4 через третий резистор 5 соединен с выходом источника 6 опорного напряжения, а через четвертый резистор 7 - с выходом второго операционного усилителя 4. Выходы первого 1 и второго 4 операционных усилителей соединены с входами соответственно первого 8 и второго 9 преобразователей уровней, выходы которых соединены с входами соответственно первого 10 и второго 11 , логических инверторов, входы которых соединены с первым входом первого 12 и с первым входом второго 13 логических элементов 2И-НЕ. При этом второй вход первого логического элемента 2И-НЕ соединен с выходом второго преобразователя 9 уровней, а второй вход второго логического элемента 2И-НЕ 13 - с выходом первого преобразователя 8 уровней. Выходы первого 12 и второго 13 логических элементов 2И-НЕ соединены соответственно с S и R входами RS-триггера 14, прямой выход которого является выходом компаратора..

35

40

45

50

на и и со пр на пе ин на и хо

ра

па св то ли ро

то ус

-ре

от тр вы ен то

мн ко му

им че по фи

ме на ка на со и ни ко вы

те на

гд

0

5

0

5

0

5

0

5

0

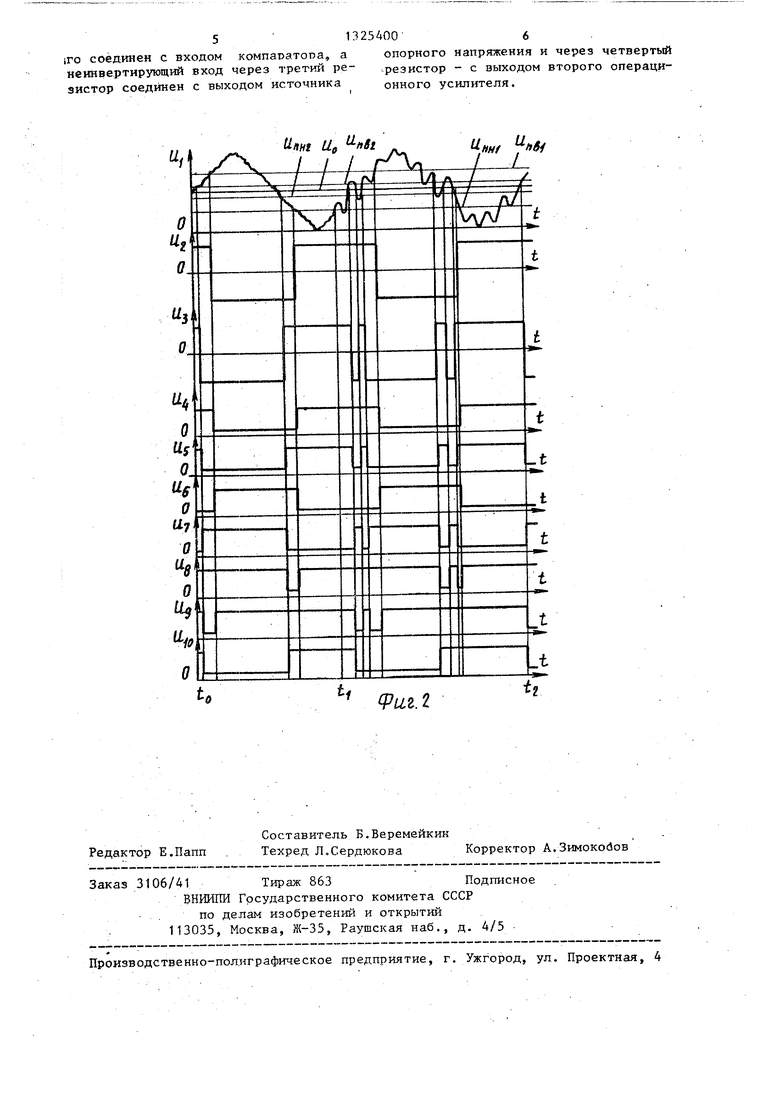

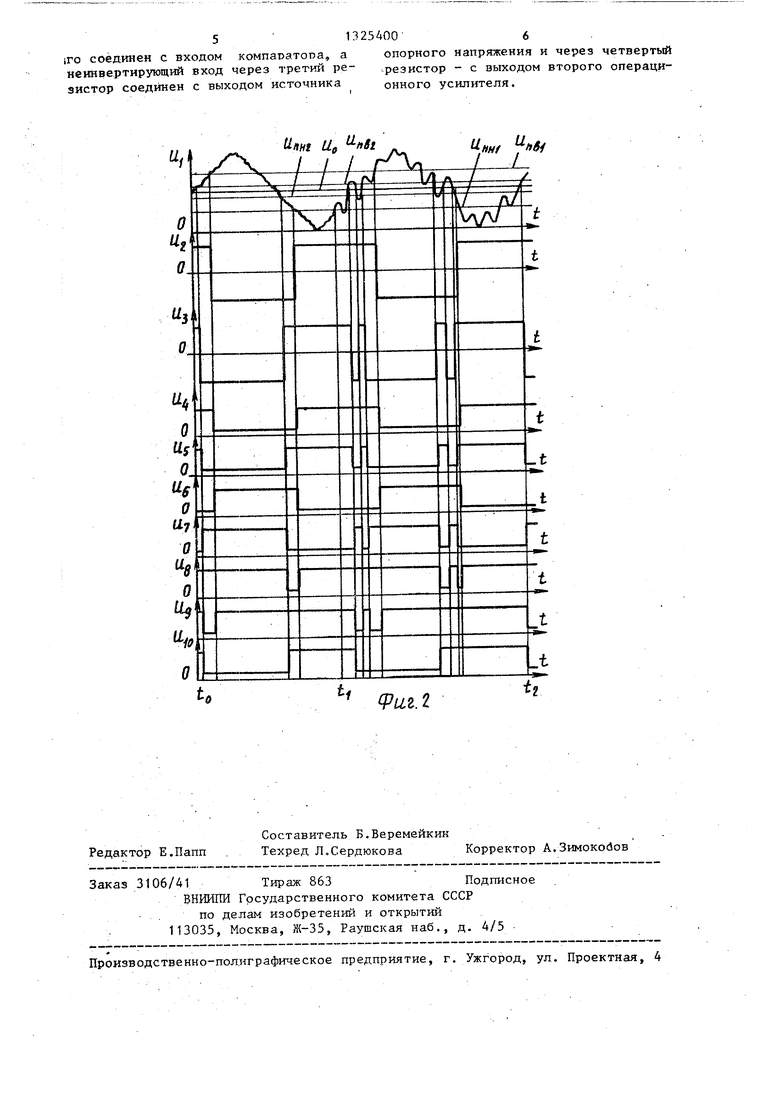

На фиг. 2 Uj, - опорное напряжение на выходах соответственно первого 1 и второго 4 операционных усилителей, и. и Uj - напряжения на выходах соответственно первого 8 и второго 9 преобразователей уровне-й, U и U - напряжения на выходах соответственно первого 10 и второго 11 логических инверторов, Ug и Uj - напряжения на выходах соответственно первого 12 и второго 13 логических элементов 2И-НЕ, напряжение на.прямом выходе RS-триггера 14.

Компаратор работает следующим образом.

Основу схемы составляют два компаратора с положительной обратной связью (ПОС): первый компаратор, состоящий из первого операционного усилителя 1, первого и второго резисторов 2 и 3 и первого преобразователя

8уровней, и второй компаратор, состоящий из второго 4 операционного усилителя, третьего 5 и четвертого 7

-резисторов и второго преобразователя

9уровней.

Сопротивления R, R, R. и R соответственно первого 2, второго 3, третьего 5 и четвертого 7 резисторов выбраны таким образом, что коэффициент ПОС второго компаратора ft. , который вычисляется по формуле

RJ/CR, + R), (1)

много меньше коэффициента ПОС первого компаратора /Э , вычисляемого по формуле. .

. /3, R,/(R, + Rj). (2)

В связи с этим второй компаратор имеет более высокую чувствительность, чем первый компаратор, но меньшую помехоустойчивость из-за малого коэффициента ПОС.

На практике уровень помех часто меняется, как, например, представлено на фиг.2. На ней в течение промежутка времени л Ц (it t, - t ) размах напряжения помехи Upn меньше по абсолютной величине, чем разность U,,. и UfiHj соответственно верхнего и нижнего пороговых напряжений второго компаратора, которые определяются выражениями: Une

и,.

и А,

(3)

и,, + , (4) соответственно положительное и отрицательное напряжения насыщения операционньк усилителей.

UnH2 где и-, и; В течение промежутка времени atj (ut t ) значение Up,, по аб- co DOтнoй величин е больше, чем разность Чпвз j ° меньше, чем разность ипв и Up,, соответственно верхнего и нижнего пороговых напряжений первого компаратора, которые определяются выражениями:

Une, Uo + U, ; (5)

UHH, Uo + U-p/. (6) В связи с вьппесказанным в течение промежутка времени происходит устойчивое переключение обоих компарато- ров. В течение промежутка времени /Itj при переходе входного напряжения через опорный уровень UQ происходят неустойчивые колебания выходного напряжения второго компаратора между значениями U и U в зависимости от мгновенного значения напряжения помехи. Первый компаратор переключается по-прежнему устойчиво. Вьшесказанное отражено на временных диаграммах на- пряжений Uj и и на фиг.2.

Первый 8 и второй 9 преобразователи уровней предназначены для ограничения напряжений и U до уровней соответственно логической единицы и логического нуля, необходимых для нормальной работы структурных элементов 10-14.

Работа цифровой части компаратора, которая состоит из логических инверторов 10 и 11, логических элементов 2И-НЕ- 12 и 13, триггера 14, поясня- ,ется временными диаграммами напряжений , приведенными на фиг.2. При этом необходимо отметить, что RS-триггер 14 является асинхронным, управляемым по входам R и S напряжением логического нуля. Очевидно, при поступлении пачки импульсов на один из входов RS-триггера 14 и при напряжении логической единицы на его другом входе RS-триггер 14 реагирует на первый перепад напряжения из единичного в нулевое значение на первом из упомянутых входов, и последующие перепады напряжения на этом входе уже не изменяют состояние RS-триггера

14. Следовательно, колебания напряжения на выходе второго операционного усилителя 4 в течение промежутка времени &t не влияют на устойчивость срабатьгоания RS-триггера 14.

Таким образом, происходит устойчивое срабатывание компаратора с чув

5

о

Q g

g

5

ствительностью, обеспечиваемой значением коэффициента ПОС ft в обоих следующих случаях: при значении Up , меньшем по абсолютному значению, чем разность Une,2 пн (промежуток времени jt, , в течение которого при наличии одного только первого компаратора происходило бы значительное снижение чувствительности из-за большого значения /j , что имеет место в известном компараторе); при значении Upp , большем по абсолютному значению, чем разность и UnH, , но меньшем, чем разность Uf, и UnH (промежуток времени itj, в течение которого второй компаратор срабатывает неустойчиво из-за помех).

Формула изобретения

Компаратор, содержащий первый операционный усилитель, инвертирующий вход которого является входом компаратора, а неинвертирующий вход через первый резистор соединен с выходом источника опорного напряжения и через второй резистор - с выходом первого операционного усилителя, который соединен также с входом первого преобразователя уровней, отличающийся тем, что, с целью повьше- ния чувствительности при сохранении высокой помехоустойчивости, в него введены второй операционньй усилитель, третий и четвертый резисторы, второй преобразователь уровней, первый и второй логические инверторы, первый и второй логические элементы 2И-НЕ и RS-триггер, прямой выход которого является выходом компаратора, S-вход RS-триггера соединен с выходом первого логического элемента 2И-НЕ,, первый вход которого соединен с выходом первого логического инвертора, а второй вход - с выходом второго преобразователя уровней, R-вход RS- триггера соединен с выходом второго логического элемента 2И-НЕ, первый вход которого соединен с выходом второго логического инвертора, а второй вход - с выходом первого преобразователя уровней, входы первого и второго логических инверторов соединены соответственно с выходами первого и второго преобразователей уровней, вход второго преобразователя уровней соединен с выходом второго операционного усилителя, инвертирующий вход которо-,

5 13254006

iro соединен с входом компасатопа, а опорного напряжения и через четвертый неинвертирующий вход через третий ре- .резистор - с выходом второго операци- зистор соединен с выходом источника онного усилителя.

f

Редактор Е.Папп

Составитель Б.Веремейкик

Техред ЛоСердюкова Корректор А.Зимокобов

Заказ 3106/41 Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

. по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

11роизводственно-пол.играфическое предприятие, г, Ужгород, ул. Проектная, 4

9иг.г

г

| название | год | авторы | номер документа |

|---|---|---|---|

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ИМПУЛЬСНЫМ РЕГУЛИРОВАНИЕМ | 1991 |

|

RU2014646C1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Устройство для измерения параметров линейных микросхем | 1978 |

|

SU752207A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Измеритель отношения двух сигналов | 1986 |

|

SU1465791A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1444950A1 |

| Вибрационный источник сейсмических сигналов | 1985 |

|

SU1277034A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

Изобретение может быть использовано в электроизмерительной и вычислительной технике. Цель изобретения - повыЬение чувствительности устройства. Компаратор содержит операционные усилители 1 и 5, источник 6 опорного напряжения, преобразователи 10 и 11 уровней, инверторы 12 и 13, элементы 2И-НЕ 12 и 13, RS-триггер 14 и резисторы 2,3,5и7.2ш1. Вход (Л С

| Шило В.Л | |||

| Линейные интегральные схемы в радиоэлектронной аппаратуре.- М.: Советское радио, 1979, с | |||

| Гидравлическая или пневматическая передача | 0 |

|

SU208A1 |

| Там же, с | |||

| Парный рычажный домкрат | 1919 |

|

SU209A1 |

Авторы

Даты

1987-07-23—Публикация

1985-11-29—Подача