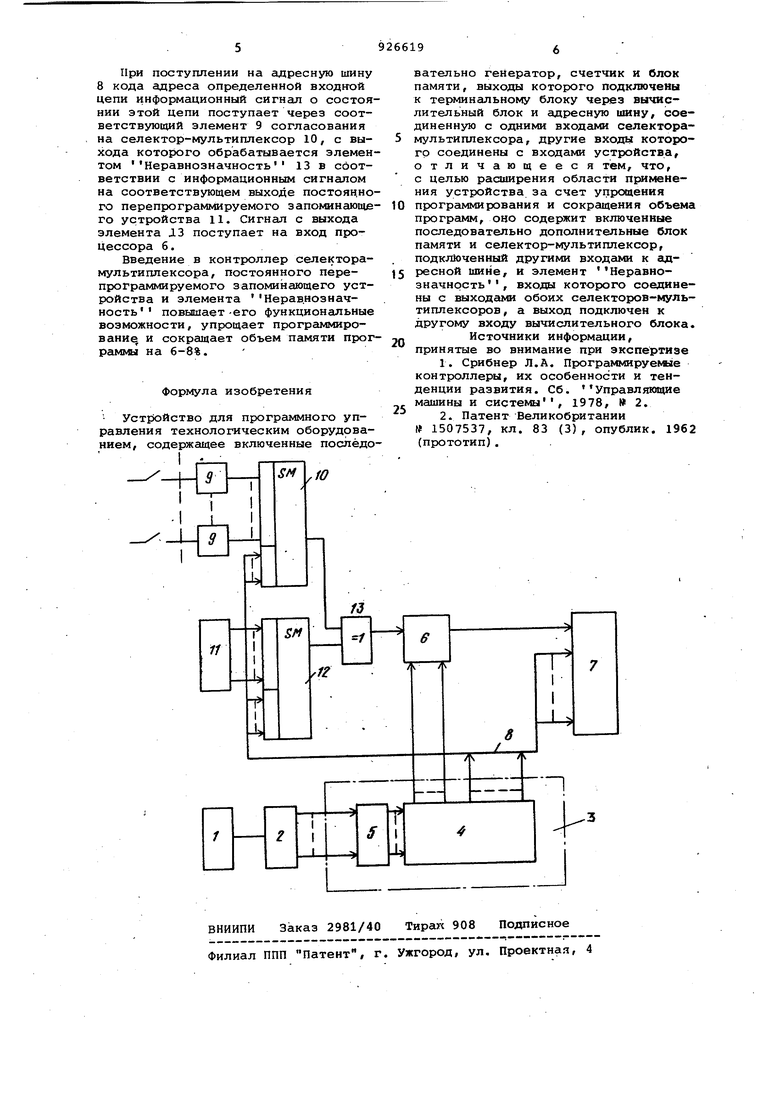

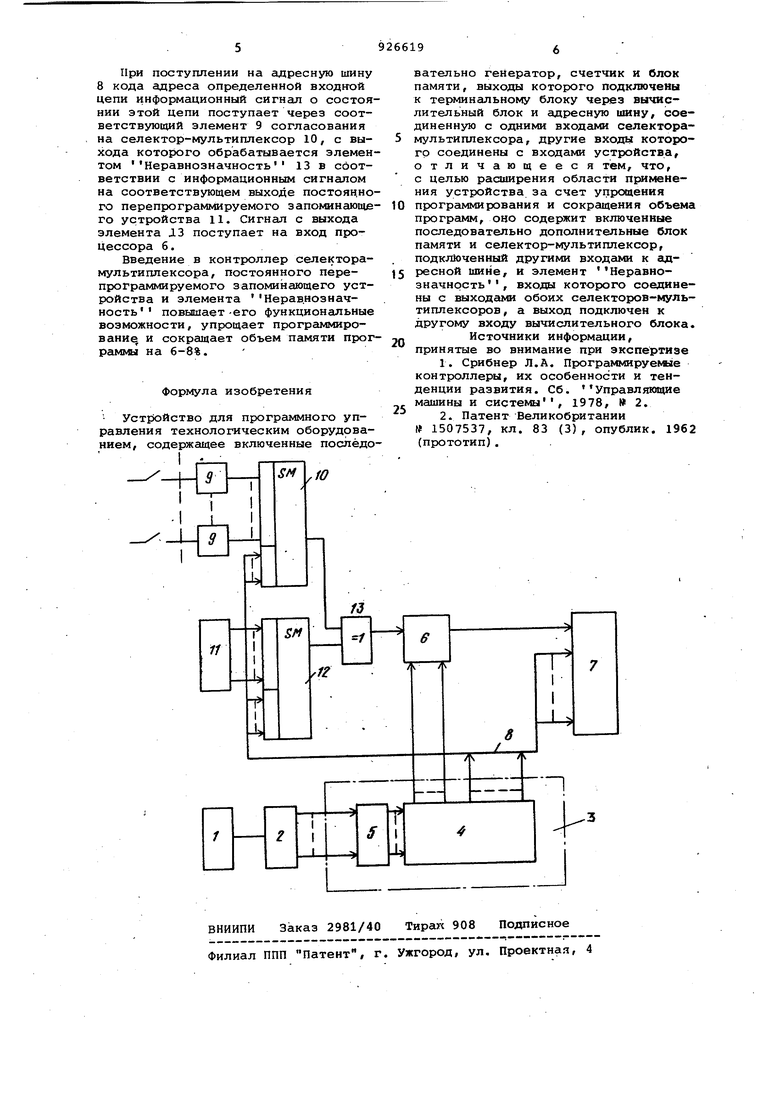

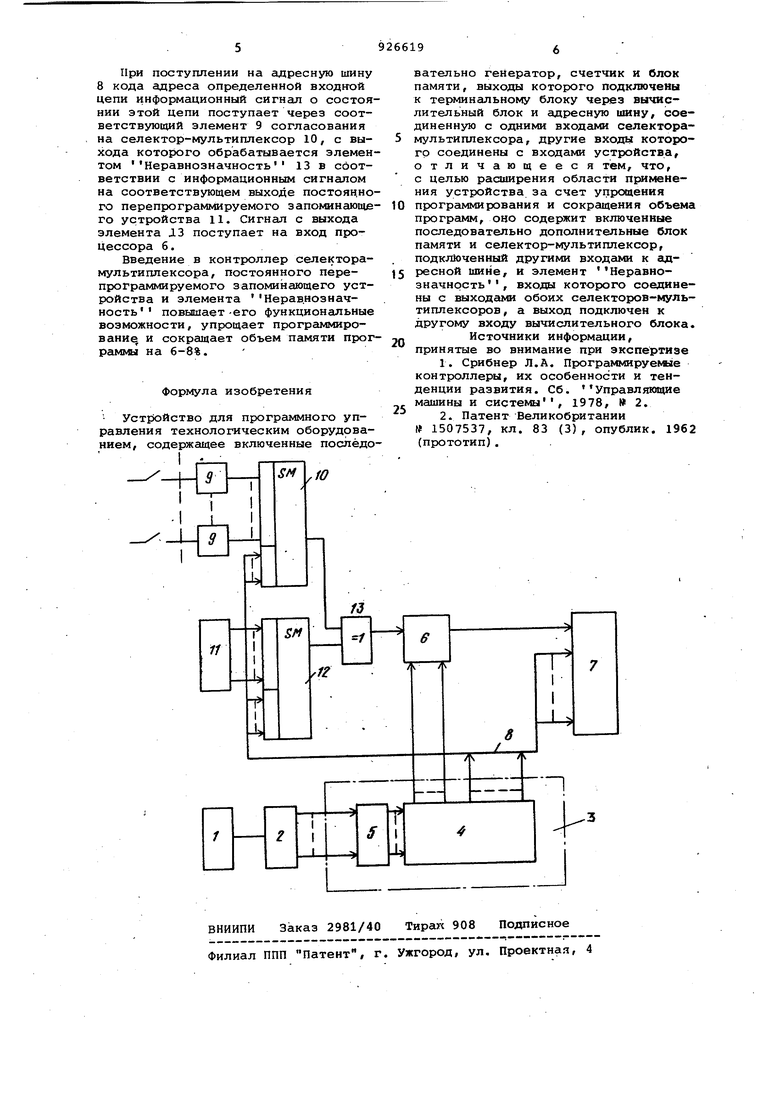

и селектор-мультиплексор, подключенный другими входами к адресной шине, и элемент Неравнозначность входы которого соединены с выходами обоих селекторов-мультиплексоров, а выход подключен к другому входу вычислительного блока. На чертеже приведена структурная схема предлагаемого устройства. Устройство содержит генератор 1 счетчик 2, блок 3 памяти, состоящий из многоразрядных ячеек 4 памяти и схемы 5 выборки многоразрядных кодов, вычислительный блок (процессо 6, терминальный блок (блок формирования выходных сигналов) 7, адресную шину 8, элементы 9 согласовани селектор-мультиплексор Юс внутрен ним дешифратором и элементами И, до полнительный блок памяти (постоянно перепрограммируемое запоминающее устройство) 11, селектор-мультиплек сор 12с внутренним дешифратором и элементами И и элемент Неравнозначность 13. Устройство работает следующим образом. Генератор 1 формирует импульсы, которые с.его выхода поступают на вход счетчика 2, где пересчитываютс На выходах счетчика 2 формируется код, который подается на управляющи входы схемы 5 выборки. Схема 5 обес печивает выдачу содержимого из ячее 4 памяти, код адреса которой установлен на входах схемы 5. Каждый следующий импульс устанав ливает на выходах счетчика 2 новый адрес и так до тех пор, пока не будет считано содержимое всех ячеек. Затем цикл считывания повторяется. На выходах блока 3 памяти после довательно формируются коды команд, которыесостоят из двух частей кода адреса и кода операции. Код операции поступает на входы процессора 6, код адреса - в адресную шину 8. Процессор 6 реализует логическую функцию (дизъюнкцию, конъюнкцию и др.) над операндом, поступающим на его вход с выхода элемента Неравнозначность 13 и операндом, хранящимся в памяти процессора 6, в соответствии с, кодом операции на его входах, соединенных с выходами блока 3 памяти, результат операции подается с выхода процессора 6 в блок 7 формирования выходных сигналов, который по команде из блока 3 памяти принимает операнд и формирует выходной сигнал, соответствующий значению операнда на том выходе, адрес которого портупает из адресной шины 8. Формирование операнда на входе процессора 6 происходит под управлением селектора-мультиплексора 12. Входы селектора-мультиплексора 12 соединены с выходами постоянного перепрограммируемого устройства 11, разряды кода в котором сформированы в зависимости от вида контакта коммутационного элемента в соответствующей входной цепи. входной цепи стоит нормально разомкнутый контакт, то в соответствующем разряде постоянного перепрограммируемого запоминающего устройства 11 записан логический О , если нормально замкнутый контакт - логическая . Коды, поступающие на адресные входы селекторов-мультиплексоров 10 и 12, обеспечивают подключение к выходу селектора-мультиплексора 10 поочередно сигналов со всех входных цепей и к выходу селектора-мультиплексора 12 - значений соответствующих разрядов кода, хранящегося в постоянном перепрограммируемом запоминающем устройстве 11. Оба выхода селекторов-мультиплексоров 10 и 12 подключены ко входам элемента Heравнозначность 13. Во время присутствия на шине 8 одного значения кода элемент Heравнозначность 13 инвертирует или неинвертирует информационный сигнал с выхода селектора-мультиплексора 10 в зависимости от значения двоичной переменной на выходе селекторамультиплексора 12 в соответствии с таблицей. При поступлении на адресную шину 8 кода адреса определенной входной цепи информационный сигнал о состоя нии этой цепи поступает через соответствующий элемент 9 согласования на селектор-мультиплексор 10, с выхода которого обрабатывается элемен том Неравнозначность 13 в сЬответствии с информационным сигналом на соответствующем выходе постоян.но го nepenporpaMivwpyeMoro запоминающе го устройства 11. Сигнал с выхода элемента ДЗ поступает на вход процессора 6. Введение в контроллер селекторамультиплексора, постоянного перепрограммируемого запоминающего устройства и элемента Неравнозначность повышает-его функционгшьные возможности, упрощает программировани и сокращает объем памяти прог раммы на 6-8%. Формула изобретения Устркэйство для программного управления технологическим оборудованием, содержсидее включенные послёдо вательно генератор, счетчик и блок памяти, выходы которого подключены к терминальному блоку через вычислительный блок и адресную ишну, соединенную с одними вxoдa и селекторамультиплексора, другие входы которого соединены с входами устройства, отличающееся тем, что, с целью расширения области применения устройства за счет упрощения программирования и сокращения объема программ, оно содержит включенные последовательно дополнительные блок памяти и селектор-мультиплексор, подклйченный другими входс1МИ к гщресной шине, и элемент Неравнозначность , входы которого соединены с выходами обоих селекторов-мультиплексоров , а выход подключен к другому входу вычислительного блока. Источники информации, принятые во внимание при экспертизе 1.Срибнер Л.А. Программируемые контроллеры, их особенности и тенденции развития. Сб. Управляющие машины и системы , 1978, 2. 2.Патент Великобритании № 1507537, кл. 83 (3), опублик. 1962 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1977 |

|

SU691858A1 |

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| Устройство для программного управления технологическим оборудованием | 1985 |

|

SU1325407A1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

Авторы

Даты

1982-05-07—Публикация

1980-01-04—Подача