Изобретение относится к вычислительной технике и может быть использовано при проектировании устройств распознавания образов.

Цель изобретения - упрощение программируемой логической матрицы (ПЛМ).

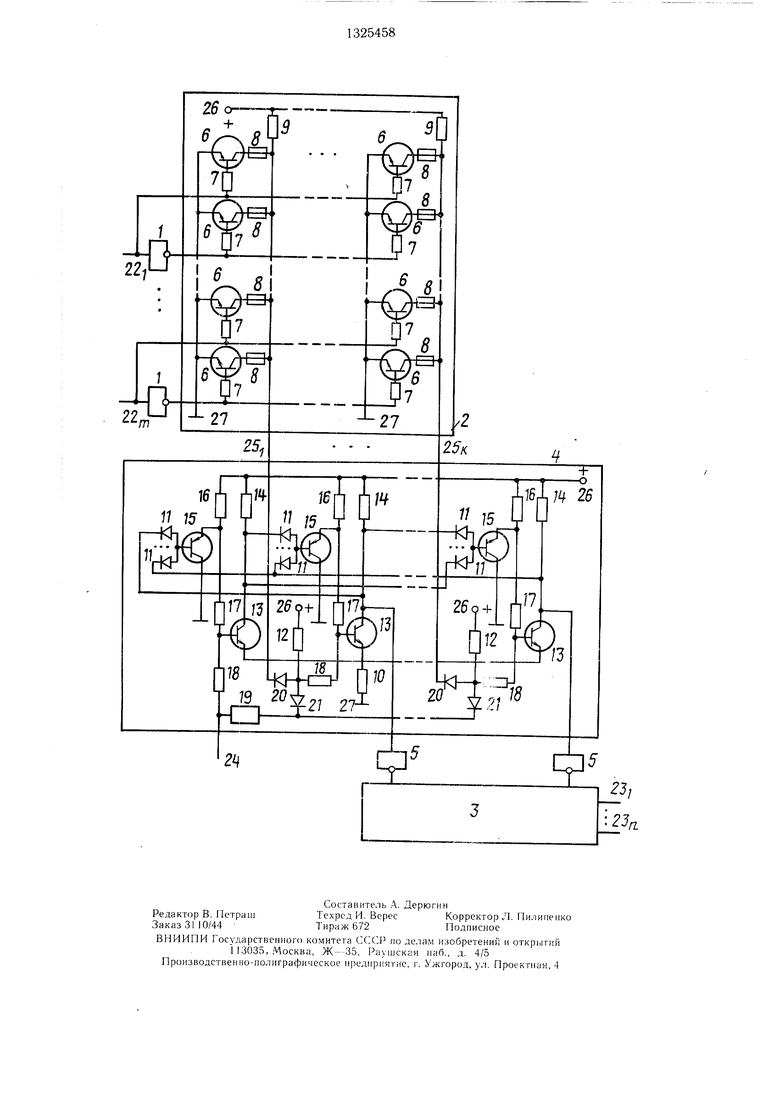

На чертеже приведена схема ПЛМ.

ПЛМ содержит m элементов НЕ 1, К элементов И 2, п элементов ИЛИ 3 (т, К, п - число входов, термов и выходов ПЛМ), пороговый блок 4 и К дополнительных элементов НЕ 5.

Элементы И 2 выполнены в виде матрицы. Каждый элемент И соответствует столбцу матрицы и имеет 2т входов. Элемент И состоит из транзисторов 6 связи, ограничительных резисторов 7, кодовых перемычек 8 и нагрузочного резистора 9.

Пороговый блок 4 содержит резистор 10 смещения, группы диодов 11 развязки, нагрузочные резисторы 12 первой группы, усилительные транзисторы 13, нагрузочные резисторы 14 второй группы, транзисторы 15 обратной связи, резисторы 16 обратной связи, ограничительные резисторы 17, согласующие резисторы 18, элемент 19 задержки, разделительные диоды первой 20 и второй

21групп. На чертеже показаны также входы

22и выходы 23 ПЛМ, вход 24 сброса ПЛМ, выходы 25 элементов И, шины 26 питания и шину 27 нулевого потенциала.

ПЛМ работает следующим образом.

Пороговый блок 4 может находиться в одном из(К+1) устойчивых состояний, когда один из транзисторов 13 открыт, а все остальные транзисторы закрыты. Например, при открытом последнем (левом на чертеже) транзисторе 13 потенциал его коллектора низкий. Через диоды 11, подключенные к данному коллектору, низкий потенциал передается на эмиттеры всех транзисторов 15 связи, кроме последнего (левого) транзистора 15, и через делители на резисторах 17 и 18 в соответствующей пропорции поступает на входы всех остальных транзисторов 13, закрывая их. Высокие потенциалы коллекторов всех закрытых транзисторов 13 приводят к запиранию всех диодов 11 транзистора 15 (левого) и, как следствие самого транзистора 15. Потенциал его эмиттера определяется делителем на резисторах 16-18 и удерживает транзистор 13 (левый) в открытом состоянии.

Состояние порогового блока 4, при котором открыт транзистор 13, соответствующий входу 24 (левый), является нулевым, а установка в ноль осуп ествляется подачей на данный вход кратковременного импульса положительной полярности. Схема, вырабатывающая установочный импульс, и элемент 19 задержки должны иметь низкое выходное сопротивление, благодаря чему соответствующие выводы резисторов 18 через открытые разделительные диоды 21 и эле.мент 19 задержки подключаются к тине нулевого потенциала.

Занесение кода, например, 1...0 в (левый) элемент И 2 осуществляется следующим образом. Примем нумерацию разрядов в коде слева направо в тексте и сверху вниз на чертеже. Для занесения единицы первого разряда исключается перемычка 8, соответствующая прямому входу первого разряда (верхняя). Для занесения нуля последнего разряда исключается перемычка 8, соответствующая инверсному входу последнего разряда (нижняя).

Предположим, что в первый (левый) и в последний (правый) элементы И занесены

5 соответственно следующие (эталонные) коды: 101 110и011000 (т 6), а на вход ПЛМ подан код, совпадающий с первым из приведенных. Все транзисторы 6 первого элемента И будут закрыты, а потенциал на выходе 25| будет максимальным, равным на0 пряжению питания. Входной код отличается от кода последнего элемента И в разрядах, именно в 1, 2, 4 и 5. С.ледовательно, данные транзисторы пocJ eднeгo элемента И открыты, а напряжение на выходе 25 на величину,

5 равную 4Д, меньше напряжения питания. Значение Д определяется током открытого транзистора 6 и зависит от выбранного номинала резистора 7.

После подачи на вход 24 положительного импульса блок 4 устанавливается в

0 нулевое положение, при котором на его выходах (всех) присутствуют высокие потенциалы, а на выходах элементов НЕ 5 - низкие.

Через время, определяемое элементом 19 задержки и (еобходимое для установки

5 блока 4 в нуль, на выхолче элемента задержки появляется положительный импульс, закрывающий диоды 21. На время действия положительного управляющего импульса сигналы с выходов 25, различные по амплитуде, подводятся к входам соответствующих транзисторов 13 через резисторы 18. При этом в открытом состоянии оказывается тот транзистор 13, положительный сигнал на входе которого наибольший, т.е. транзистор 13, соответствующий выходу 25i (второй сле- 45 ва). Время действия положительного импульса на выходе элемента 19 задержки должно быть достаточным для установки порогового блока 4 в новое состояние. При этом высокий потенциал присутствует на выходе первого элемента НЕ 5 (слева). 50 Если на вход ПЛМ подвести код, отличный от первого и второго эталонных кодов, например 1 1 1 1 1 О, то в первом элементе И будет открыт 2-й транзистор, а в К-м - 1, 4 и 5-й (транзисторы с второго по пятый не изображены). Следовательно, на первом вы- 55 ходе блока 2 высокий потенциал уменьшен на величину А, а на К-м выходе - на ЗА. После подачи на вход 24 положительного импульса блок 4 также переходит в состояние,

0

соответствующее первому входу, а на выходе блока 3 появляется код, соответствующий выходу первого элемента И. Таким образом, данный входной код распознан как первый эталонный образ.

Значение резистора 10 определяет порог срабатывания блока 4 по входам, а значение резистора 7 определяет величину различия входных и эталонных кодов, равную 1Д, где F - количество отличий в одноименных разрядах.

Если входной код ПЛМ отличен от всех эталонных кодов элементов И, причем все выходные сигналы блока 2 ниже порога срабатывания блока 4, то блок 4 остается в нулевом состоянии и на выходе ПЛМ нулевая информация. В данном случае входной код не распознан.

Если входной код ПЛМ отличен от всех эталонных кодов элементов И, причем среди выходных сигналов блока 2, превысивщих порог срабатывания блока 4, имеются одинаковые, то блок 4 устанавливается в состояние, соответствующее одному из таких сигналов. Для получения от ПЛМ более четкого ответа в данном случае этот входной код необходимо разместить в одном из свободных элементов И и в матрицу 3 занести его имя.

Таким образом, на выходе ПЛМ устанавливаются требуемые коды не только при полном совпадении входного кода с кодом, записанным в одном из элементов И, но и при отличии входного кода от записанных кодов, при этом всякий раз на выходе ПЛМ устанавливается код, соответствующий элементу И с наименьщим числом отличий от входного кода.

Формула изобретения

1. Программируемая логическая матрица, содержащая элементы НЕ, вход каждого из которых является входом программируемой логической матрицы, элементы И, входы которых соединены с входами и выходами элементов НЕ, элементы ИЛИ, выходы которых являются выходами программируемой логической матрицы, отличающаяся тем, что, с целью упрощения матрицы, она содержит

пороговый блок и дополнительные элементы НЕ, выходы которых соединены с входами элементов ИЛИ, а входы - с выходами порогового блока, установочные входы которого соединены с выходами соответствующих элементов И, а вход сброса является управляющим входом программируемой логической матрицы.

2. Матрица по п. 1, отличающаяся тем,

Q что пороговый блок содержит усилительные транзисторы, транзисторы обратной связи, группы диодов развязки, разделительные диоды первой и второй групп, элемент задержки, нагрузочные резисторы первой и второй групп, согласующие резисторы, ограни5 чительные резисторы, резисторы обратной связи и резистор смещения, первый вывод которого соединен с эмиттерами усилительных транзисторов, коллектор каждого из которых соединен с катодами одноименных диодов развязки каждой группы и с первым

выводом соответствующего нагрузочного резистора второй группы, а база - с первыми выводами соответствующих ограничительного и согласующего резисторов, эмиттер каждого транзистора обратной связи соеди5 нен с первым выводом соответствующего резистора обратной связи и вторым выводом соответствующего ограничительного резистора, база - с анодами диодов развязки соответствующей группы, а коллектор и второй вывод резистора смещения соединены с щи0 ной нулевого потенциала, второй вывод каждого согласующего резистора, кроме последнего, соединен с первым выводом соответствующего нагрузочного резистора первой группы и с анодами соответствующих разделительных диодов первой и второй групп,

5 катоды разделительных диодов первой группы являются соответствующими установочными входами порогового блока, а катоды разделительных диодов второй группы соединены с выходом элемента задержки, вход

,. которого соединен с вторым выводом послед.- него согласующего резистора и является входом сброса порогового элемента, вторые выводы резисторов обратной связи и нагрузочных резисторов первой и второй групп соединены с шиной питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Программатор | 1987 |

|

SU1654869A1 |

| Программируемая логическая матрица | 1989 |

|

SU1695383A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Запоминающее устройство | 1982 |

|

SU1023393A1 |

| Программируемая логическая матрица | 1989 |

|

SU1695387A1 |

| Управляемый стабилизатор напряжения на питающих электродах электронно-лучевой трубки | 1987 |

|

SU1432479A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1327293A1 |

| Динамическая программируемая логическая матрица | 1989 |

|

SU1635217A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании устройств распознавания образов. Целью изобретения является упрощение программируемой логической матрицы. Для достижения поставленной цели программируемая логичес- -ая содержит пороговый элемент, установочные входы которого соединены с выходами элементов И, а выходы - через элементы НЕ с входами элементов ИЛИ. Благодаря этому появилась возможность получать на выходе программируемой логической матрицы требуемые коды не только при полном совпадении входного кода с кодом, записанным в одном из элементов И, но и при отличии входного кода от кодов, записанных в элементах И, при этом выходной код соответствует элементу И с наименьшим числом отличий от входного кода. 1 з.п. ф-лы, 1 ил. со ю сд 4 О1 оо

| Каган Б | |||

| М | |||

| Электронные вычислительные машины и системы.-М.: Энергоатом- нздат, 1985, с | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Баранов С | |||

| И., Синев В | |||

| Н | |||

| Программируемые логические матрицы в цифровых системах | |||

| - Зарубежная радиоэлектроника, 1979, № 1, с | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-12—Подача