Изобретение относится к цифровой вычислительной технике и может быть использовано при построении микропроцессоров и микроЗВМ.

Целью изобретения является повышение быстродействия и снижение потребляемой мощности программируемой логической матрицы (ПЛМ).

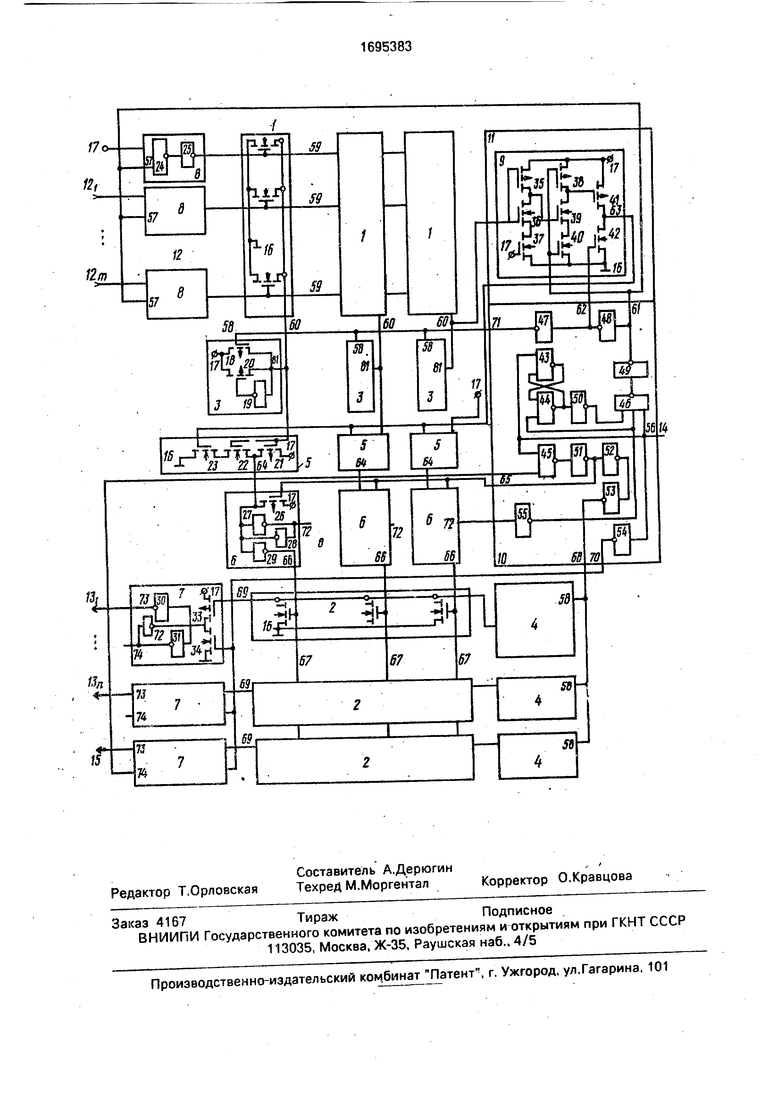

На чертеже изображена принципиальная электрическая схема ПЛМ.

ПЛМ содержит элементы И 1, элементы ИЛИ 2, блоки 3, 4 подзаряда первой и второй групп, усилители 5, блоки 6,7 временного хранения первой и второй групп, блоки установки 8, формирователь 9 сигнала выборки, формирователь 10 импульсов запуска. Формирователи 9 и 10 образуют блок 11 местного управления. На чертеже показаны также информационные входы 12 и выходы 13 ПЛМ, вход выборки 14 ПЛМ. выход готовности 15 ПЛМ, шина 16 нулевого потенциала и шина 17 напряжения питания.

Каждый блок 3,4 подзаряда первой и второй групп содержит МДП-транзистор р- типа 18, который во включенном состоянии осуществляет подзаряд гыхода соответствующего элемента И или ИЛИ до уровня логической 1 в фазе подзаряда ПЛМ.инвер- тор 19 обратной связи и МДП-транзистор р-типа 20, фиксирующие этот уровень на выходе элементов И или ИЛИ.

Каждый усилитель 5 представляет собой инвертор с управляемым переключением в состояние логического О, состоящий из МДП-транзисторов р-типа 21 и п-типа 22 и 23. Каждый блок установки 8 состоит из элемента 2 И-Н Е 24 и инвертора 25 и служит для возбуждения соответствующих входов элементов И и возврата их в исходное логическое состояние.

Каждый блок 6 временного хранения содержит МДП-транзистор р-типа 26, который служит для установки блока в исходное состояние, инвертор 27 и высокоомный инвертор 28 обратной связи, которые вместе

сл С

О Ю СЛ

ы

00

со

образуют ячейку памяти, а также выходной инвертор 29. В блоках временного хранения 6 фиксируется выходной набор термов эле- ментоо И на период выборки элементов ИЛИ.

Каждый блок 7 временного хранения содержит выходной инвертор 30, инвертор 31, образующий вместе с высокоомным инвертором 32 ячейку памяти, а также МДП-тран- зисторы 33 и 34 соответственно р- и п-типа. Транзистор 33 служит для переключения ячеек памяти в процессе выборки ПЛМ, транзистор 34 - для установки в исходное состояние. Блоки временного хранения 7 служат для фиксации выходного набора ППМ до окончания фазы выборки.

Формирователе 9 сигнала выборки со- сиит из грех каскадов. Первый каскад аналогичен усилителю 7 и содержит МДП- транзисторы р-тмпа 35 и п-типа 36 и 37. Второй каскад, состоящий из МДП-транзи- сторов р-типа 38 и п-типа 39 и 40, представляет собой управляемый инвертор, выход которого переключается в состояние логического 0 в зависимости от двух сигналов. Третий каскад состоит из МДП-транзисто- ров р-типа 41 и п-типа 42 и предназначен для управления усилителями.

Формирователь 10 импульсов запуска состоит из элементов 2 И-НЕ 43 и 44, образующих RS триггер, злементов 2 И-НЕ 45 и 3 И-НЕ 46 и инверторов 47-55.

ПЛМ функционирует следующим образом.

В начальном состоянии управляющий CMi нал выборки ПЛМ на входе 14, соот- ветстзу ющий сигналу на входе 56 формирователя 10, находится в состоякии логического 0. При этом в состоянии логического 0 находятся входы запуска 57 и 58 опоков установки 8 и блоков подзаряда 3 ч. соответственно, все входы 59 элементов И. Соответственно, n-канальные транзисторы элементов И выключены, а транзистор 18 блоков подзаряда 3 находится во пключенном состоянии, выходы 60 элементов И заряжены до напряжения питания, а транзистор 21 усилителей 5 выключен, Уровнями логического 0 и 1 соответственно на пятом 61 и третьем 62 выходах формирователя 10 импульсов запуска включены транзисторы 38, 42 и выключен транзистор 40 формирователя 9 сигнала выборки. Выход 63 формирователя 9 сигнала выборки находится в состоянии логического 0,транзистор 23 усилителя 5 выключен. Выход 64 усилителя 5 находится в состоянии высокоомного выходного сопротивпения, транзистор 26 блоков G временного хоанения включен

уровнем логического 0 на четвертом 65 выходе формирователя 10 импульсов запуска и, соответственно, выход 66 блоков 6 временного хранения и соединенные с ним входы 67 элементов ИЛИ установлены в состояние логического 0, n-канальные транзисторы злементов ИЛИ выключены, транзистор 18 блоков подзаряда 4 включен уровнем логического 0 на втором 68 выходе

0 формирователя 10 импульсов запуска, выходы 69 злементов ИЛИ заряжены до напряжения питания. При этом транзистор 33 блоков 7 временного хранения выключен, а транзистор 34 включен уровнем логической

5 1 на шестом выходе 70 формирователя 10 импульсов запуска, и выходы ПЛМ находятся в состоянии логической 1. Первый вход 56 формирователя 10 импульсов запуска находится в состоянии логического 0 и триггер,

0 образованный элементами 2 И-НЕ 43 и 44, установлен в состоянии логического 0 на выходе элемента 44.

При переключении управляющего сигнала выборки ПЛМ 14 в состояние логиче5 ской 1 начинается фаза выборки ПЛМ. На первом ее этапе триггер в формирователе- импульсов запуска переходит в состояние хранения информации, и блокируются элементы, осуществляющие подзаряд выходов

0 злементов И и ИЛИ и предустановку блоков 6, 7 временного хранения. Так, переключаются в состояние логической 1 первый 71, второй 68 и четвертый 65 выходы, в состояние логического 0 - шестой 70 выход блока

5 10, в результате чего выключается транзистор 18 в блоках подзаряда 3 и 4 и транзисторы 26 и 34 в блоках 6, 7 временного хранения. При переключении пятого 61 выхода блока 10 из состояния логического 0 в

0 состояние логической 1 и третьего выхода 62 из состояния логической 1 в состояние логического 0 изменяются состояния транзисторов 38, 40, 42 в блоке 9, блок готов к формированию импульсов запуска усилите5 лей 5. Одновременно происходит запуск блоков.установки 8 и на входных шинах 59 элементов И начинает устанавливаться информация, соответствующая коду на входных шинах 12 ПЛМ. По достижении на

0 шинах 59 уровня порогового напряжения МДП-транзистора п-типа открываются соответствующие транзисторы элементов И. Через эти транзисторы начинают разряжаться связанные с ними выходы элемен5 тов И. Весь этот.процесс формирования выходных термов элементов И моделируется на последнем элементе И, когда выход этого элемента разряжается до точки переключения первого каскада блока 9, выход первого каскада переключается в

состояние логической 1, второй каскад - в состояние логического 0 и выход 63 блока 9 - в состояние логической 1. На выходах усилителей 5, связанных с разряжающимися выходами элементов И, появляется активный уровень логической 1, а выходы усилителей 5, связанные с неразряжающимися выходами элементов И, переключаются в состояние логического 0. Информация с выходов усилителей 5 фиксируется блоками 6 временного хранения, на втором выходе 72 последнего блока б появляется уровень логической 1. Триггер в блоке 10 переключается в состояние логической 1 на выходе элемента 2 И-НЕ 44. Уровень логического 0 на пятом выходе блока 10 блокирует блоки установки 8, и с этого момента процесс на заряжаемых входных шинах 59 элементов И сменяется их разрядом до уровня логического 0.Уровень логического 0 на первом 71 выходе блока 10 включает транзистор 18 в блоках подза- ряда 3 и начинается подзаряд выходов 60 элементов И. Одновременно уровнем логической 1 на третьем выходе 62 блока 10 включается транзистор 42 блока 9 и выход 63 блока 9 переключается в состояние логического 0, а транзистор 23 в усилителе 5 закрывается. Когда на выходах элементов И устанавливается потенциал выше уровня порога МДП-транзисюра р-типа, все усилители переходят в состояние высокого выходного сопротивления.

Описанный подзаряд элементов И совмещен с процессом дальнейшей выборки ПЛМ в целом. В соответствии с записанным содержимым блоков 6 временного хранения, часть входных шин элементов ИЛИ начинает заряжаться. По достижению на этих шинах порогового напряжения МДП-тран- зистора n-типа открываются соответствующие транзисторы элементов ИЛИ. Через эти транзисторы начинают разряжаться связанные с ними выходы 69 элементов ИЛИ. Когда соответствующие выходы элементов ИЛИ разрядятся до порогового напряжения МДП-транзистора р-типа, начинают переключаться в состояние логического 0 выходы 73 блоков 7 временного хранения. С этого момента времени на выходах 73 блоков 7 временного хранения зафиксирован выходной набор разрядности п, представляющий собой запрограммированную булеву функцию от входных переменных.

При этом уровнем логического 0 на втором выходе 74 поел еднего(п+1)-го блока 7 переключается в состояние логического 0 четвертый 65 и второй 68 выходы блока 10. Уровнем логического 0 на четвертом выходе 65 блока 10 включается транзистор 26 в блоках 6. Блоки 6 устанавливаются в состояние логического 0 по выходу 66 и входы 67 элементов ИЛИ начинают разря- жаться. Уровнем логического 0 на втором выходе 68 блока 10 включается транзистор 18 блоков подзаряда 4, и начинается подзаряд выходов 69 элементов ИЛИ. Тоаизистоо 33 в блоках 7 закрывается.

0Появление логического 0 на выходе последнего (пН)-го блока 7 является признаком готовности выходного набора ПЛМ для внешних устройств. По завершении использования кода на выходах 13 ПЛМ внеш5 нее устройство переводит сигнал выборки на входе 14 ПЛМ из состояния логической 1 в состояние логического 0, и фаза выборки ПЛМ заканчивается. При переключении сигнала выборки ПЛМ в состояние логического

0 0 начинается фаза предустановки ПЛМ Триггер в блоке 10 переключается в состояние логической 1 по выходу элемента 2 И-НЕ 44, шестой выход 70 блока 10 переключается в состояние логической 1 Этим уровнем

5 открывается транзистор 34 в блоках 7 временного хранения. Блоки 7 переключаются в состояние логической 1 на выходах 71, т с выходы 13 ПЛМ устанавливаются в исходное состояние.

0Как видно из приведенного описания

работы, в предлагаемой ПЛМ реализован асинхронный переход внутри ПЛМ к подза- ряду элементов И и ИЛИ непосредственно в фазе выборки. При этом процесс подзаря5 да элементов И совмещается с началом аы- борки элементов ИЛИ Процесс подзаряда элементов ИЛИ начинается в фазе выборки с момента записи выходного набора в блоки 7 временного хранения. По переключению

0 внешним блоком синхрочиээции управляющего сигнала выборки ПЛМ в состояние логического 0, внутри ПЛМ подтверждается сосюяние подзаряда для элементов И и ИЛИ. При этом выполняется установка триг5 гера в блоке 10 и блоков временнего хранения 7 в исходное состояние. Эта фаза называется фазой предустановки. Таким образом вместо строго разграниченных фаз -выборки и подзаряда в описанной

0 ПЛМ реализован асинхронный подзаряд элементов И и ИЛИ по завершению формирования на их выходах соответствующего выходного набора данных. Это и дает выигрыш в быстродействии.

5Разряд и заряд входных и выходных

шин элементов И и ИЛИ представляет собой медленный во времени процесс в связи с большой распределенной емкостью шин, достигающих десятка пикофарад. Для уменьшения площади ПЛМ в элементах И и

ИЛИ используются гранзисторы минимальной величины. Как следует из описания работы ПЛМ, процесс выборки развивается до достижения на соответствующих шинах элементов И и ИЛИ пороговых уровней напряжения. Асинхронный переход к подзаря- ду но связи останавливает этот процесс, vi возвращает шины элементов И и ИЛИ з исходное состояние. Таким образом, достигается перезаряд больших емкостей шин элементов И и ИЛИ в неполном диапазоне напряжений между уровнями нулевого напряжения и напряжения питания, что приводит к снижению потребляемой ПЛМ мощности

Формула изобретения

Программируемая логическая матрица, содержащая элементы И, элементы ИЛИ, первую группу блоков подзаряда, причем еыход каждого блока подзаряда первой группы соединен с выходом соответствующего элемента И, вторую группу блоков под- заряда, причем выход каждого блока подзаряда второй группы соединен с выходом соответствующего элемента ИЛИ,усилители, информационный вход каждого из которых, кроме последнего, соединен с выходом соответствующего элемента И, формирователь сигнала выборки, информационный вход которого соединен с выходом последнего элемента И, а выход -со стробирующим входом каждого усилителя, формирователь импульсов запуска, первый вход которого является входом выбор- программируемой логической матрицы, первый и второй выходы соединены со входами запуска блоков подзаряда первой и второй групп соответственно, a tpe- тий выход - с первым входом запуска формирователя сигнала выборки, отличающаяся тем, что, с целью повышения быстродействия и снижения потребляемой мощности, в программируемую логическую матрицу введены первая группа

блоков временного хранения, первый вход каждого из которых соединен с выходом соответствующего усилителя, второй вход- с четвертым выходом формирователя импульсов запуска, выход каждого блока временного хранения первой группы соединен с соответствующим входом каждого элемента ИЛИ, блоки установки, информационный вход каждого из которых, кроме первого, является соответствующим информационным входом программируемой логической матрицы, вход запуска каждого блока установки соединен с пятым выходом формирователя импульсов запуска, выход каждого блока установки соединен с соответствующим входом каждого элемента И, а информационный вход первого блока установки соединен с шиной питания программируемой логической матрицы, вторая группа блоков временного хранения, выход каждого из

которых, кроме последнего, является соответствующим информационным выходом, а последний - выходом готовности программируемой логической матрицы, первый вход каждого блока временного хранения второй

группы соединен с выходом соответствующего элемента ИЛИ, а второй вход - с шестым выходом формирователя импульсов запуска, второй и третий входы формирователя импульсов запуска соединены со

вторыми выходами последних блоков временного хранения первой и второй групп соответственно, второй вход запуска формирователя сигнала выборки соединен с пятым выходом формирователя импульсов

запуска, информационный вход последнего усилителя соединен с шиной питания программируемой логической матрицы.

17

й|

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1989 |

|

SU1695387A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Источник питания | 1980 |

|

SU900376A1 |

| Управляемый формирователь импульсов | 1986 |

|

SU1309302A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2012 |

|

RU2498456C1 |

| Формирователь импульсов на МДП-транзисторах | 1988 |

|

SU1539995A1 |

| Каскадное устройство ортогонального типа для сдвигов многоразрядных операндов | 1989 |

|

SU1661757A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения постоянной памяти типа ПЛМ в БИС управляющей памяти. БИС микропроцессоров. микроЭВМ с высокими требованиями по быстродействию и ограниченным энергопотреблением. Эти качества ПЛМ достигаются за счет обеспечения асинхронного перехода к подзаряду элементов И 1 и элементов ИЛИ 2 непосредственно в фазе выборки. Для этого в устройство дополнительно введены блок установки и две группы блоков 6, 7 временного хранения 1 ил

| Авторское свидетельство СССР № 1345911,кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР N 1424598, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-30—Публикация

1989-03-30—Подача