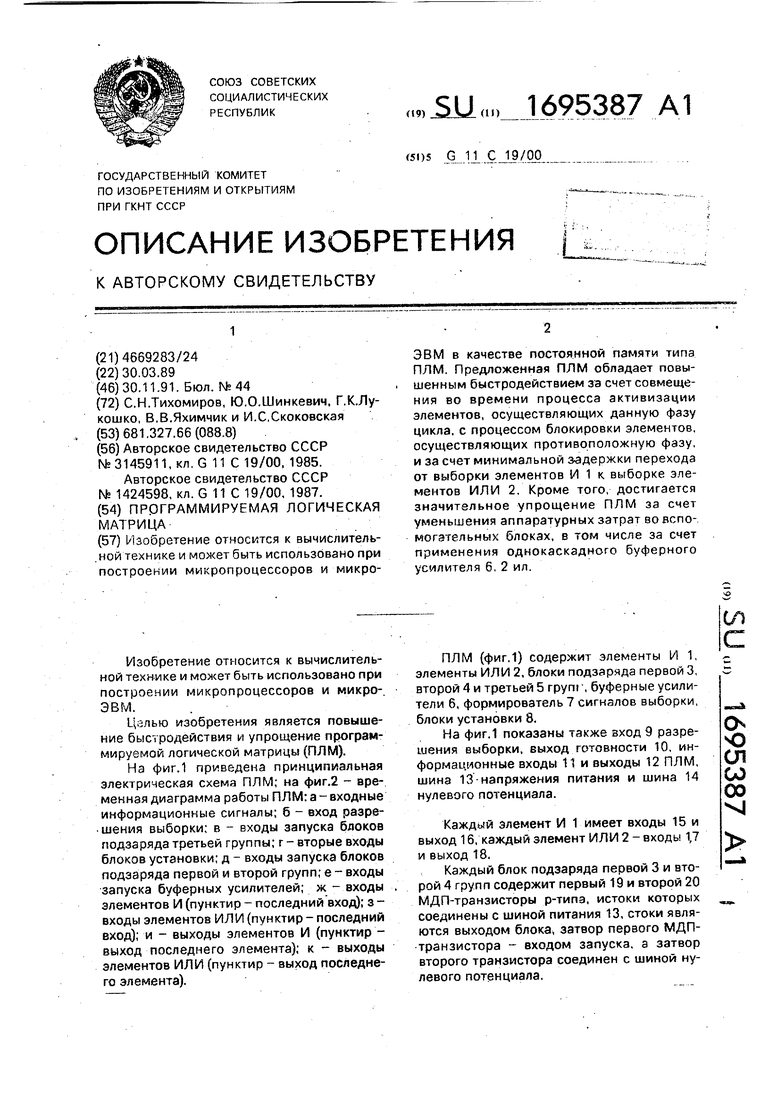

Изобретение относится к вычислительной технике и может быть использовано при построении микропроцессоров и микро- ЭВМ.

Ц.злью изобретения является повышение быстродействия и упрощение программируемой логической матрицы (ПЛМ).

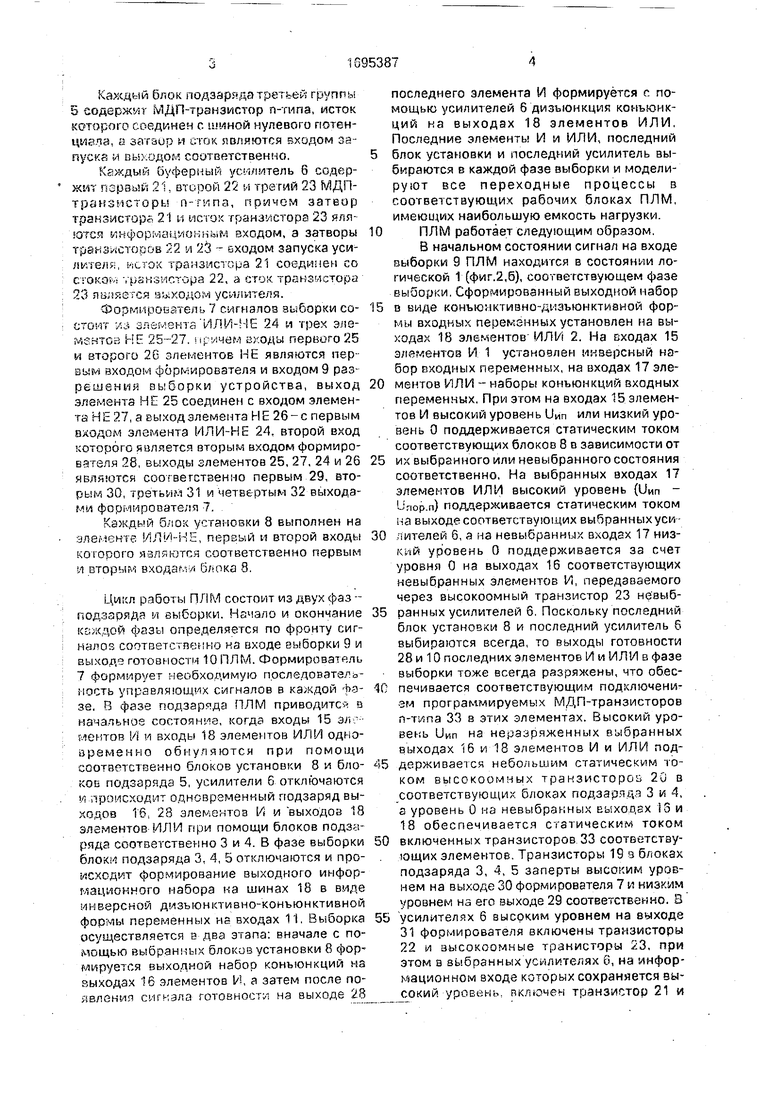

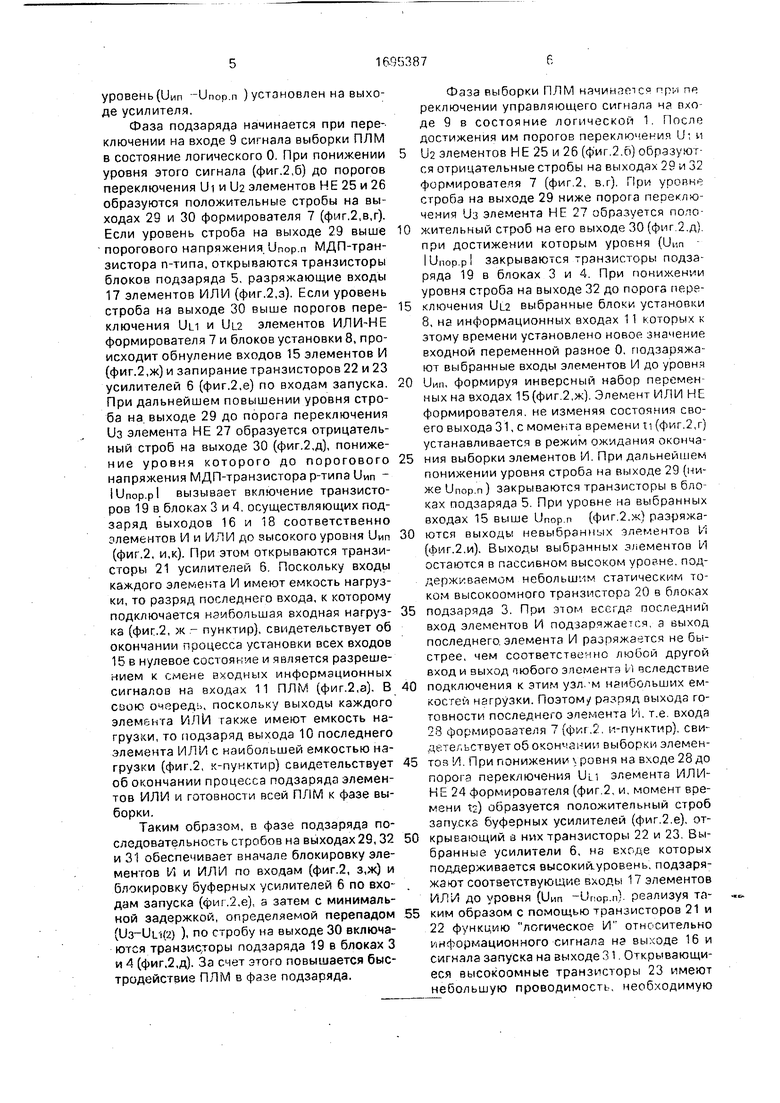

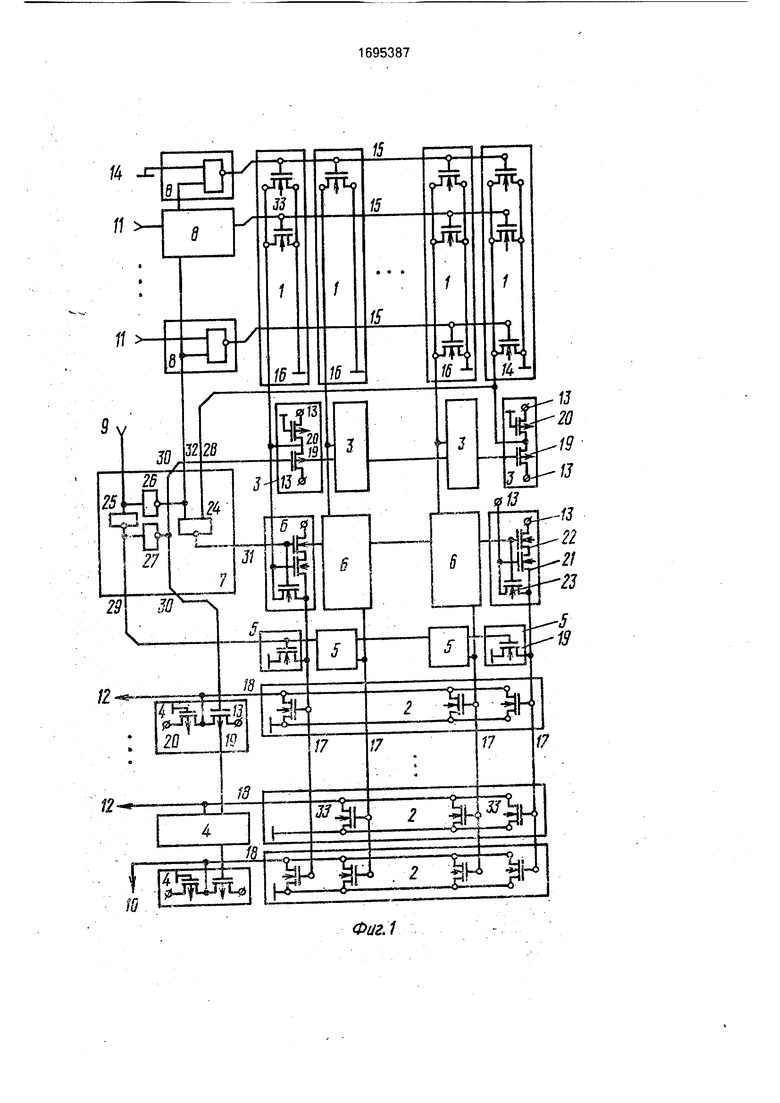

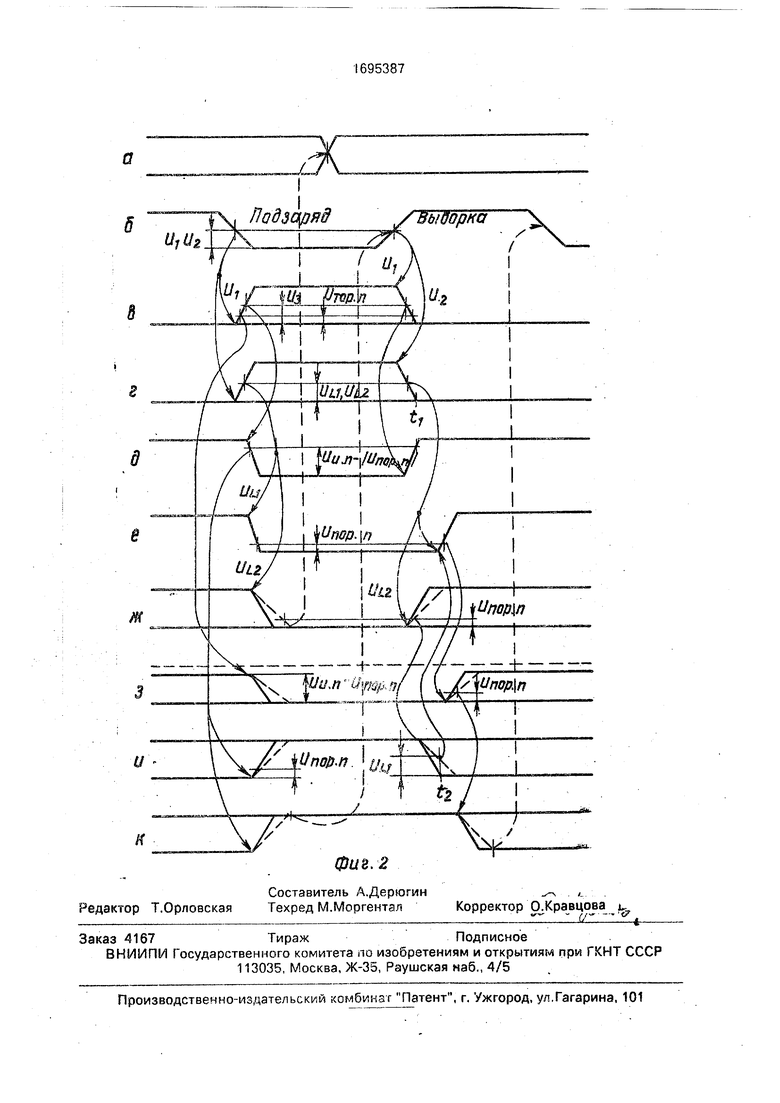

На фиг.1 приведена принципиальная электрическая схема ПЛМ; на фиг.2 - временная диаграмма работы ПЛМ: а - входные информационные сигналы; б - вход разрешения выборки; в - входы запуска блоков подзаряда третьей группы; г - вторые входы блоков установки; д - входы запуска блоков подзаряда первой и второй групп; е - входы запуска буферных усилителей; ж - входы элементов И (пунктир - последний вход); з - входы элементов ИЛИ (пунктир - последний вход); и - выходы элементов И (пунктир - выход последнего элемента); к - выходы элементов ИЛИ (пунктир - выход последнего элемента).

ПЛМ (фиг,1) содержит элементы И 1, элементы ИЛИ 2, блоки подзаряда первой 3, второй 4 и третьей 5 груш , буферные усилители 6, формирователь 7 сигналов выборки, блоки установки 8.

На фиг.1 показаны также вход 9 разрешения выборки, выход готовности 10, информационные входы 11 и выходы 12 ПЛМ, шина 13-напряжения питания и шина 14 нулевого потенциала.

Каждый элемент И 1 имеет входы 15 и выход 16, каждый элемент ИЛИ 2 - входы 1,7 и выход 18.

Каждый блок подзаряда первой 3 и второй 4 групп содержит первый 19 и второй 20 МДП-транзисторы р-типэ, истоки которых соединены с шиной питания 13, стоки являются выходом блока, затвор первого МДП- транзистора - входом запуска, а затвор второго транзистора соединен с шиной нулевого потенциала.

О

о

СП

со

00

VJ

Каждый блок подзаряда третьей группы 5 содержит МДП-транзистор п-тмпа, исток которого соединен с шиной нулевого потенциала, а затаор и сток являются входом запуска и выходом соответственно.

Каждый Буферный уем житель 6 содержит пэраый 21. второй 25 и третий 23 МДП- транзисторь n-гипа, причем затвор транзисторе. 21 и исток транзистора 23 яля- ются информацию;жь.м входом, а затворы траиз стосов S2 и 23 ьходом запуска уси- лигеля, литок транзистора 21 соединен со стоков фанамстора 22, а сток транзистора 23 является заходом усилителя.

Формироьзпгель 7 сигналов выборки состоит ил злегиентз ИЛИ-НЕ 24 и трех элементен HF 25-27. игу.чем сходы первого 25 и второго 26 элементов НЕ являются первым входом формирователя и входом 9 раз- решения выборки устройства, выход элемента НЕ 25 соединен с входом элемента НЕ 27, а выход элемента НЕ 26-с первым входом элемента ИЛИ-НЕ 24. второй вход которого является вторым входом формирователя 28, выходы элементов 25, 27, 24 и 26 являются соответственно первым 29, вторым 30, третьим 31 и четвертым 32 выходами формирователя 7.

Каждмй блох установки 8 выполнен на элемент. УЬ / --НЕ, первый и второй входы коюрого являются соответстаенно первым л вторым входами блока 8.

Цикл работы ПЛ М состоит из двух фаз - подзаряда и выборки. Начало и окончание каждой фазы определяется по фронту сиг- налоз соответственно на входе выборки 9 и выходе готовности 10 ПЛМ. Формирователь 7 формирует необходимую последовате,ло- пость управляющих сигналов в каждой Фазе. В фазе подзаряда ПЛМ приводите в начальное состояние, когда входы 15 ал ментов И и входы 18 элементов ИЛИ одновременно обнуляются при помощи соответственно блоков установки 8 и блоков подзаряда 5, усилители 6 отключаются п происходит одновременный подзаряд выходов 16, 28 элементов А и выходов 18 элементов ИЛИ при помощи блоков ПОДЗУ- ряда соответственно 3 и 4. В фазе выборки блоки подзаряда 3, 4, 5 отключаются и происходит формирование выходного информационного набора на шинах 18 в виде инверсной дизъюнктивно-конъюнктивной фоомы переменных на входах 11. Выборка осуществляется в два этапа: вначале с помощью выбранных блоков установки 8 формируется выходной набор конъюнкций на выходах 16 элементов И, а затем после появления сигнала готовности на выходе 28

последнего элемента И формируется г. помощью усилителей 6 дизъюнкция конъюнкций на выходах 18 элементов ИЛИ, Последние элементы И и ИЛИ, последний

блок установки и последний усилитель выбираются в каждой фазе выборки и моделируют все переходные процессы в соответствующих рабочих блоках ПЛМ, имеющих наибольшую емкость нагрузки.

ПЛМ работает следующим образом.

В начальном состоянии сигнал на входе выборки 9 ПЛМ находится в состоянии логической 1 (фиг.2,6), соответствующем фазе выборки. Сформированный выходной набор

в виде конъю;наивно-дизъюнктивной формы входных переменных установлен на выходах 18 элементов ИЛИ 2. На входах 15 элементов И 1 установлен инверсный набор входных переменных, на входах 17 элементов ИЛИ - наборы конъюнкций входных переменных. При этом на входах 15 элементов И высокий уровень Кип или низкий уровень 0 поддерживается статическим током соответствующих блоков 8 в зависимости от

их выбранного или невыбранного состояния соответственно, На выбранных входах 17 элементов ИЛИ высокий уровень (Кип Unop.n) поддерживается статическим током на выходе соответствующих выбранных уси

жителей 6, а на невыбрзнных входах 17 низкий уровень 0 поддерживается за счет уровня 0 на выходах 16 соответствующих невыбранных элементов И, передаваемого через высокоомный транзистор 23 не выбранных усилителей б. Поскольку последний блок установки 8 и последний усилитель 6 выбираются всегда, то выходы готовности 28 и 10 последних эпементов И и ИЛИ в фазе выборки тоже всегда разряжены, что обеспечивается соответствующим подключением программируемых МДП-транзисторов п-тлпа 33 а этих элементах. Высокий уровень Dun на неразряженных выбранных выходах 16 и 18 элементов И и ИЛИ поддерживается небольшим статическим током высокоомных транзисторов 20 в соответствующих блоках подзарлцч 3 и 4, а уровень 0 на невыбракных выходах iS и 18 обеспечивается статическим током

включенных транзисторов 33 соответствующих элементов. Транзисторы 19 з блоках подзаряда 3, 4, 5 заперты высоким уровнем на выходе 30 формирователя 7 и низким уровнем на его выходе 29 соответственно. 8

усилителях 6 высоким уровнем на выходе 31 формирователя включены транзисторы 22 и аысокоомные траниеторы 23, при этом в выбранных усилителях 0, на информационном входе которых сохраняется высокий уровень, включен транзистор 21 и

уровень(иип Unop.n ) установлен на выходе усилителя,

Фаза подзаряда начинается при переключении на входе 9 сигнала выборки ПЛМ в состояние логического 0. При понижении уровня этого сигнала (фиг,2,б) до порогов переключения Ui и LJ2 элементов НЕ 25 и 26 образуются положительные стробы на выходах 29 и 30 формирователя 7 (фиг,2,в,г). Если уровень строба на выходе 2.9 выше порогового напряжения Unop.n МДП-тран- зистора n-типа, открываются транзисторы блоков подзаряда 5, разряжающие входы 17 элементов ИЛИ (фиг.2,з). Если уровень строба на выходе 30 выше порогов пере- ключения DM и Ui2 элементов ИЛИ-НЕ формирователя 7 и блоков установки 8, происходит обнуление входов 15 элементов И (фиг.2,ж) и запирание транзисторов 22 и 23 усилителей 6 (фиг.2,е) по входам запуска. При дальнейшем повышении уровня строба на. выходе 29 до порога переключения Ua элемента НЕ 27 образуется отрицательный строб на выходе 30 (фиг.2,д), понижение уровня которого до порогового напряжения МДП-транзистора р-типа Dun IUnop.pl вызывает включение транзисторов 19 в блоках 3 и 4. осуществляющих под- заряд выходов 16 и 18 соответственно элементов И и ИЛИ до высокого уровня Unn (фиг.2, и,к). При этом открываются транзисторы 21 усилителей 6. Поскольку входы каждого элемента И имеют емкость нагрузки, то разряд последнего входа, к которому подключается нэибопьшая входная нагруз- ка (фиг.2, ж - пунктир), свидетельствует об окончании процесса установки всех входов 15 в нулевое состояние и является разрешением к смене входных информационных сигналов на входах 11 ПЛМ (фиг.2,а). В саою очередь, поскольку выходы каждого элемента ИЛИ также имеют емкость нагрузки, то подзаряд выхода 10 последнего элемента ИЛИ с наибольшей емкостью нагрузки (фиг.2, к-пунктир) свидетельствует об окончании процесса подзаряда элементов ИЛИ и готовности всей ПЛМ к фазе выборки.

Таким образом, в фазе подзаряда последовательность стробов на выходах 29,32 и 31 обеспечивает вначале блокировку элементов М и ИЛИ по входам (фиг.2, з,ж) и блокировку буферных усилителей 6 по входам запуска (фиг.2,е), а затем с минимальной задержкой, определяемой перепадом (U3-Ui i(2) ), по стробу на выходе 30 включаются транзисторы подзаряда 19 в блоках 3 и 4 (фиг,2,д). За счет этого повышается быстродействие ПЛМ в фазе подзаряда.

Фаза выборки ПЛМ начинаете0 np-,i пе реключении управляющего сигнала ча пхо- де 9 в состояние логической 1. После достижения им порогов переключения Ui и U2 элементов НЕ 25 и 26 (фиг.2.о) образуются отрицательные стробы на выходах 29 и 32 формирователя 7 (фиг,2, в.г). При уровне строба на выходе 29 ниже порога переключения из элемента НЕ 27 образуется положительный строб на его выходе 30 (фиг 2.д). при достижении которым уровня (Una - IUnop.pl закрываются транзисторы подзаряда 19 в блоках 3 и 4. При понижении уровня строба на выходе 32 до порога переключения выбранные блоки установки 8, на информационных входах 11 которых к этому времени установлено новое знамение входной переменной разное 0, подзаряжают выбранные входы элементов И до уровня Uwi, формируя инверсный набор переменных на входах 15(фиг.2,ж). Элемент ИЛИ НЕ формирователя, не изменяя состояния своего выхода 31, с момента времени ц (фиг.2,г) устанавливается в режим ожидания окончания выборки элементов И. При дальнейшем понижении уровня строба на выходе 29 (ниже Unop.n) закрываются транзисторы в блоках подзаряда 5. При уровне на выбранных входах 15 выше Unop п (фиг.2.ж) разряжаются выходы невыбранных элементов И (фиг.2.и). Выходы выбранных элементов И остаются в пассивном высоком уровне, поддерживаемом небольшим статическим током высокоомного транзистора 20 в блоках подзаряда 3. При этом всегда последний вход элементов И подзаряжается, а выход последнего, элемента И разряжается не быстрее, чем соответственно любой другой вход и выход аюбого элемента 11 вследствие подключения к этим узл.-м наибольших емкостей нагрузки. Поэтому рязряд выхода готовности последнего элемента И, т.е. входа 28 формирователя 7 (фиг.2, и-пунктир), свидетельствует об окончании выборки элементов И. При понижении ровня на входе 28 до порога переключения Uu элемента ИЛИ- НЕ 24 формирователя (фиг.2, и. момент времени t2) образуется положительный строб запуска буферных усилителей (фиг.2.е), открывающий з них транзисторы 22 и 23. Выбранные усилители 6, нз входе которых поддерживается высокиЛуровень, подзаряжают соответствующие входы 17 элементов ИЛИ до уровня (Unn -Unop.n). реализуя таким образом с помощью транзисторов 21 и 22 функцию логическое И относительно информационного сигнала на выходе 16 и сигнала запуска на выходе 31. Открывающиеся высокоомные транзисторы 23 имеют небольшую проводимость, необходимую

для исключения перераспределения заряда между подзаряжающимся выходом выбранного усилителя и его высоким входом в момент запуска и одновременно достаточную для поддержания низкого уровня на выходе невыбранных усилителей от низкого уровня на соответствующем входе. Таким образом, набор конъюнкций входных переменных на входах 11 передается с помощью буферных усилителей 6 с выходов 16 элементов И на входы 17 элементов ИЛИ. При уровне на выбранных входах 17 выше Unop.n (фиг,2,з) разряжаются выходы невыбранных элементов ИЛИ (фиг.2,к). Выходы выбранных элементов ИЛИ остаются на высоком уровне, поддерхедваемом небольшим статическим током высокоомиого транзистора 20 в блоках подзаряда 4. При этом всегда последний вход элементов ИЛИ подзаряжается, а выход последнего элемента ИЛИ разряжается не быстрее, чем соответственно любой другой вход и выход любого элемента ИЛИ вследстаие подключения к этим узлам наибольших емкостей нагрузки. Поэтому разряд выхода готовности 10 последнего элемента ИЛИ (фиг,2, к-пунктир) свидетельствует об окончании процесса выборки элементов ИЛИ и ПЛМ в целом.

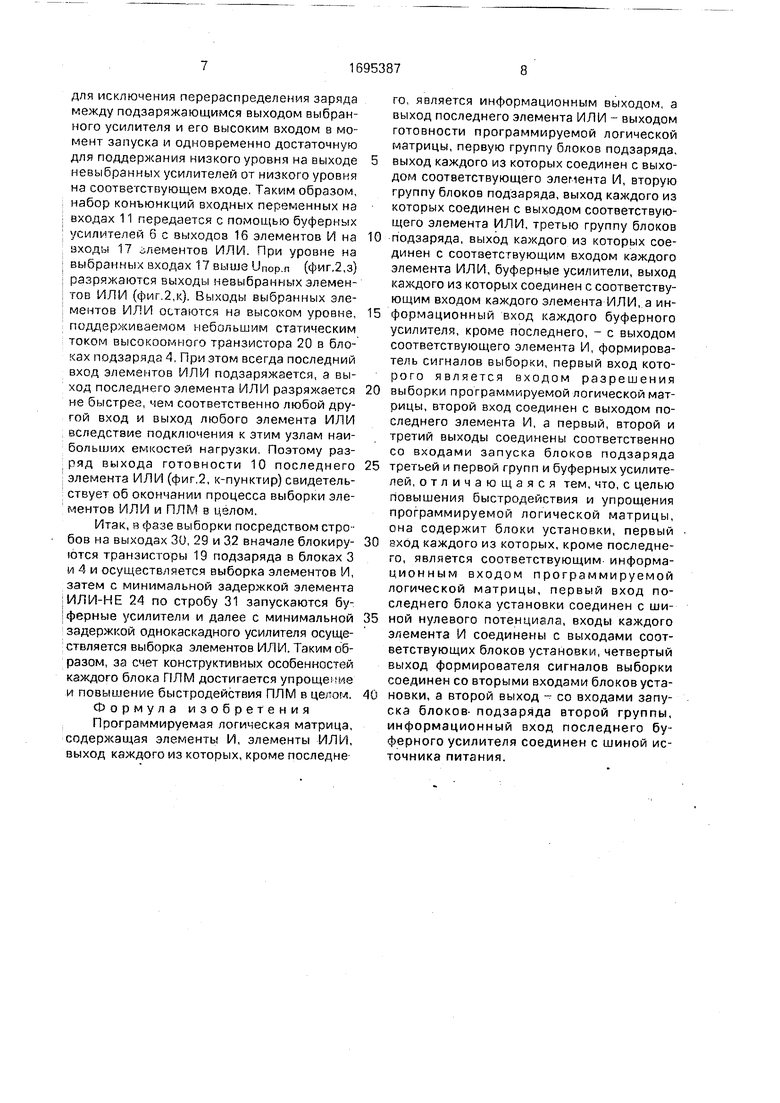

Итак, я фазе выборки посредством стробов на выходах 30, 29 и 32 вначале блокируются транзисторы 19 подзаряда в блоках 3 и 4 и осуществляется выборка элементов И, затем с минимальной задержкой элемента ИЛИ-НЕ 24 по стробу 31 запускаются буферные усилители и далее с минимальной задержкой однокаскадного усилителя осуществляется выборка элементов ИЛИ. Таким образом, за счет конструктивных особенностей каждого блока ПЛМ достигается упрощение и повышение быстродействия ПЛМ в целом. Формула изобретения Программируемая логическая матрица, содержащая элементы И, элементы ИЛИ, выход каждого из которых, кроме последне

го, является информационным выходом, а выход последнего элемента ИЛИ - выходом готовности программируемой логической матрицы, первую группу блоков подзаряда,

выход каждого из которых соединен с выходом соответствующего элемента И, вторую группу блоков подзаряда, выход каждого из которых соединен с выходом соответствующего элемента ИЛИ, третью группу блоков

подзаряда, выход каждого из которых соединен с соответствующим входом каждого элемента ИЛИ, буферные усилители, выход каждого из которых соединен с соответствующим входом каждого элемента ИЛИ, а информационный вход каждого буферного усилителя, кроме последнего, - с выходом соответствующего элемента И, формирователь сигналов выборки, первый вход которого является входом разрешения

выборки программируемой логической матрицы, второй вход соединен с выходом последнего элемента И, а первый, второй и третий выходы соединены соответственно со входами запуска блоков подзаряда

третьей и первой групп и буферных усилителей, отличающаяся тем, что, с целью повышения быстродействия и упрощения программируемой логической матрицы, она содержит блоки установки, первый

вход каждого из которых, кроме последнего, является соответствующим информационным входом программируемой логической матрицы, первый вход последнего блока установки соединен с шиной нулевого потенциала, входы каждого элемента И соединены с выходами соответствующих блоков установки, четвертый выход формирователя сигналов выборки соединен со вторыми входами блоков установки, а второй выход - со входами запуска блоков- подзаряда второй группы, информационный вход последнего буферного усилителя соединен с шиной источника питания.

Фиг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1989 |

|

SU1695383A1 |

| Каскадное устройство ортогонального типа для сдвигов многоразрядных операндов | 1989 |

|

SU1661757A1 |

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1615728A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1795521A1 |

| Коммутационное устройство | 1985 |

|

SU1307572A1 |

| Устройство управления газоразрядной индикаторной панелью | 1989 |

|

SU1709388A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении микропроцессоров и микроЭВМ в качестве постоянной памяти типа ПЛМ. Предложенная ПЛМ обладает повышенным быстродействием за счет совмещения во времени процесса активизации элементов, осуществляющих данную фазу цикла, с процессом блокировки элементов, осуществляющих противоположную фазу. и за счет минимальной задержки перехода от выборки элементов И 1 к, выборке элементов ИЛИ 2. Кроме того, достигается значительное упрощение ПЛМ за счет уменьшения аппаратурных затрат во вспомогательных блоках, в том числе за счет применения однокаскадного буферного усилителя 6, 2 ил.

и

ZW jfyf-ж

- I fir

| Авторское свидетельство СССР N° 3145911,кл.С 11 С 19/00, 1985 | |||

| Авторское свидетельство СССР № 1424598,кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-11-30—Публикация

1989-03-30—Подача