1

(21)4694769/24 1

(22)23.05.89

(46) 15.03.91. Бюл. № 10

(72) В.П.Горский, Е.И.Мироненко

и С.С-.Коваленко

(53)681.327.6 (088.8)

(56)Neil Н.Е. Weste et al. Princip- les of CMOS VLSI Design. - Addison - Wesley, 1985, p. 371.

Там же, с. 373.

(54)ДИНАМИЧЕСКАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА

(57)Изобретение относится к вычислительной технике и может быть использовано в интегральных схемах на

КМОП-транзисторах. Целью изобретения является упрощение динамической программируемой логической матрицы. Матрица содержит элемент синхронизации на транзисторе 11 с соответствующими связями. Транзистор И формирует сигнал, разрешающий передачу информации из матричного блока И 8 через элементы 10 согласования в матричный блок ИЛИ 9 только после того, как на выходах блока 8 появится информация. При этом одного элемента синхронизации на транзисторе 11 достаточно для осуществления синхронизации всех элементов 10 согласования. 2 з.п. ф-лы, 4 ил.

С

S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь импульсов | 1985 |

|

SU1374417A1 |

| Программируемая логическая матрица | 1989 |

|

SU1695387A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Формирователь импульсов | 1985 |

|

SU1374416A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Устройство для выборки информации из матричного накопителя | 1982 |

|

SU1073796A1 |

со ел

ю

Изобретение относится к вычислительной технике и может быть использовано в интегральных схемах на КМОП-транэисторах.

Целью изобретения является упрощение динамической программируемой матрицы.

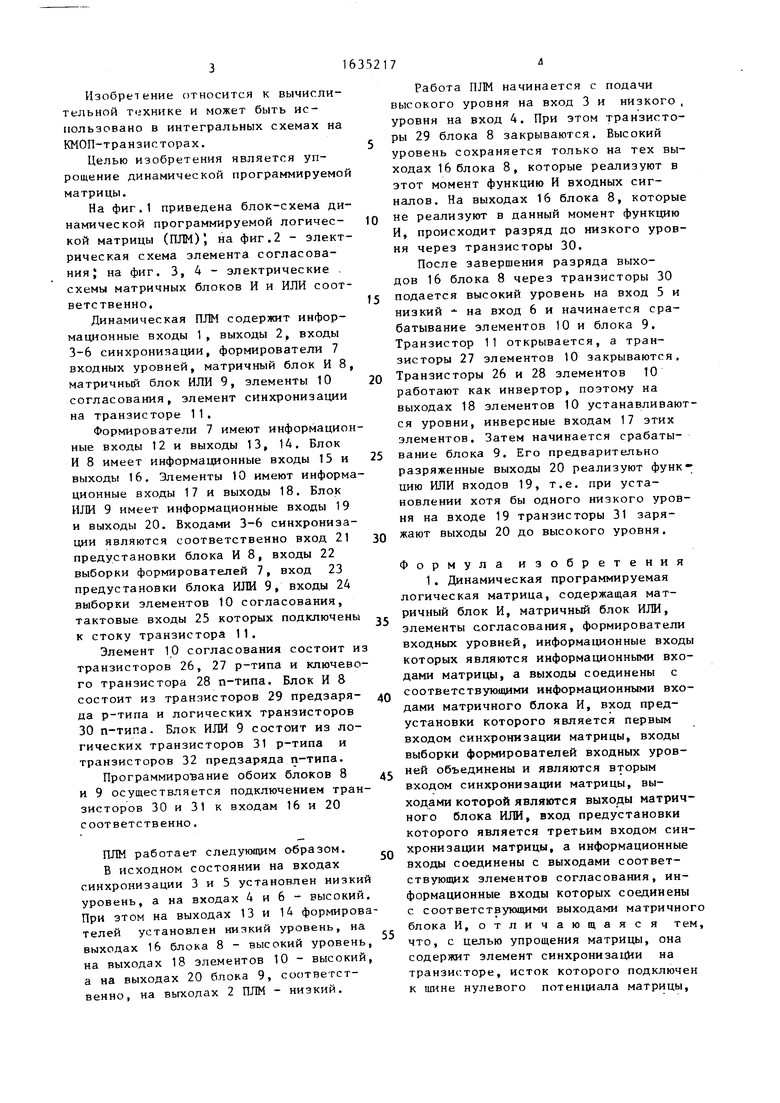

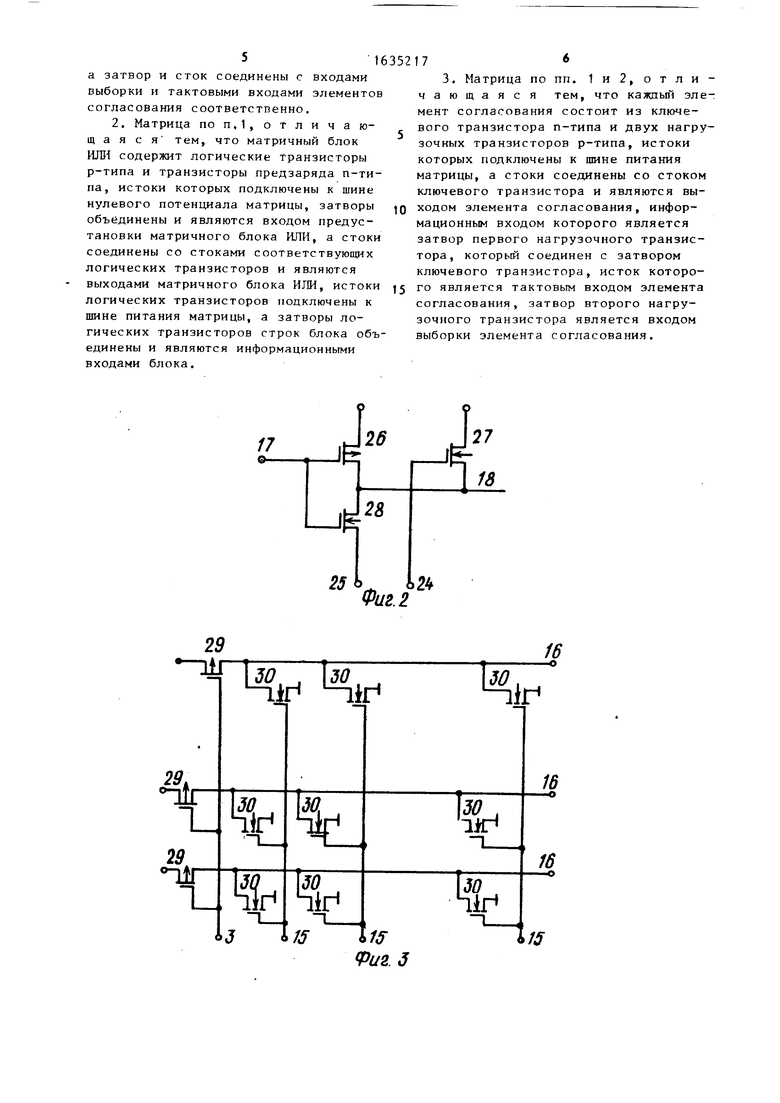

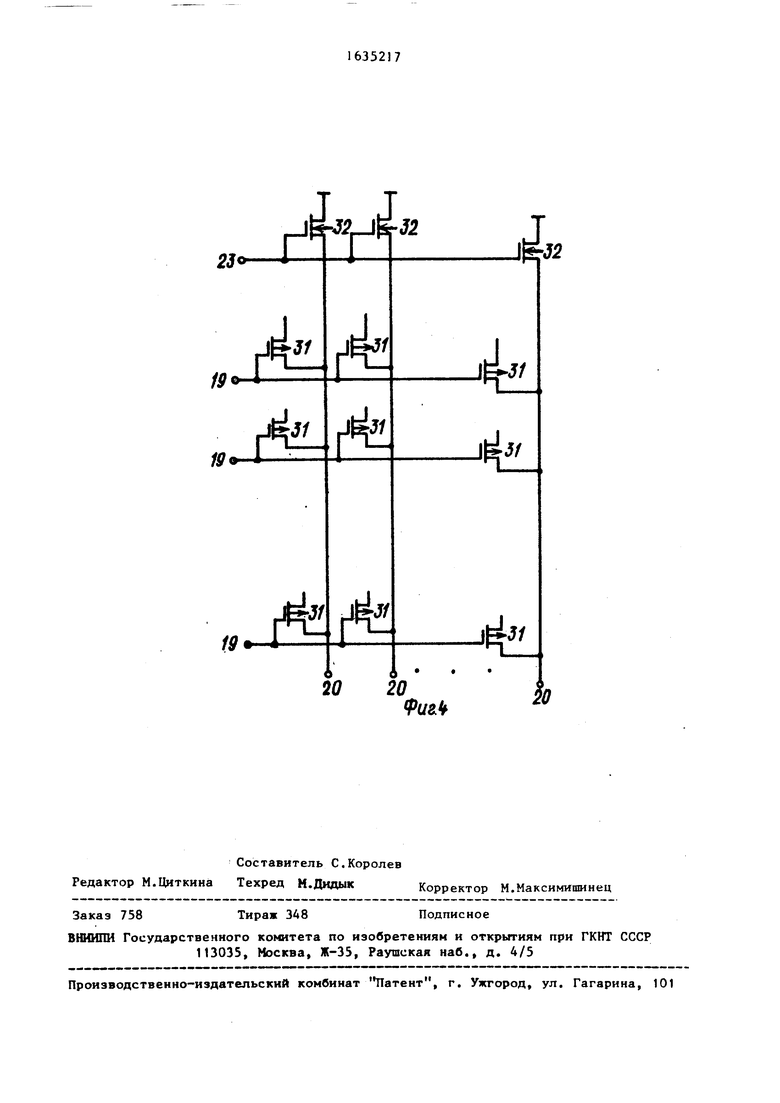

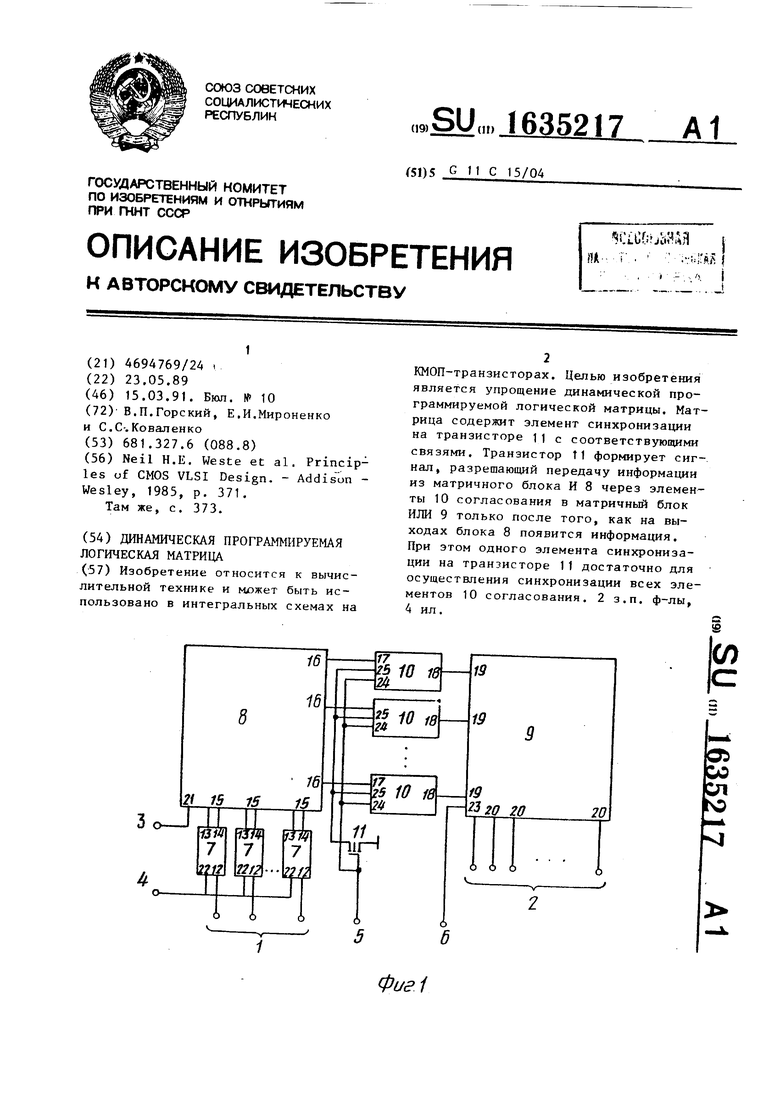

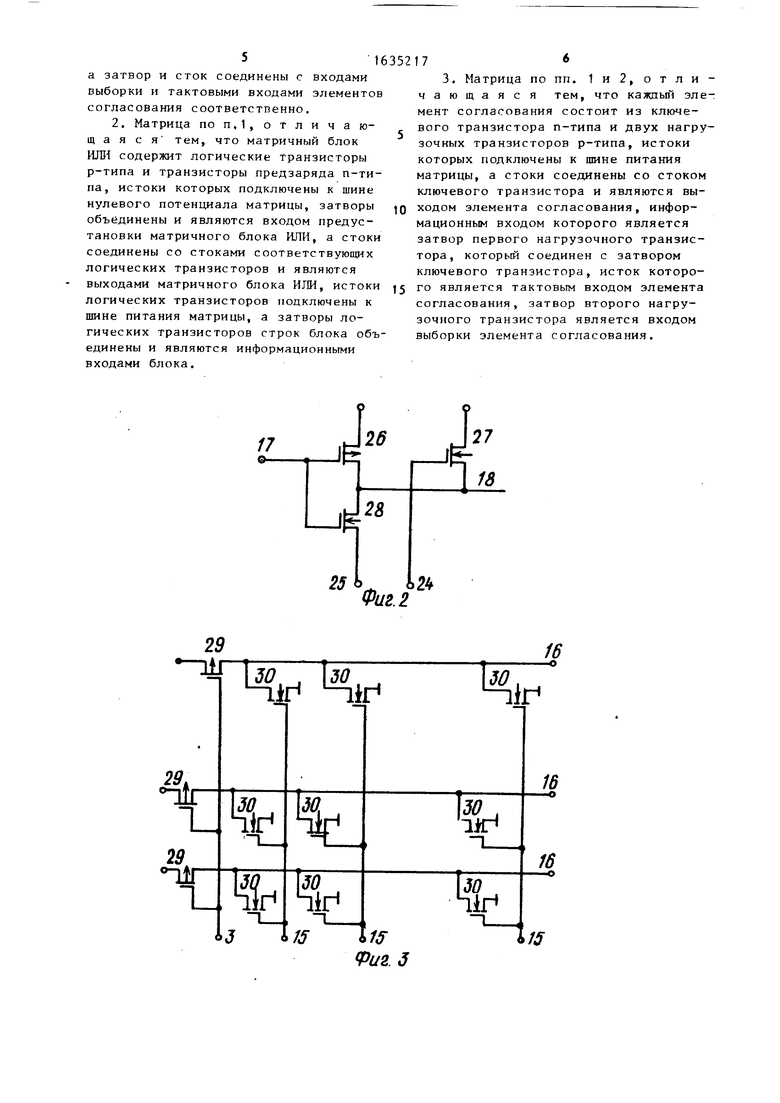

На фиг.1 приведена блок-схема динамической программируемой логичес- кой матрицы (ПЛМ) на фиг.2 - электрическая схема элемента согласования; на фиг. 3, 4 - электрические схемы матричных блоков И и ИЛИ соответственно.

Динамическая ПЛМ содержит информационные входы 1, выходы 2, входы 3-6 синхронизации, формирователи 7 входных уровней, матричный блок И 8, матричный блок ИЛИ 9, элементы 10 согласования, элемент синхронизации на транзисторе 11.

Формирователи 7 имеют информационные входы 12 и выходы 13, 14. Блок И 8 имеет информационные входы 15 и выходы 16. Элементы 10 имеют информационные входы 17 и выходы 18. Блок ИЛИ 9 имеет информационные входы 19 и выходы 20. Входами 3-6 синхронизации являются соответственно вход 21 предустановки блока И 8, входы 22 выборки формирователей 7, вход 23 предустановки блока ИЛИ 9, входы 24 выборки элементов 10 согласования, тактовые входы 25 которых подключены к стоку транзистора 11.

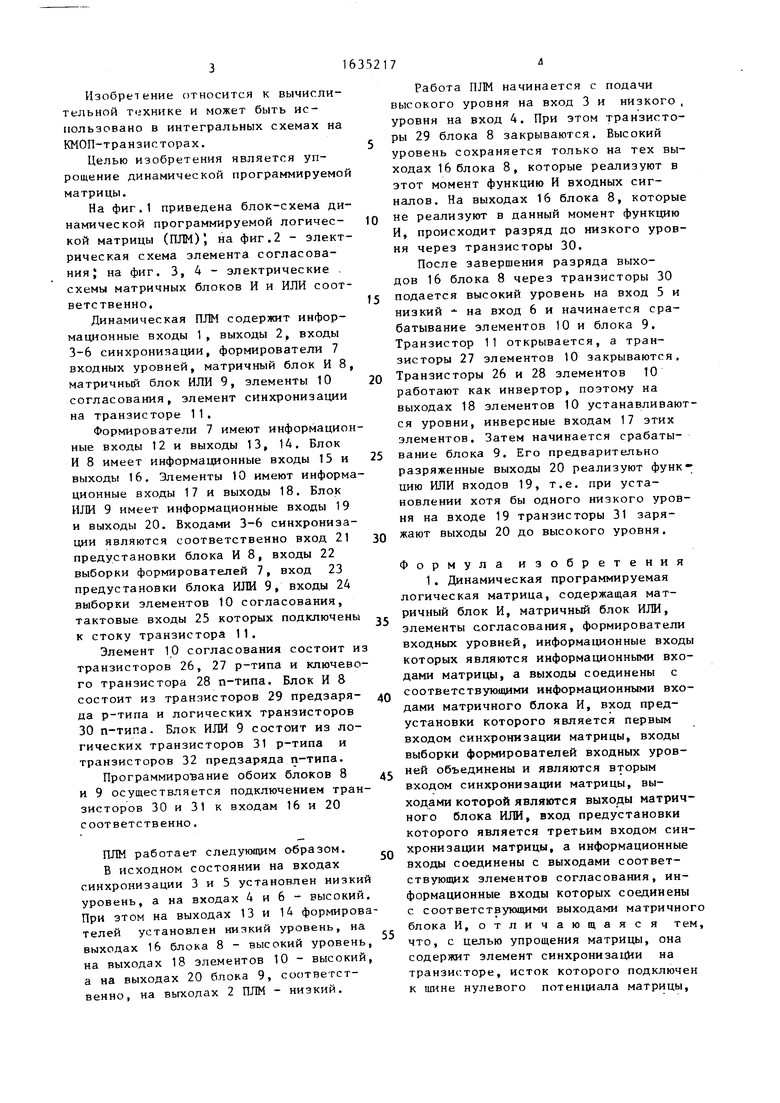

Элемент 10 согласования состоит и транзисторов 26, 27 р-типа и ключевого транзистора 28 n-типа. Блок И 8 состоит из транзисторов 29 предзаря- да р-типа и логических транзисторов 30 n-типа. Блок ИЛИ 9 состоит из логических транзисторов 31 р-типа и транзисторов 32 предзаряда п-типа.

Программирование обоих блоков 8 и 9 осуществляется подключением транзисторов 30 и 31 к входам 16 и 20 соответственно.

ПЛМ работает следующим образом.

В исходном состоянии на входах синхронизации 3 и 5 установлен низкий уровень, а на входах 4 и 6 - высокий. При этом на выходах 13 и 14 формирователей установлен низкий уровень, на выходах 16 блока 8 - высокий уровень, на выходах 18 элементов 10 - высокий, а на выходах 20 бпока 9, соответственно, на выходах 2 ПЛМ - низкий.

0 ,

о

5

0

Работа ПЛМ начинается с подачи высокого уровня на вход 3 и низкого , уровня на вход 4. При этом транзисторы 29 блока 8 закрываются. Высокий уровень сохраняется только на тех выходах 16 блока 8, которые реализуют в этот момент функцию И входных сигналов. На выходах 16 блока 8, которые не реализуют в данный момент функцию И, происходит разряд до низкого уровня через транзисторы 30.

После завершения разряда выходов 16 блока 8 через транзисторы 30 подается высокий уровень на вход 5 и низкий - на вход 6 и начинается срабатывание элементов 10 и блока 9. Транзистор 11 открывается, а транзисторы 27 элементов 10 закрываются. Транзисторы 26 и 28 элементов 10 работают как инвертор, поэтому на выходах 18 элементов 10 устанавливаются уровни, инверсные входам 17 этих элементов. Затем начинается срабатывание блока 9. Его предварительно разряженные выходы 20 реализуют функцию ИЛИ входов 19, т.е. при установлении хотя бы одного низкого уровня на входе 19 транзисторы 31 заряжают выходы 20 до высокого уровня.

Формула изобретения

516

а затвор и сток соединены с входами выборки и тактовыми входами элементов согласования соответственно.

17

Фиг. 3

20 20

Составитель С.Королев Редактор М.Циткина Техред М.Дидык Корректор М.Максимишинец

Заказ 758

Тираж 348

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг.Ь

20

Подписное

Авторы

Даты

1991-03-15—Публикация

1989-05-23—Подача