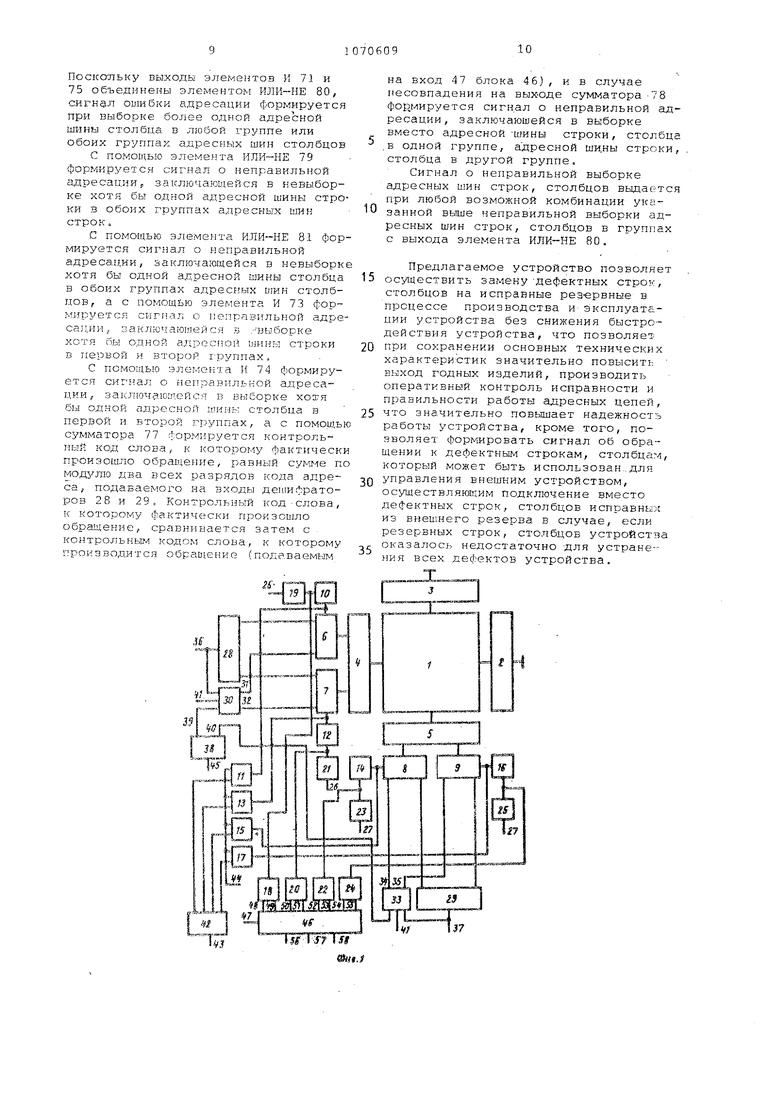

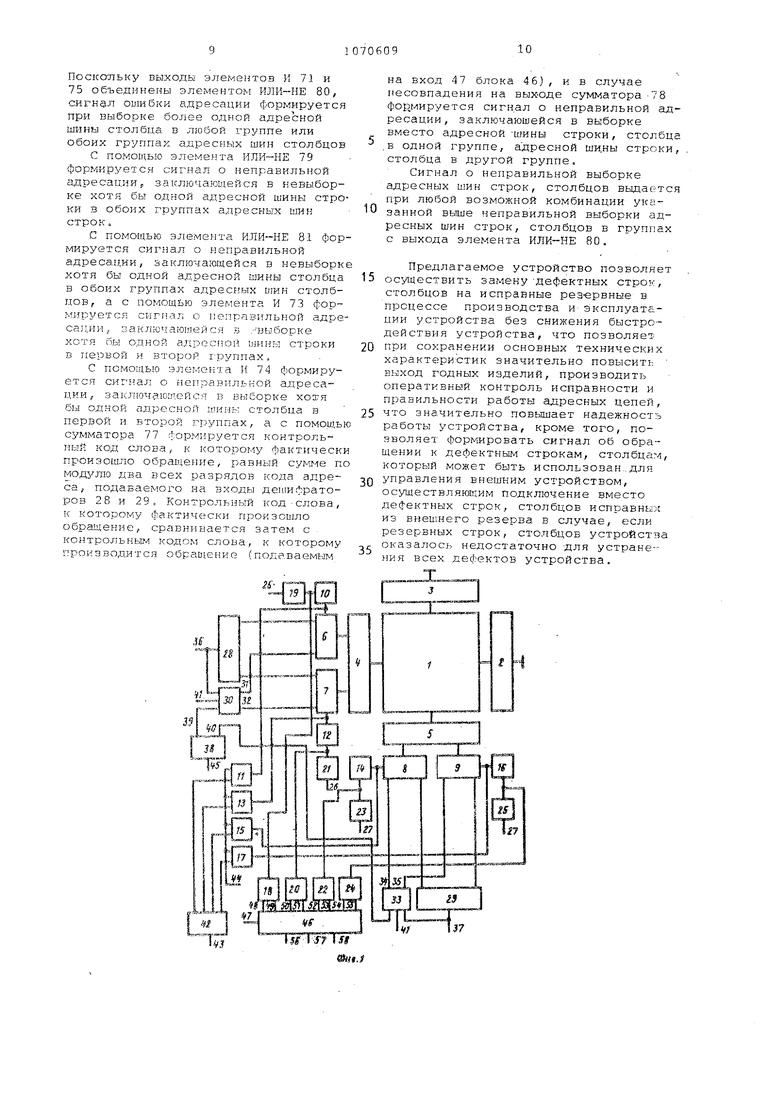

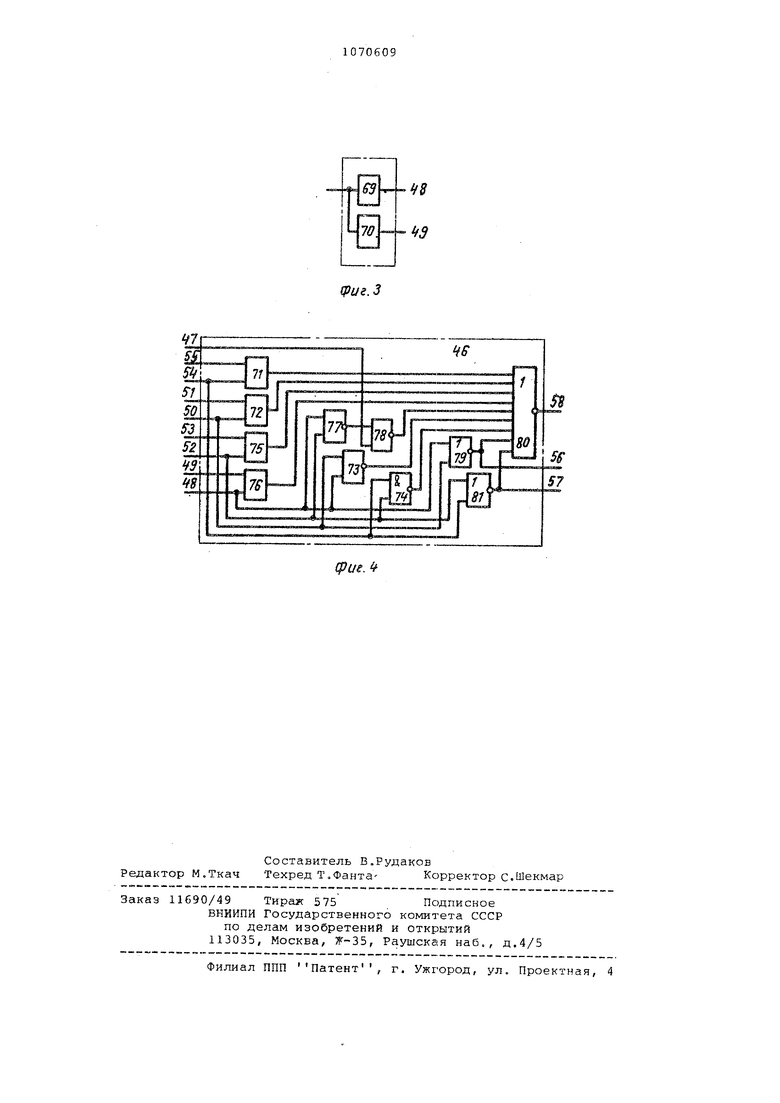

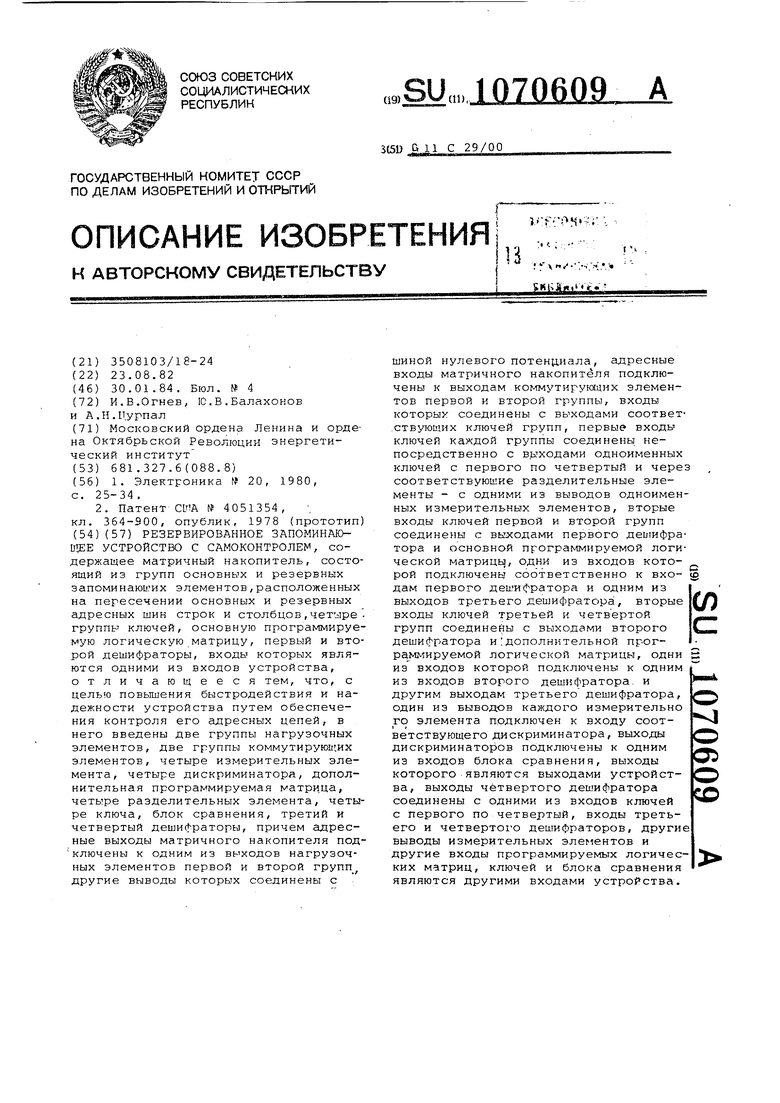

Изобретение относится к вычислительной технике, в частности к запо ivSHHaiQiUHM устройствам, и может быть использовано в системах дискретной обработки информации, в в:оторых предъявляются повьииенные требования к надежности,, Известны запоминающие устройства с самоконтролем правильности работы тракта дешифрации ,осуществляемым методом шифрации выбранных адресных шин контрольный код адреса по некоторому нодулго, сравниваемый затем с внешним контрольным кодом адреса по тому же модулю, Основными недостатками известных устройств являются большая аппарату ная избыточность и малое быстродейст вие, являющиеся следствием сложности шифратора Известно запоминаюи ее устройство с резервированием дефектных столбцов запоминаю1 Р х элементов, содержащее матричный накопитель, имеющий основные и резервные запоминающие элемент схему сравнения адресов, коммутирую7 щие схемы с плавкими перег-тычками, ключи выборки основных и резервных столбцов . Недостатками известного устройства являются отсутствие оперативного контроля правильности работь) адресных цепей в процессе работы, замена дефектного столбца на исправньтй резервный невозможно при отказах ключей выборки столбцов типа стоянная единица , не предусмотрена замена строк дефектных запоминающих элементов на нсправггые резервные. На.иболее близким техническим реше нием к предлагаемому является резерв рованное запоминающее устройство с самоконтролем, содержащее накопитель состоящий из основных и резервных зпоминающих элементов, дешифраторы выборки основных строк и столбцов запоминающих элементов, ключи выборки основных и резервных с-трок, стол цов запог«и-1На:ОИ.их элементов, программируемую логическую матрицу. Принцип действия устройства состоит в записи и хранении информации об адресах дефектных запоминающих элементов в п:poгpa флнpyeмoй логической матрице (ПЛМ). При работе устройства адресаp по которым .производится обращение, подаются на входы ПЛМ и, если адрес, по которому производитс обращение, записан в ПЛМ, то на выходе ПЛМ формир1Татся сигналы, запрей ающие выборку дефектного запоминающего элемента и подключающие исправный резервный запоминающий элемент к входам-выходам устройства С2,1, Наиболее существенными недоста - нами известного устройства являются усложнение .логических схем вводавывода информации из накопителя и схем обрамлер)ия накопителя, отсутствие оперативного контроля правильгюсти работы адресных цепей во время обраь.ения, необходимость адресации каждого деф-ектногс запоминающего элемента, что приводит к усложнению структуры ПЛМ и увеличивает аппаратурНЕГй объем ПЛМ-. Указанные недостатки снижают надежность устройства, Цель изобретения - повьшение быстродействия и надежности запоминающего устройства путем обеспечения контроля его адресных цепей. Поставленная цель достигается тем, что в резервированное запоминающее устройство самоконтролем, содержащее матричный накопитель, сосТОЯ1ЦИЙ из групп основных и резервных запоминающих элементов, располсженHfjx на пересечении основных и резервных адресных шин строк и столбцов, четыре группы ключей, основную )0граммируемую логическую матрицу, первый и второй дешифраторы, входы которьлх являются одними из входов устройг;тва, введены группы нагрузочных элементов, две группы коммутирушь-дих элементов, четыре измерительных элемента, четыре дискриминатора, дополнительная программируемая матрице, четыре разделительных элегу1ента, четыре ключа, блок сравнения, третий и четвертый .цешкфраторы,, причем адресные выходы матричного накопителя подключены к одним КЗ выводов на)рузочных эле vieHTO3 первой и второй групп, другие выводы которых соединены с игиной нулевого потенциала, адресные входы г атричного накопителя подключены к выходам коммутирующих элементов первой и второй групп, входы которых соединены с выходами соответствующих ключей групп, первые входы ключей каждой группы соединены непосредственно с выходами одноименных ключей с первого по четвертый и через разделительные элементы - с одними из выводов одноименных измерительны ; элементов, вторые входы ключей первой и второй групп соединены с выходами первого дешифратора и основной программируемой логической матрицы, одни из входов которой подключены соответственно к входам первого дешифратора и одним из выходов третьего дешифраторе, вторые входы ключей третьей и четвертой групп соединены с выходами второго дешифратора и дополнительной програгФ1ируемой логической матрицы одни из входов которой подключены к одним из входов второго дешифратора и другим выходам третьего дешифратора, один из выводов каждого измерительного элемента подключен к входу соответствукщего дисjicpHMHHaTOpa, выходы дискриминаторов подкл.ючены к одним из входов блока сравнения, выходы которого являются выходами устройства, выходы четвертого дешифратора соединены с одними из входов ключей с первого по четвертый, входы третьего и четвертого дешифраторов, другие вы.воды измерительных элементов и другие входы программируемых логических матриц,, ключей и блока сравь;ения являются другими входами устройства На фиг, 1 изображена структурная схема устройства; на фиг. 2 - то же программируемой логической матрицы; на фиг. 3 - то же, дискриминатора; на фИГ. 4 - то же, блока сравнения. Устройство (фиг. ) содержит матричный накопитель 1, состоящий из групп основных и резервных .запоминающих элементов (не показаны), расположенных на пересечении основных и резервных адресных шин строк и столбцов, первую 2 и вторую 3 группы нагрузочных элементов, в качестве которых могут быть использованы резисторы, первую 4 и вторую 5 группы коммутирующих элементов, в качестве которых могут быть использованы плав кие перемычки, пережигаег-гые повышенным током, первую б и вторую 7 группы. ключей , служащих соответственно для выборки основных и резервных строк, первой и второй групп накопителя 1, третью 8 и четвертую 9 группы ключей, служащих соответственно для выборки основных и резервных столбцов первой и второй групп накопителя 1, первые разделительный элемент 10 и ключ 11, вторые разделительный элемент 12 и ключ 13, третьи разделительный элемент 14 - и ключ 15, четвертые разделителы-гый элемент 16 и ключ 17(в качестве разделительных элементов 10,12,14 и 16 могут быть использованы полупроводниковые диоды), первые дискри г инатор 18 и измерительный элемент 19, вторые дискриминатор 20 и измер тельный элемент 21, третьи дискрими натор 22 и измерительный элемент 23, четвертые дискриминатор 24 и из мерительный элемент 25 (в качестве измерительных элементов 19,21,23 и 25 могут быть использованы резисторы) . Элементы. 19 и 21 имеют входы 26, элементы 23 и 25 - входы 27. Устройство содержит первый 28 и второй 29 дешифраторы, служащие соответственно для выбора основных стро и столбцов накопителя 1, основную программируемую матрицу 30 с выходами 31 и 32, дополнительную программируемую матрицу 33 с выходами .34 и 35. Дешифраторы 28 и 29 имеют вход 36 и 37 соответственно. Устройство содержит третий дешифратор 38 с выходами 39 и 40. Матрицы 31 и 34 име ют вход 41. Устройство содержит че вер.тый дешифратор 42 с входом 43. Один ИЗ входов ключей 11,13,15 и 17 объединены и подключены i входу 44 устройства. Дешифратор 39 имеет вход 45. Устройство содержит блок 46 сравнения, имеющий входы 47.-55 и выходы 56-58. Программируемые логические матрицы 30 и 33 могут выполняться на основе различной элег-1ентной базы, иметь разнообразную организацию. Например, программируемая логическая матрица (фиг. 2) состоит из схем 59 записи «сода а.дреса резервной строки (столбца), число которых равно числу резервны.х строк (столбцов) , а каждая схема 59 записи ко..иа адреса резервной строки (столбца) , в свою очередь, состоит из схем 60 записи разрядов кода адреса, число которых, равно числу разрядов в коде адреса основной строки (столбца) накопителя 1 и элемента ИЛИ-НЕ 61. Каждая схема 60 заппс.и разря.да кода адреса резервной (столбца) , в свою очередь, состоит из ключевых транзисторов 62 и 63 диода 64, трапз 1сторов 65 и 66 и плав1 их перемычек 67-68. Каждый из дискриминаторов 18, 20,24 и 26 может быть выполнен на основе двух пороговых усилителей 69 и 70 с разными урон нями срабатывания (фиг. 3). Блок 46 сравнения содержит (фиг.4) элементы И 71-76, сумматоры 77 и 78 по модулю два и элементы ИЛИ-НЕ 7981. Устройство работает следующим об.разом. Р устройстве осуществляется оператив11Ьй аппаратный контроль правильНООТ51 работы адресных цепей во время обращения, а, кроме того,предусмотрен режим замены з.апо инающих элементов матричного накопителя 1, к которым ста -ЮБитс51 незозьюжньтм нормальное обращение вс.1сд.ствче технологических дефектов и отказов элементов и связей, возникших в процессе эксплуатации, на исправь;ые резервные отроки и столбцы запоминающих элементов . Режим замены дефектных запоминающих элементо..в, к которым становится невозможным нормальное обращение на исправные резервные, может состоять из нес ольких этапов, число которых определяется типом неисправно.сти числом дефектных строк, столбцов запоминающих элементов, которые-требуется заменить. В процессе работы устройства производятся его контроль и диагностика с целью обнаружения и локализации всех дефектных- запоминающих элементов. Для обнаружения и локализации дефектных запоминанвдих элементов, возникающих в процессе эксплуатации устройства, проводятся дополнительные контроль и диагностика, проведение которых облегчается и упрощается

наличием оперативного контроля правильности работы адресных цепей устройства во время обращения.

В случае обнаружения дефектов, приводящих к неправильной работе дешифраторов, запоминающих элементов, ключей выборки, строк, столбцов, усилителей считывания и т.д., производится отключение дефектной строки (столбца) и подключение исправной резервной о Порядок замены дефектных строк, столбцов одинаков при технологических дефектах и отказах во время эксплуатации.

Один из наиболее сложных случаев, когда вместе с правильно выбранной адресной шиной строки, столбца выбираются дополнительные адресные шины строк, столбцов. Пусть, например , в.результате дополнительных контроля и диагностики определено, что при обращении по некоторому коду адреса, который в последугадем будем называть кодом .адреса дефектной строки,-совместно с правильно выбираемой адресной шиной строки первой группы дополнительно выбираются: одна адресная шина строки первой группы и одна адресная шина стро ки во второй группе с Для отключения дефектных строк на входы устройства необходимо подать следунацие управляющие сигналы и потенциалы: на вход 36 дешифратора 28 код адреса дефектной строки, на вход 43 дешифратора 42 код группы,- в которой требуется отключить дефектную адресную шину строки, а на входы ключей 11,-13,15, 17 со входа 44 подается потенциал программирования,, По коду группы, в которой требуется отключить дефект ную строку, на соответствующем выходе дешифратора 42 формируется разрешгиощий потенциал, открывающий один из ключей 11,ЛЗ,15,17 и потенциал програг/ширования через соответствующий открытый ключ поступает на входы соответствующих ключей 6-9. Если ключи 6-9, соответсвуквдие дефектным строкам, открыты то через них протекает повьгшенннй ток, который вызывает переключение коммутирующих элементов 4 данных строк, например, пережиганием плавких перемычвк повышенным током. Для выборки, например, нескольких адресных шин строк нужно подать на вход 43 дешифратора 42 код первой группы адресных шин строк, а затем по окончании пережигания, плавких перемычек в первой группе адресных щин строк, подать на вход 43 дешифратора 42 код второй группы адресных шнн строк. Указанная очередность подачи кодов групп адресных шин строк на вход 43 дешифратора 42 не является обязательной .И может быть изменена на обратную.

По окончании пережигания плавких перемычек в первой и второй группгзх адресных шин строк с входа 36 дешифратора 28 снимается код адреса дефектной строки, а с входа 43 дешифра5 тора 42 - код группы, в которой проводилось отключение дефектных адресных шин строк, после -чего проводятся дополнительные контроль и дагностика для определения правильности отклю0 чения дефектных адресных шин строк

и определения кода адреса отключемных адресных шин строк. После проверки правильности отключения адресных г-пин строк и определения кода адреса отклю

5 (ценных адресных шин строк с целью

Подключения вместо отключенных адресных шин строк исправных резервных

на входы устройства подаются следующие управляющие сигналы и потенциа0 лы: на вход 36 дешифратора 28 код адреса откл оченной адресной шины строки, на вход 45 первого дополнительного дешифратора 39 код неподключенной резервной адресной шины

5 строки,, в группе, к которой относится отключенная адресная шина строки, на вход 41 -- потенциал программирования и опорное напряжение. По коду неподключенной резервной адресной

0 шины строки, подаваемому на вход 45 дешифратора 39- на одном из его выходов формируется потенциал, разрешающий запись кода адреса отключенной адресной шины строки в програк5 мируемую логическую- матрицу 30. Разрешающий потенциал с выхода 39 дешифратора 38 подается на схему 59 записи кода адреса соответствующей резервной адресной шины строки в

л которой он открывает ключевые транзисторы 62 и 63 во всех схемах 60 записи разрядов кода адреса. Потен циал программ11р6вания с соответствующего входа 41 пpoгpa vDv:Иpyeмoй логической матрицы 30 через 1 лючевые

транзисторы 62 и 63 поступает на транзисторы 65 и 66 в каждой схеме 60 записи. В зависимости от значения разряда кода адреса отключенной адресной шины строки - нуль или едини0 ца,- в схеме 60 записи каждого разряда кода адреса пережигается перемычка 67 или 68 и тем самым код адреса отключенной адресной шины строки записывается в програьд ируемую

5 логическую матрицу 30. После оконча- нкя пережигания плавких перемычек в Програм1 1ируемой логической матрице 30 с входа дешифратора 39 снимается код неподключенной резервной адресной

Q вшны строки, а е входа дешифратора 26 - код адреса отключенной адресной шины строки, после чего таким же образом осуществляется запись в програйгугируемую логическую матрицу 30 кода адреса следующей отключенной адресной шины строки и т.д. до тех пор, пока коды адреса всех отключенных адресных имн строк не будут запи саны в программируемую логическую матрицу 30. При последующей работе в случае обращения по коду адреса отключенной адресной шины строки в схеме 59 записи, в которую записан данный код адреса, по опорному напряжению на выходах составляквдих схем 60 записи формируются нулевые уровни, постуЛающи-е на входы элемента ИЛИ-НЕ 61, и на его выходе форми у ется разрешакадий потенциал, откры вающий ключ выборки соответствуквдей резервной адресной строки, которая и выбирается вместо отключенной адре ной шины строки.При необходимости замещения дефектной резервной адресной шины столбца ее отключение и замена на исправную адресную шину стро ки производится вышеописанным способом. Рассмотрим как осуществляется контроль правильности работы адресных цепей устройства при отсутствии обращения, правильной работе устройства, наличии дефектов, сбоев, приводящих к неправильной работе. При описании работы логических элементов устройства положительный уровень потенциала соответствует логиче.ской единице, а нулевой - логическому нулю; при правильной работе устройства подача на входы дешифраторов 28 и 29 комбинации кода адреса приводит к тому, что на один из вторых входов ключей 6-9 подаетс единичный положительный разрешаквдий потенциал, а вторые входы остальных ключей 6-9 имеют нулевой уровень, чем разрешается выборка определенной адресной шины строки (столбца)накопителя 1; потенциал выборки адресных шин строк подается на первые входы всех ключей,6 и 7 с входа 26; при подаче на вход 36 дешифратора 28 кодовой комбинации с нечетным числом единиц выбирается одна из адресных шин строк первой группы, а счетным числом единиц - одна из адресных шин строк второй группы. При подаче на вход 37 дешифратор 29 кодовой комбинации с нечетным числом единиц выбирается одна из ад ресных шин столбцов первой группы, а с четным числом единиц -одна из адресных шин столбцов второй группы при подаче на входы дешифраторов 29 комбинации кода адреса, содержащего нечетное число единиц, на входе 47 блока 46 формируется единичный уровень потенциала, а при четном - нуле вой уровень. Сигналы на выходах дискриминаторо 18,20,22,24 рассмотриг/ на примере искриминатора 18, который может быть выполнен, как показано на фиг. 3. При отсутствии обращения все ключи 5закрыты и все напряжение выборки строк с входа 26 через измерительный элемент 19 будет приложено к входу дискриминатора 18. Пороги срабатывания пороговых усилителей 69 и 70 выбраны так, что ни один из них не срабатывает и на его выходах 48 и 49 формируется потенциал, соответствующий логическому нулю. При открывании одного из ключей 6от источника напряжения выборки (не показан) через измерительный элемент 19 потечет ток. При этом за счет падения напряжения на измерительном элементе 19 на вход дискриминатора 18 поступает напряжение, срабатывает первый пороговый усилитель 69 и на выходе 48 дискриминатора 18 появляется единичный уровень положительного потенциала. Второй пороговый усилитель 70 при этом на-, пряжении не срабатывает и на выходе 49 формируется уровень логического .нуля. При от:крывании более одного ключа 6(неправильная работа устройства вследствие отказов, сбоев) от источника напряжения выборки с входа 26 через измерительный элемент 19 будет течь больший ток, при этом на вход дискриминатора 18 будет приложено меньшее напряжение, чем в описанном выше случае. По этому напряжению происходит срабатывание пороговых усилителей 69 и 70 и на выходах 48 и 49 дискриминатора 18 формируются уровни логической единицы. Сигналы на выходах остальных дискриминаторов формируются аналогично. На основе указанных особенностей формирования сигналов дискриминаторами 18,20,22,24 на выходе 58 блока 46 сравнения формируется потен циал ошибки адресации, равный единичному уровню при неправильной работе и нулю в противном случае. С помощью элементов И 72 и 76 блока 46 формируется сигнал о неправильной адресации, заключающийся в выборке более одной адресной шины строки в первой, второй группах адресных шин строк. Выходы элементов И 72 и. 76 объединшотся элементом ИЛИ-НЕ 80 и сигнал ошибки адресации формируется при выборке более одной адресной шины строки в любой группе или в обоих группах адресных шин строк. С помощью элементов И 71 и 75 блока 46 сравнения формируется сигнал о неправильной адресации, заключающейся в выборке более одной адресной шины столбца в первой , второй группах адресных шин строк.

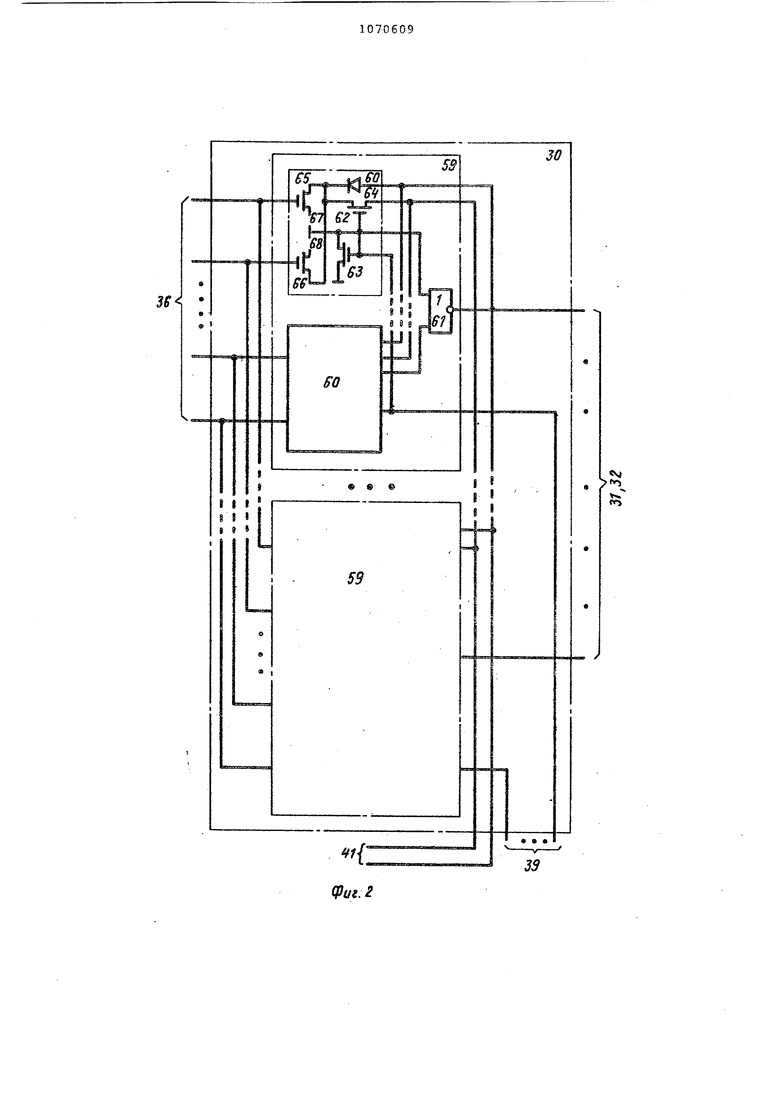

Поскольку выходы элементов И 7i и 75 объединены элементом ИЛИ-НЕ 80, сигнал ошибки адресации формируется при вглборке более одной адресной шины столбца в любой группе или обоих группах адресных шин столбцов

С помогцыо элемента ИЛИ-НЕ 79 формируется сигнал о неправильной с1Дресаи.иИр за лючаюшейся в невыборке хотя бы одной адресной шины строки з обоих группах адресных шин строк.

С помощью эле:мента ИЛИ-НЕ 81 формируется сигнал о неправильной адресации, эа лючающейся в невыборке хотя бы одной адресной шины столбца в обоих группах адресггых шин столбцов, а с помощью элемента И 73 формируется сигнал о неправильной адресал,ии, заключающейся Б .-выборке хотя пы одной ajpGcnoit строки в первой и второй г-руппах,

С помощью элемента И 74 формируется сигнал о неправильной адресации, заключающейся в выборке хоогя бы одной адресной минь- столбца в первой и второй группах, а с помощью сумматора 77 Формируется контрольный код слова,- к которому фактически произошло обращение, равный по модулю два всех разрядов кода адреса, подаваемого на входы дешифраторов 28 и 29 Контрольный код Слова, к которому фактически прокэо1ило обращение, сравнивается затем с контрольным слова, к которому производится обра01ение (подаваемым

на вход 47 блока 46), и в случае несовпадения на выходе сумматора 78 формируется сигнал о неправильной адресации, заключающейся в выборке вместо адресной чиины строки, столбц ,в одной группе, адресной ши.ны строки столбца в другой группе.

Сигнал о неправильной выборке адресных шин строк, столбцов выдаетс при любой возможной комбинации указанной выше неправильной выборки адресных шин строк, столбцов в группах с выхода элемента ИЛИ-НЕ 80.

Предлагаемое устройство позволяет осуществить заменудефектных строк, столбцов на исправные резервные в процессе производства и- эксплуатации устройства без снижения быстродействия устройства, что позволяет при сохранении основных технических характ€;ри-стик значительно повысить вьлход годных изделий, производить оперативный контроль исправности и правильности работы адресных цепей, что значительно повышает надежность работы устройства, кроме того, позволяет формировать сигнал об обращении к дефектным строкам, столбцам, который может быть использован,.для управления внешним устройством, осуществляющим подключение вместо дефектных строк, столбцов исправных из внешнего резерва в случае, если резервных строк, столбцов устройства оказалось недостаточно ДЛЯ устранения всех деф-ектов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1982 |

|

SU1023393A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU959168A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Запоминающее устройство с резервированием | 1989 |

|

SU1674252A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970477A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1418816A1 |

| Полупроводниковое оперативное запоминающее устройство | 1987 |

|

SU1531164A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Запоминающее устройство | 1983 |

|

SU1107176A1 |

| Запоминающее устройство | 1985 |

|

SU1252816A1 |

РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮИЩЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ, содержащее матричный накопитель, состоящий из групп основных и резервных запоминающих элементов,расположенных на пересечении основных и резервных адресных шин строк и столбцов,четырегруппы ключей, основную программируемую логическую матрицу, первый и второй дешифраторы, входы которых являются одними из входов устройства, отличающееся тем, что, с целью повышения быстродействия и надежности устройства путем обеспечения контроля его адресных цепей, в него введены две группы нагрузочных элементов, две группы коммутируют.их элементов, четыре измерительных элемента, четыре дискриминатора, дополнительная программируемая матри.ца, четыре разделительных элемента, четыре ключа, блок сравнения, третий и четвертый дешифраторы, причем адресные выходы матричного накопителя подключены к одним из выходов нагрузочных элементов первой и второй групп другие выводы которых соединены с шиной нулевого потенциала, адресные входы матричного накопителя подключены к выходам коммутирукадих элементов первой и второй группы, входы которых соединены с выходами соответ-ствующих ключей групп, первые входы ключей каждой группы соединены непосредственно с выходами одноименных ключей с первого по четвертый и через соответствующие разделительные элементы - с одними из выводов одноименных измерительных элементов, вторые входы ключей первой и второй групп соединены с выходами первого деишфратора и основной программируемой логической матрицц, одни из входов которой подключены соответственно к вхо- § дам первого дешифратора и одним из (Л выходов третьего дешифратора, вторые входы ключей третьей и четвертой групп соединены с выходами второго дешифратора и дополнительной програ ммируемой логической матрицы, одни из входов которой подключены к одним из входов второго дешифратора, и другим выходам третьего дешифратора, один из выводов каждого измерительно го элемента подключен к входу соото СУ: ветствующего дискриминатора, выходы дискриминаторов подключены к одним из входов блока сравнения, выходы о со которого являются выходами устройства, выходы четвертого дешифратора соединены с одними из входов ключей с первого по четвертый, входы третьего и четвертого дешифраторов, другие выводы измерительных элементов и другие входы программируемых логических матриц, ключей и блока сравнения являются другими входами устройства.

СриеЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Патент CLrA № 4051354, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

Авторы

Даты

1984-01-30—Публикация

1982-08-23—Подача