Изобретение относится к ычисли- тепьной технике и- ориентировано на использование в быстродействующих специализированных вычислителях, системах цифровой обработки сигналов и различных системах автоматики для вычисления Экспоненциальной функции от аргументов, представленных в модулярной системе счисления.

Целью изобретения является повышение быстродействия.

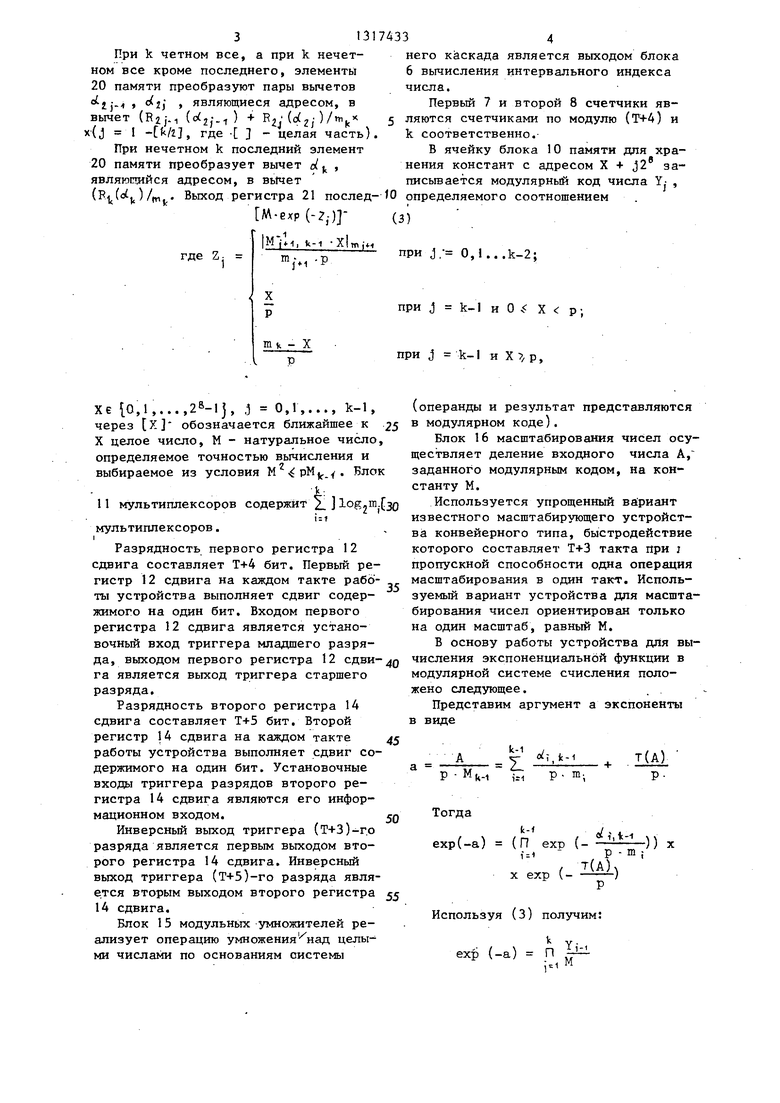

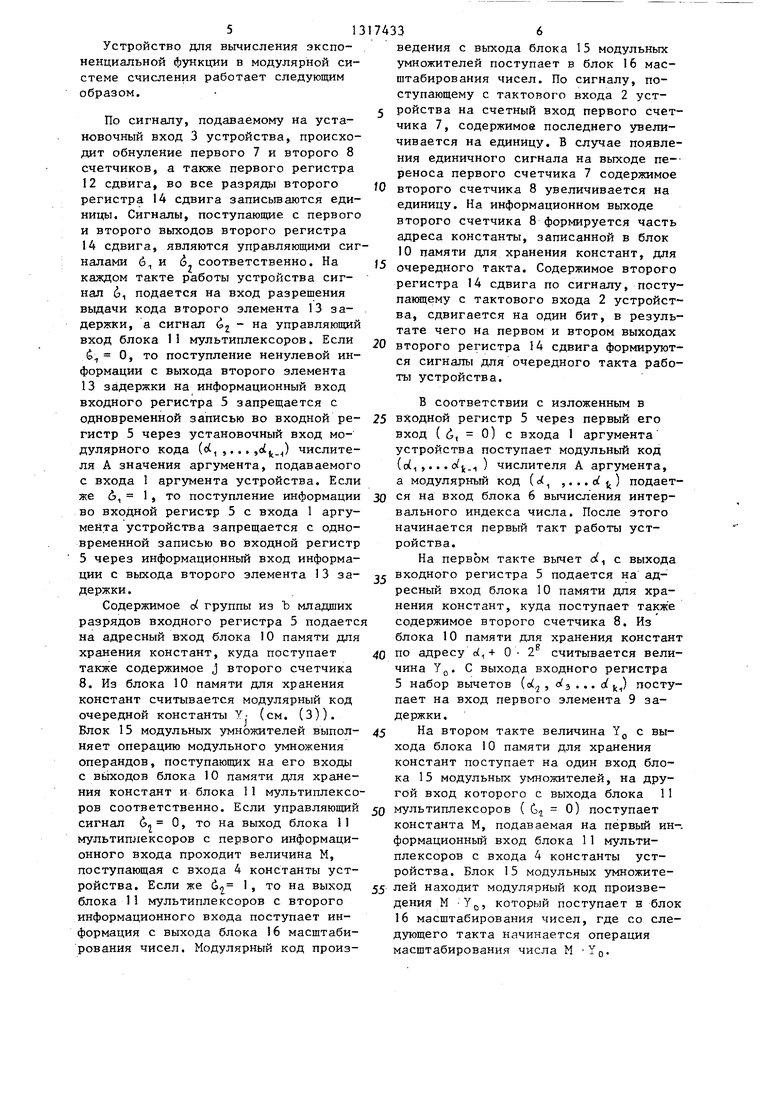

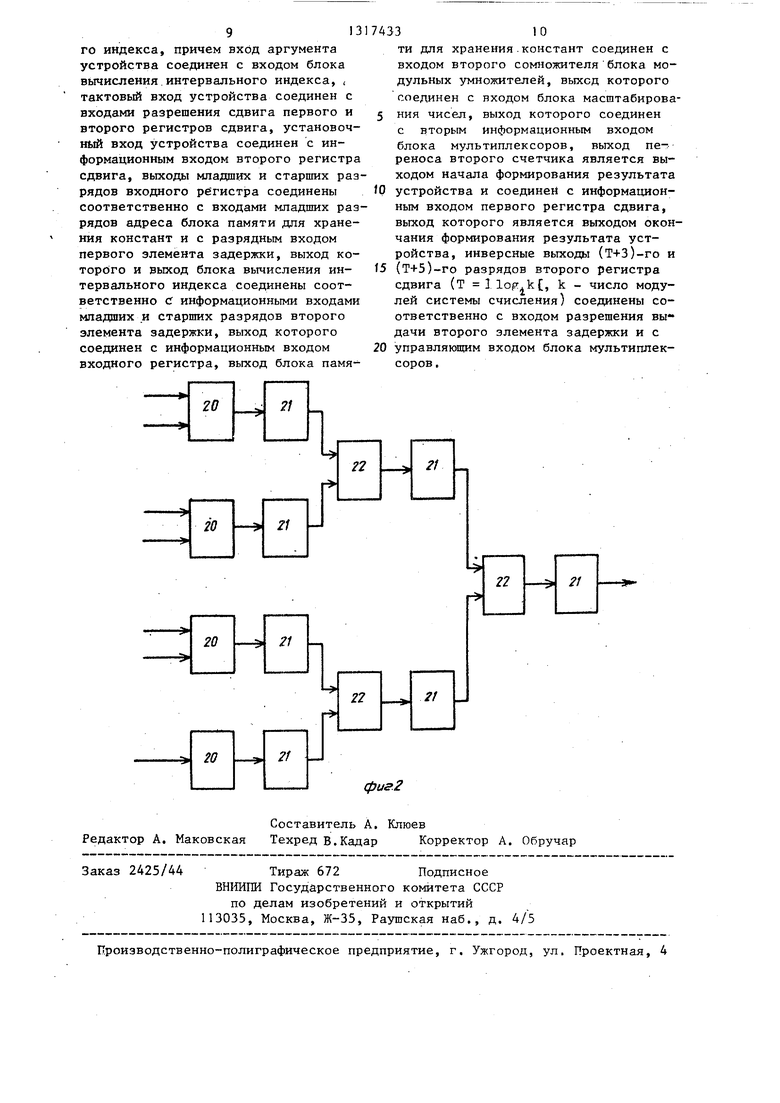

На фиг. 1 приведена структурная схема предлагаемого устройства для вычисления экспоненциальной функции в модулярной системе счисления; на фиг. 2 - схема блока вычисления интервального индекса (для k 7,, И - число модулей системы счисления).

Устройство дпя вычисления экспоненциальной функции в модулярной системе счисления (фиг. 1) содержит вход 1 аргумента, тактовый вход 2, установочный вход 3, вход 4 константы устройства, входной регистр 5, блок 6 вычисления интервального индекса числа, первый счетчик 7, второй счетчик 8, первый элемент 9 задержки, блок 10 памяти для хранения констант, блок 11 мультиплексоров, первый регистр 12 сдвига, второй элемент 1.3 задержки, второй регистр 14 сдвига, блок 15 модульных умножителей, блок 16 масштабирования чисел, выход 17 окончания формирования рез.ультата устройства, выход 18 резуль- 35. выходом. Вход разрешения выдачи кода

тата устройства и выход 19 начала формирования результата устройства.

Блок 6 вычисления интервального индекса числа (фиг. 2) содержит элементы 20 памяти, регистры 21 и сумматоры 22 по модулю

Вход 1 аргумента устройства подключен к входу входного регистра 5, предназначенного для приема модулярпоследнего регистра второго элемента 13 задержки является его входом разрешения вьщачи кода.

Блок 6 вычисления интервального индекса числа имеет Т-каскадную конвейерную структуру.

Блок вычисления интервального инного кода по попарно взаимно простым -5 декса числа 6 по входному модулярнооснованиям ш. . .т( й ...c/i., ) исходного числа А из множества D fO,l..., р М , -Ц;- -о(,- (А1,- (i l,2,...,k), 2р + k-2,

причем и 7/

ное натуральное число;

Р - фиксированп 50 Кы П,т. ;

через |Х1| обозначен наименьший неотрицательный вычет.

Разрядность входного регистра 5 составляет (k - 1)Ъ бит, где Ъ - разрядность вычетов по наибольшему из модулей выбранной модулярной системы счисления. Информационный вход входного регистра 5 соединен с выходом

му коду ( 0 , ) некоторого числа А осуществляет формирование вычета за Т тактов

1 Т (А) lRjc;jL

Ri(oii)

55

,f.-i m.

при

,2...k-l

(1)

M

при i k

k- -i

,., /т.; М,..,М,.,-(2)

второго элемента 13 задержки. Выход группы из Ъ младших разрядов входного регистра 5 подключен к адресному входу блока 10 памяти для хранения конс.тант. Выходы остальных (k-2) групп из Ъ разрядов подрслючены к входу первого элемента 9 задержки.

Первый элемент 9 задержки представляет собой цепочку из Т-1 последовательно соединенных регистров, где Т Jlogj k, через ХГ обозначается наименьшее целое число не меньшее X. Вход первого из регистров является входом первого элемента 9

задержки. Разрядность регистров, вхо- в состав первого элемента 9 задержки, составляет (k-2)Ъ бит. Выход последнего регистра первого элемента 9 задержки является его выходом.

Второй элемент 13 задержки представляет собой цепочку из четьфех последовательно соединенных регистров, вход первого из которых является входом второго элемента 13 задержки. Разрядность регистров, входящих в состав второго элемента 13 задержки, составляет (k-l)b бит.

Входы первых (k-2).групп и вход старшей (k-I)-й группы из Ъ разрядов первого регистра являются входом элемента 13 задержки.

Выход последнего регистра второго . элемента 13 задержки является его .

последнего регистра второго элемента 13 задержки является его входом разрешения вьщачи кода.

Блок 6 вычисления интервального индекса числа имеет Т-каскадную конвейерную структуру.

Блок вычисления интервального индекса числа 6 по входному модулярн

му коду ( 0 , ) некоторого числа А осуществляет формирование вычета за Т тактов

1 Т (А) lRjc;jL

Ri(oii)

5

,f.-i m.

при

,2...k-l

(1)

M

при i k

k- -i

,., /т.; М,..,М,.,-(2)

3131

при k четном все, а при k нечетном все кроме последнего, элементы 20 памяти преобразуют пары вычетов ij.i , ij , являющиеся адресом, в вычет (R2J.1 ( ) + 2j (2j (j 1 , где - целая часть).

При нечетном k последний элемент 20 памяти преобразует вычет d , являющийся адресом, в вь1чет (B(otj)/ . Выход регистра 21 послед М-ехр (-2.)J

Z.

IM JM, k-1 -Xl,

m

X Р

mk - X

Хе 0,1,...,, ,j 0,1,..., k-1, через Х обозначается ближайшее к 25 X целое число, М - натуральное число, определяемое точностью вычисления и выбираемое из условия ,;.|. Блок

Ijlogji

11 мультиплексоров содержит J

i:1

мультиплексоров.

I

Разрядность первого регистра 12 сдвига составляет Т+4 бит. Первый регистр 12 сдвига на каждом такте работы устройства выполняет сдвиг содержимого на один бит. Входом первого регистра 12 сдвига является установочный вход триггера младшего разряда, выходом первого регистра 12 СДВИга является выход триггера старшего разряда.

Разрядность второго регистра 14 сдвига составляет Т+5 бит. Второй регистр 14 сдвига на каждом такте работы устройства выполняет сдвиг содержимого на один бит. Установочные входы триггера разрядов второго регистра 14 сдвига являются его информационном входом.

Инверсный выход триггера (Т+3)-го разряда является первым выходом второго регистра 14 сдвига. Инверсный выход триггера (Т+5)-го разряда является вторым выходом второго регистра 14 сдвига.

Блок 15 модульных умножителей реализует операцию умножения над целы- ми числами по основаниям системы

4334

него каскада является выходом блока 6 вычисления интервального индекса числа.

Первый 7 и второй 8 счетчики яв- 5 ляются счетчиками по модулю {Т+4) и k соответственно.В ячейку блока 10 памяти для хранения констант с адресом X + j2 записывается модулярный код числа Y-, to определяемого соотношением

(3) при j,- 0,l...k-2;

при j k-1 и О v X

Р;

при j k-1 и X 7/ р,

(операнды и результат представляются в модулярном коде).

Блок 16 масштабирования чисел осуществляет деление входного числа А, заданного модулярным кодом, на константу М.

Используется упрощенный вйриант известного масштабирующего устройства конвейерного типа, быстродействие которого составляет Т+3 такта при j пропускной способности одна операция масштабирования в один такт. Используемый вариант устройства дпя масштабирования чисел ориентирован только на один масштаб, равный М.

В основу работы устройства для вычисления экспоненциальной функции в модулярной системе счисления положено следующее.

Представим аргумент а экспоненты в виде

(-а) П

1

Ik:

М

513

Устройство для вычисления экспоненциальной функции в модулярной системе счисления работает следующим образом.

По сигналу, подаваемому на установочный вход 3 устройства, происходит обнуление первого 7 и второго 8 счетчиков, а также первого регистра

12сдвига, во все разряды второго регистра 14 сдвига записьшаются единицы. Сигналы, поступающие с первого и второго выходов второго регистра

14 сдвига, являются управляющими сигналами 6 и & соответственно. На каждом такте работы устройства сигнал 6, подается на вход разрешения выдачи кода второго элемента 13 задержки, а сигнал 6 - на управляющий вход блока 11 мультиплексоров. Если О, то поступление ненулевой информации с выхода второго элемента

13задержки на информационный вход входного регистра 5 запрещается с одновременной записью во входной регистр 5 через установочный вход модулярного кода (, ,. . . ,оС,.) числителя А значения аргумента, подаваемого с входа 1 аргумента устройства. Если же 6, 1, то поступление информации во входной регистр 5 с входа 1 аргумента устройства запрещается с одновременной записью во входной регистр 5 через информационньй вход информации с выхода второго элемента 13 задержки .

Содержимое d группы из Ъ младших разрядов входного регистра 5 подаетс на адресный вход блока 10 памяти для хранения констант, куда поступает также содержимое j второго счетчика 8. Из блока 10 памяти для хранения констант считывается модулярный код очередной константы Y- (см. (З)). Блок 15 модульных умножителей выполняет операцию модульного умножения операндов, поступающих на его входы с вь1ходов блока 10 памяти для хранения констант и блока 11 мультиплексоров соответственно. Если управляющий сигнал (-., 0, то на выход блока 11 мультиплексоров с первого информационного входа проходит величина М, поступающая с входа 4 константы устройства. Если же 1, то на выход блока 11 мультиплексоров с второго информационного входа поступает информация с выхода блока 16 масштабирования чисел. Модулярный код произ36

ведения с выхода блока 15 модульных умножителей поступает в блок 16 масштабирования чисел. По сигналу, поступающему с тактового входа 2 устройства на счетный вход первого счетчика 7, содержимое последнего увеличивается на единицу. В случае появления единичного сигнала на выходе переноса первого счетчика 7 содержимое

второго счетчика 8 увеличивается на единицу. На информационном выходе второго счетчика 8 формируется часть адреса константы, записанной в блок 10 памяти для хранения констант, для

очередного такта. Содержимое второго регистра 14 сдвига по сигналу, поступающему с тактового входа 2 устройства, сдвигается на один бит, в результате чего на первом и втором выходах

второго регистра 14 сдвига формируются сигналы для очередного такта работы устройства.

В соответствии с изложенным в

входной регистр 5 через первый его вход ( d, о) с входа 1 аргумента устройства поступает модульный код (o(i ,... .i ) числителя А аргумента, а модулярный код (( ,,., d подается на вход блока 6 вычисления интервального индекса числа. После этого начинается первый такт работы устройства.

На первом такте вычет of, с выхода

входного регистра 5 подается на адресный вход блока 10 памяти для хранения констант, куда поступает также содержимое второго счетчика 8. Из блока 10 памяти для хранения констант

по адресу о(, + О- 2 считывается величина Уц. С выхода входного регистра 5 набор вычетов (d , d .,. поступает на вход первого элемента 9 задержки.

На втором такте величина Y с выхода блока 10 памяти для хранения констант поступает на один вход блока 15 модульных умножителей, на другой вход которого с выхода блока 11

мультиплексоров ( G О) поступает константа М, подаваемая на первый ин-. формационный вход блока 11 мультиплексоров с входа 4 константы устройства. Блок 15 модульных умножителей находит модулярный код произведения М -YQ, который поступает н блок 16 масштабирования чисел, где со следующего такта начинается операция масштабирования числа М -YQ.

713

По истечении Т-го такта работы устройства на выходе блока 6 вычисления интервального индекса числа формируется вычет Г(А), который на след ющем такте записывается в старшую группу из Ъ разрядов первого регистра второго элемента 13 задержки, в остальные k-2 группы из Ъ разрядов которого с выхода первого элемента 9 задержки поступает выбор вычетов (d oij,... d. t-i).

На (Т+4)-м такте управляющий сигнал 6 1, вследствие чего с выхода второго элемента 13 задержки в входной регистр 5 поступает набор тов -(«ij Т(А)). На выходе переноса первого счетчика 7 появляется единичный сигнал, вследствие чего содержимое второго счетчика 8 становится равным единице.

На (Т+5)-м такте блок 16 масштабирования чисел на своем выходе формирует модулярный код величины Y . Вычет 0 с выхода входного регистра 5 подается на адресный вход блока 10 Оамяти для хранения констант, на вход которого поступает также содержимое второго счетчика 8, Из блока 10 памяти для хранения констант по адресу 1 -2 ® считывается величина Y. С второго выхода входного регистра 5 набор вычетов (о( -л (-Л) )

поступает на вход первого элемента 9 задержки.

На (Т+б)-м такте работы устройства величина Y с выхода блока 10 памяти для хранения констант поступает на один вход блока 15 модульных умножителей, на другой вход которого с выхода блока 11 мультиплексоров ( 6i 1) подается величина Y, по- .ступающая на второй информационный вход блока 11 мультиплексоров с выхода блока 16 масштабирования чисел. Блок 15 модульных умножителей находит модулярный код произведения Y, х X Y , который поступает в блок 16 масштабирования чисел, где со следующего такта начинается операция масштабирования указанных чисел.

На следующих тактах работы устройства вьшолняются действия, аналогичные описанным вьш1е. По окончании k;-(T+4) тактов на выходе переноса второго счетчика 8 появляется единичный сигнал, поступающий на третий выход 19 устройства, что означает окончание вычисления значения экспо8

ненциальной функции от аргумента, которое снимается с выхода блока 16 масштабирования чисел на следующем такте.

Благодаря конвейерной структуре в предлагаемом устройстве одновременно может происходить вычисление экспоненциальной функции от Т+4 аргументов. При этом появление единичного сигнала на выходе 19 устройства означает начало появления на выходе 18 устройства вычисленных значений экспоненциальной функции и возможность начала вычислений для новых Т+4 ар- гументов.

Появление единичного сигнала на выходе 17 устройства означает завершение вычисления значений экспоненциальной функции от Т+4 аргументов. При работе устройства в конвейер- ном режиме из расчета на одно функциональное значение быстродействие устройства составляет k тактов.

25

ормула изобретения

Устройство для вычисления экспоненциальной функции в модулярной системе счисления, содержащее входной

регистр, блок памяти для хран ения

констант, первый регистр сдвига, первый и второй счетчики, блок мультиплексоров , блок модульных умножите ; лей и блок масштабирования чисел,

причем вход аргумента устройства соединен с установочным входом входного регистра, тактовый вход устройства соединен со счетным входом первого счетчика, вход обнуления которого

соединен с входом обнуления второго счетчика, с входом обнуления первого регистра сдвига и с установочном входом устройства, вход константы которого соединен с первым йнформационным входом блока мультиплексоров, выход которого соединен с входом первого сомножителя блока модульных умножителей, выход блока масштабирования является выходом результата

устройства, информационный выход второго счетчика соединен с входами старших разрядов адреса блока памяти для хранения констант, выход первого счетчика соединен со счетным входом

второго счетчика, отличаю- щ е е с я тем, что, с целью повышения быстродействия, в него введены два элемента задержки, второй регистр сдвига и блок вычисления интервально913

го индекса, причем вход аргумента устройства соединен с входом блока вычисления.интервального индекса, , тактовый вход устройства соединен с входами разрешения сдвига первого и второго регистров сдвига, установочный вход устройства соединен с информационным входом второго регистра сдвига, выходы младших и старших разрядов входного регистра соединены соответственно с входами младших разрядов адреса блока памяти для хранения констант и с разрядным входом первого элемента задержки, выход которого и выход блока вычисления интервального индекса соединены соответственно С информационными входами младших и старших разрядов второго элемента задержки, выход которого соединен с информационным входом входного регистра, выход блока памяСоставитель А. Клюев Редактор А. Маковская Техред В.Кадар Корректор А. Обручар

2425/44

Тираж 672 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

743310

ти для хранения.констант соединен с входом второго сомножителя блока модульных умножителей, выход которого соединен с входом блока масштабирова5 ния чисел, выход которого соединен с вторым информационным входом блока мультиплексоров, выход переноса второго счетчика является выходом начала формирования результата

О устройства и соединен с информацион- ньпм входом первого регистра сдвига, выход которого является выходом окончания формирования результата устройства, инверсные выходы (Т+3)-го и

t5 (Т+5)-го разрядов второго регистра сдвига (т , k - число модулей системы счисления) соединены соответственно с входом разрешения выдачи второго элемента задержки и с

20 управляющим входом блока мультиплексоров ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

| Устройство для масштабирования чисел | 1989 |

|

SU1667066A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

Изобретение относится к вычислительной технике и ориентировано к использование в быстродействующих специализированных вычислителях, системах цифровой обработки сигналов и в различных системах автоматики для вычисления экспоненциальной функции в модулярной системе счисления. Цель изобретения состоит в повьшении быстродействия. Поставленная цель достигается тем, что в устройство, содержащее входной регистр 5, счетчики 7, 8, блок 10 памяти для хранения констант, блок 11 мультиплексоров, регистр 12 сдвига, блок 15 модульных умножителей и блок 16 масштабирования, введены элементы задержки 9. 13. регистр 14 сдвига и блок 6 вычисления интервального индекса с соответствующтми связями. 2 ил. 2 S (Л

| Устройство для вычисления экспоненты | 1978 |

|

SU798857A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-15—Публикация

1985-11-22—Подача