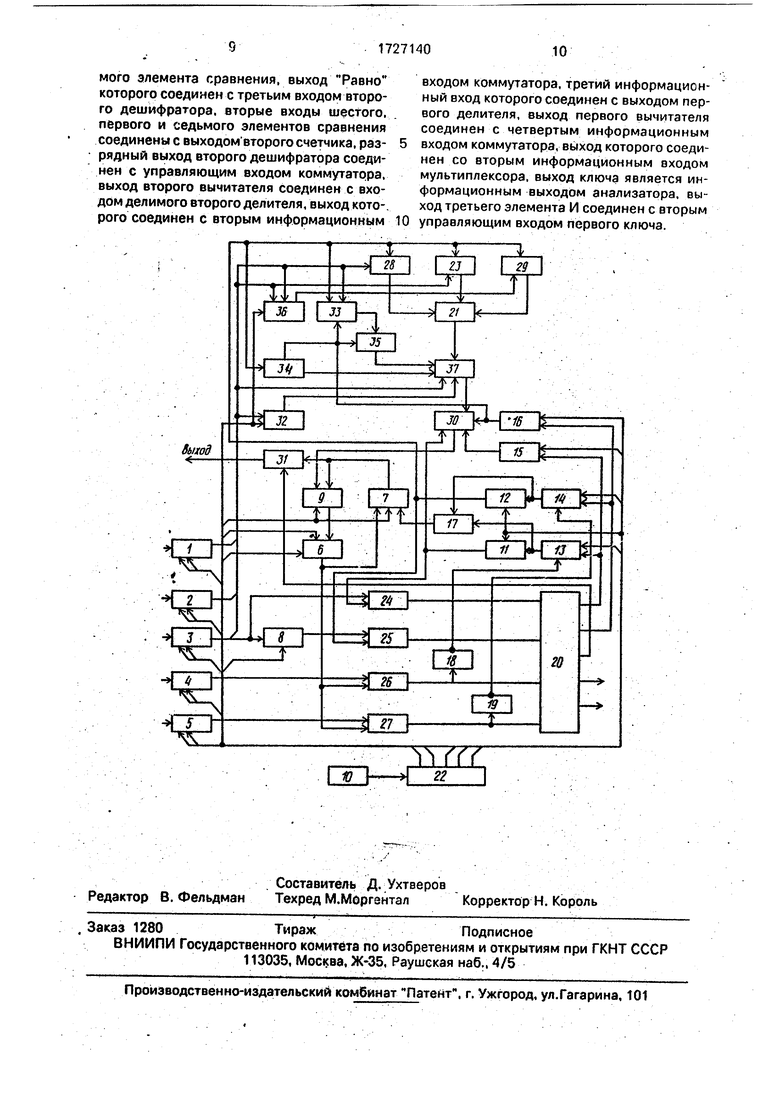

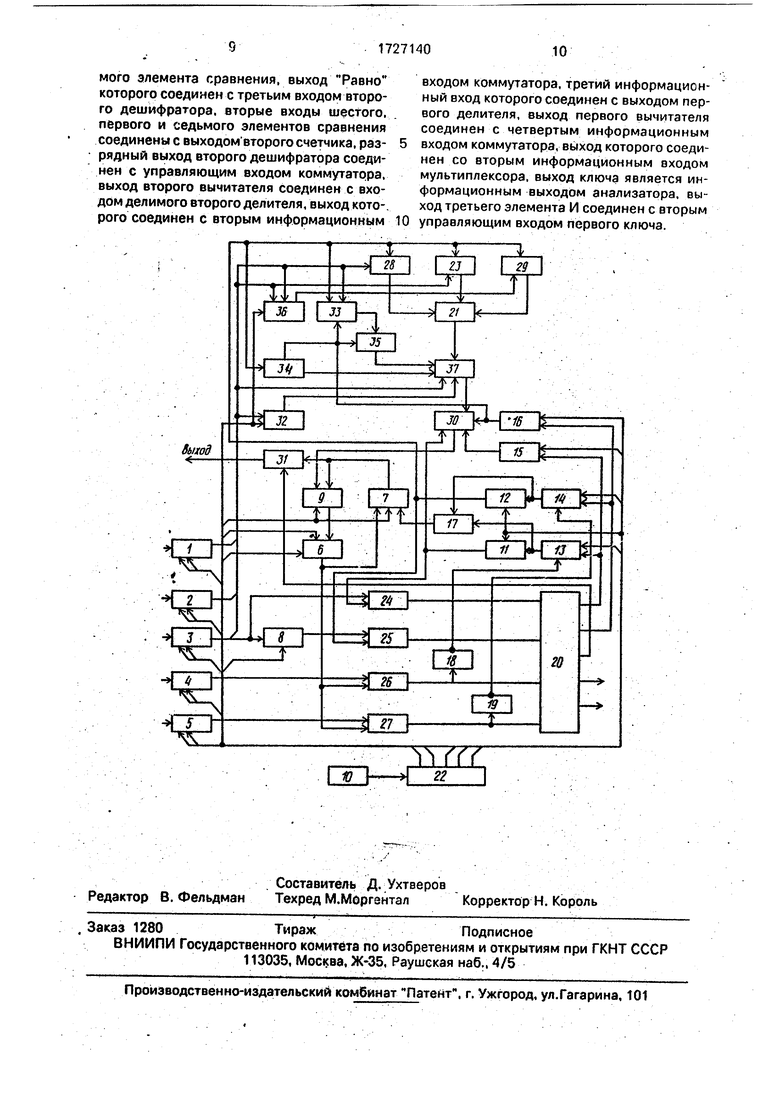

вого умножителя 8, с вторым входом сумматора 36 и первыми входами первого, второго элементов сравнения 23, 24, выход первого-умножителя 8 соединен с первым входом третьего элемента сравнения 25, второй вход которого соединен с выходом второго счетчика 12, подключенного к входу вычитаемого второго вычитателя 33 и к входу делимого первого делителя 34, выход четвертого регистра 4 соединен с первым входом четвертого элемента сравнения 26, второй вход которого соединен с первым входом пятого элемента сравнения 27 и с выходом шестого регистра 6, подключенного к информационному входу седьмого ре- гистра 7. выход пятого регистра 5 соединен с вторым входом пятого элемента сравнения 27, выходы Равно второго, третьего, четвертого и пятого элементов сравнения 24, 25, 26, 27 соединены с первым, вторым, третьим и четвертым входами первого де- шифратора 20 соответственно, второй выход которого соединен с первыми входами второго элемента И 14, четвертого элемента И 16, выход второго элемента И 14 соединен со счетным входом второго счетчика- 12 и первым входом элемента ИЛИ 17, выход первого элемента И 13 соединен со счетным входом первого счетчика 11 и вторым входом элемента ИЛИ 17, выход которого сое- динен с синхровходом седьмого регистра 7, выход которого соединен с первым входом второго умножителя 9 и информационным входом ключа 31, управляющий вход которого соединен с третьим выходом первого дешифратора 20, выход второго умножителя 9 соединен с информационным входом шестого регистра 6, выход Равно четвертого элемента сравнения 26 через первый элемент НЕ 18 соединен с вторым входом первого элемента И 13. выход Равно пятого элемента сравнения 27 через второй элемент НЕ 19 соединен с вторым входом второго элемента И 14, выход генератора тактовых импульсов 10 соединен с синхров- ходом блока синхронизации 22, первый выход которого соединен с входом сброса первого, второго, третьего, четвертого, пятого, шестого регистров.1, 2, 3, 4, 5, 6 и входами предварительной установки седь- мого регистра 7 и первого и второго счетчи- ков 11, 12, второй выход блока синхронизации 22 соединен с синхровхода- ми первого, второго, третьего, четвертого, пятого регистров .1, 2, 3, 4, 5, с.тактовыми входами первого вычитателя 32, сумматора 36 и первого умножителя 8, третий выход б/ioka синхронизации 22 соединен с вторыми входами третьего и четвертого элементов И 15, 16, четвертый выход блока

синхронизации 22 соединен с синхровходом шестого регистра бис тактовым входом. второго умножителя 9, пятый выход блока синхронизации 22 соединен с третьими входами первого и второго элементов И 13, 14, выход четвертого элемента И 16 соединен с тактовыми входами первого, второго делителей 34, 35, второго вычитателя 33 и первым управляющим входом мультиплексора 30, первый вход шестого элемента сравнения 28 соединен с первым входом сумматора 36, с входом уменьшаемого второго вычитателя 33 и выходом второго регистра 2, выход Равно шестого элемента сравнения 28 соединен с первым входом второго дешифратора 21, второй вход которого соединен с выходом Равно первого элемента сравнения 23, выход сумматора 36 соединен с первым входом седьмого элемента сравнения 29, выход Равно которого соединен с третьим входом второго дешифратора 21, вторые входы шестого, первого, седьмого элементов сравнения 28, 23, 29 соединены с выходом второго счетчика 12, разрядный выход второго дешифратора 21 соединен с управляющим входом коммутатора 37, выход второго вычитателя 33 соединен с входом делимого второго делителя 35, выход которого соединен с вторым информационным входом коммутатора 37, третий информационный вход которого соединен с выходом первого делителя 34. второй вход второго элемента сравнения 24 соединен с выходом первого счетчика 11 и вторым информационным входом мультиплексора 30, выход первого вычитателя 32 соединен с четвертым информационным входом коммутатора 37, выход которого соединен с первым информационным входом- мультиплексора 30, выход которого соединен с вторым входом второго умножителя 9, выход ключа 31 является информационным выходом анализатора, выход третьего элемента И 15 соединен с вторым управляющим входом мультиплексора 30.

Устройство работает Следующим образом.

После включения питания на первом выходе блока синхронизации 22 появляется импульс, который поступает на входы сброса первого, второго, третьего, четвертого, пятого, шестого регистров 1, 2, 3, 4, 5, 6, обнуляет их и подготавливает их к приему информации. Этот же импульс поступает на вход предварительной установки седьмого регистра 7, первого и второго счетчиков 1.1, 12 и записывает в них 1. Далее следующие импульсы с второго выхода блока синхронизации 22 поступают на синхровходы первого, второго, третьего, четвертого, пятого

регистров 1, 2, 3, 4, 5 и осуществляется запись постоянных величин Р, К, N, Рп, Рн соответственно, а также при поступлении на тактовый вход первого вычитателя 32 происходит вычисление величины (1 - р), при поступлении на тактовый вход сумматора 36 вычисляется величина (N - К), при поступлении на тактовый вход первого умножителя 8 вычисляется величина (2 х N). Значения величин N, 2N, Рв, К, N, N-K, Р, которые используются в качестве пороговых значений, поступают на первые входы второго, третьего, четвертого, шестого, первого седьмого элементов сравнения 24, 25, 26, 28, 23. 29 и второй вход пятого элемента сравнения 27 соответственно.

Элементы сравнения работают таким образом, что на выходе Равно появляется логическая 1 в том случае, если значения величин, поступающих на вторые .входы, превысят .пороговые значения.

На начальном этапе на выходах всех, элементов сравнения присутствуют логические 0, которые поступают на входы первого и второго дешифраторов 20, 21. При данной комбинации на входе первого дешифратора 20 на его первом входе появляется логическая 1,. которая поступает на первые входы третьего, первого элементов И 15, 13. На разрядном выходе второго дешифратора 21 появляется комбинация, которая воздействует на управляющий вход коммутатора 37, в результате чего выход первого делителя через коммутатор 37 подключается к первому информационному входу мультиплексора 30. Появление импульса на третьем входе блока синхронизации 22 приводит к тому, что на выходе третьего элемента И 16 появляется логическая 1, которая поступает на второй управляющий вход мультиплексора 30, в результате;чего выход первого счетчика 11 подключается через мультиплексор 30 к второму входу второго умножителя 9. На первом входе второго умножителя 9 присутствует 1, которая поступила с седьмого регистра 7, записанная на начальном этапе. Затем на четвертом выходе блока синхронизации 22 формируется импульс, который поступает на тактовые входы второго умножителя 9 и шестого регистра 6. В результате происходит перемножение чисел, присутствующих на первом и втором входах второго умножителя 9, и запись результата перемножения в шестой регистр 6 и далее на входы четвертой и пятой схем сравнения 26,27, где происходит сравнение с величинами Рв и Рн. Затем на пятом выходе блока синхронизации 22 формируется логическая 1, которая поступает на входы

первого, второго элементов И 13, 14, при этом на выходе первого элемента И 13 будет логическая 1, которая поступает на синх- ровход седьмого регистра 7 и записывается 5 содержимое из шестого регистра 6. Кроме того, содержимое первого счетчика 11 увеличивается на 1. На этом заканчивается первый шаг вычисления и начинается второй.

0Второй шаг вычисления начинается после очередного появления импульса на третьем, выходе блока синхронизации 22, который поступает на входы четвертого и третьего элементов И 16, 15. В зависимости

5 от выходного состояния первого дешифра тора 20, которое зависит от состояния второго, третьего, четвертого, пятого элементов сравнения 24. 25, 26, 27, появляется логическая 1 на выходе третьего или

0 четвертого элементов И 16, 15. Наличие логической 1 на выходе третьего элемента И 15 позволяет подключить через мультиплексор 30 выход первого счетчика 11 к входу второго умножителя 9, это соответствует на5 личию числа Ai на входе второго умножите ля 9. Наличие логической 1 на выходе четвертого элемента И 16 позволяет подключить через мультиплексор 30 выходные величины, поступающие с коммутатора 37

0 на вход второго умножителя 9, это соответствует наличию числа BI на входе второго умножителя 9. Затем вновь на четвертом выходе блока синхронизации 22 формируется импульс, по которому происходит пере5 множение чисел, присутствующих на первом, втором входах второго умножителя 9 и запись результата перемножения в шестой регистр 6, и далее на элементы сравне- ния 26, 27.

0 Затем импульс с пятого выхода блока синхронизации 22 поступает на входы первого и второго элементов И 13, 14. Логическая 1 будет на выходах тех элементов И, у которых на всех трех входах присутствуют

5 логические 1, и поступают либо на первый счетчик 11, либо на второй счетчик 12 и через элемент ИЛ И 17 поступает на седьмой регистр 7 для записи результата с шестого регистра 6 и на информационный вход седь0 мого регистра 7. Содержимое счетчиков увеличивается на 1. Далее следует очередной шаг вычисления. После того н.з выходе первого счетчика 11 появляется число N, а на выходе второго счетчика 12 - число 2N. На

5 третьем выходе первого дешифратора 20 появляется логическая 1, которая поступит на управляющий вход ключа 31. и информация с.седьмого регистра 7 через ключ 31 поступит на выход. На этом устройство заканчивает работу.

Формула изобретения

Статический анализатор, состоящий из трех регистров и содержащий генератор тактовых импульсов, два счетчика, первый, второй, третий элементы И, элемент ИЛИ, элемент НЕ, выход первого элемента И соединен со счетным входом первого счетчика, выход второго элемента И соединен с первым входом элемента ИЛИ, отличаю- щ и и с я тем, что, с целью повышения точности, в него введены четвертый, пятый, шестой, седьмой регистры, два дешифратора, два умножителя, блок синхронизации, второй элемент НЕ, семь элементов сравне- ния, четвертый элемент И, ключ, мультиплексор, два вычитателя, два делителя,, сумматор и коммутатор, информационный вход первого регистра соединен с входом задания текущего значения функции рас- пределения анализируемых процессов анализатора, информационный вход второго регистра соединен с входом задания количества анализируемых входных процессов анализатора, информационный вход треть- его регистра соединен с входом задания длины анализируемых входных процессов анализатора, информационный вход четвертого регистра соединен с входом задания верхнего значения вычисляемой совокупной функции распределения анализатора, информационный, вход пятого регистра соединен с входом задания нижнего значения вычисляемой совокупной функции распределения анализатора, выход первого регистра соединен с входом уменьшаемого первого вычислителя и первым информационным входом коммутатора, первый выход первого дешифратора соединен с первыми входами первого.и третьего элементов И, выход третьего регистра соединен с первым входом первого умножителя, со вторым входом сумматора и первыми входами первого : и второго элементов сравнения, выход первого умножителя соединен с первым входом третьего элемента сравнения, второй вход которого соединен с выходом второго счетчика, второй вход второго элемента сравнения соединен с выходом первого счетчика и первым информационным входом мульти- плексора, выход которого соединен с вторым входом второго умножителя, второй вход первого элемента сравнения соединен с входом вычитаемого второго вычитателя и входом делимого первого делителя,-выход четвертого регистра соединен с первым входом четвертого элемента сравнения, второй вход которого соединен с первым входом пятого элемента сравнения и с выходом шестого регистра, подключенного к информационному входу седьмого регистра, выход пятого регистра соединен с вторым входом пятого элемента сравнения, выходы Равно второго, третьего, четвертого и пятого элементов сравнения соединены с первым, вторым, третьим и четвертым входами первого дешифратора соответственно, второй выход которого соединен с первыми входами второго и четвертого элементов И, выход второго элемента И соединен со счетным входом второго счетчика, выход первого, элемента И соединен с вторым входом элемента ИЛИ, выход которого соединен с син- хровхрдом седьмого регистра, выход которого соединен с первым входом второго умножителя и информационным входом ключа, управляющий вход которого соединен с третьим выходом первого дешифратора, выход второго умножителя соединен с информационным входом шестого регистра, выход Равно четвертого элемента сравнения через первый элемент НЕ соединен с вторым входом первого элемента И, выход Равно пятого элемента сравнения через второй элемент НЕ соединен с вторым входом второго элемента И, выход генератора тактовых импульсов соединен с синх- ровходом блока синхронизации, первый выход которого соединен с входом сброса первого, второго, третьего, четвертого, пятого и шестого регистров и входами предварительной установки седьмого регистра и первого и второго счетчиков, второй выход блока синхронизации соединен с синхров- ходами первого, второго, третьего, четвертого, пятого регистров, с тактовыми входами первого вычитателя, сумматора и первого умножителя, третий выход блока синхронизации соединен с вторыми входами третьего и четвертого элементов И, четвертый -выход блока синхронизации соединен с синхровходом шестого регистра и тактовым входом второго умножителя, пятый выход блока синхронизации соединен с третьими входами первого и третьего элементов И, выход четвертого элемента И соединен с тактовыми входами первого и второго делителей второго вычитателя и первым управляющим входом мультиплексора, второй управляющий вход которого соединен с выходом третьего элемента И. первый вход шестого элемента сравнения соединен с первым входом сумматора, с входом уменьшаемого второго вычитателя и выходом второго регистра, выход Равно . шестого элемента сравнения соединен, с первым входом второго дешифратора, второй вход которого соединен с выходом Равно первого элемента сравнения, выход сумматора соединен с первым входом седьмого элемента сравнения, выход Равно которого соединен с третьим входом второго дешифратора, вторые входы шестого, первого и седьмого элементов сравнения соединены с выходом второго счетчика, разрядный выход второго дешифратора соединен с управляющим входом коммутатора, выход второго вычитателя соединен с входом делимого второго делителя, выход кото-, рого соединен с вторым информационным

входом коммутатора, третий информационный вход которого соединен с выходом первого делителя, выход первого вычитателя соединен с четвертым информационным входом коммутатора, выход которого соединен со вторым информационным входом мультиплексора, выход ключа является информационным выходом анализатора, выход третьего элемента И соединен с вторым управляющим входом первого ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| ПРОЦЕССОР С МАКСИМАЛЬНО ВОЗМОЖНОЙ ПРОИЗВОДИТЕЛЬНОСТЬЮ ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2005 |

|

RU2290687C1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ДРОНОМ СОПРОВОЖДЕНИЯ ВОДОЛАЗА | 2017 |

|

RU2672505C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Арифметическое устройство | 1984 |

|

SU1229754A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

Авторы

Даты

1992-04-15—Публикация

1988-12-19—Подача