лительных блоков по п блоков в каждой. Каждый вычислительный блок содержит четыре входных регистра 3, 25, 4 и 26, четыре преобразователя код - напряжение 1, 23, 2 и 24, два узла 5 и 27 выбора знакового разряда большего по абсолютному значению числа из входных регистров, выполненных на логических элементах, два шифратора 18 и 37, согласующие элементы 21 и 22, кодоуправляемый сумматор 52, преобразователь напряжение - код 53 и пять

Изобретение относится к технике вычислительных преобразователей информации и может быть использовано как вычислительное устройство, работающее в реальном масштабе времени в различных системах управления и в устройствах обработки сигналов и случайных процессов.

Целью изобретения является расширение функциональных возможностей преобразователя .за счет реали5.ации алгебраических, дифференциальных и интегральных преобразований суммы и разности таблично заданных функций и операций дисперсионного и корреляционного анализа.

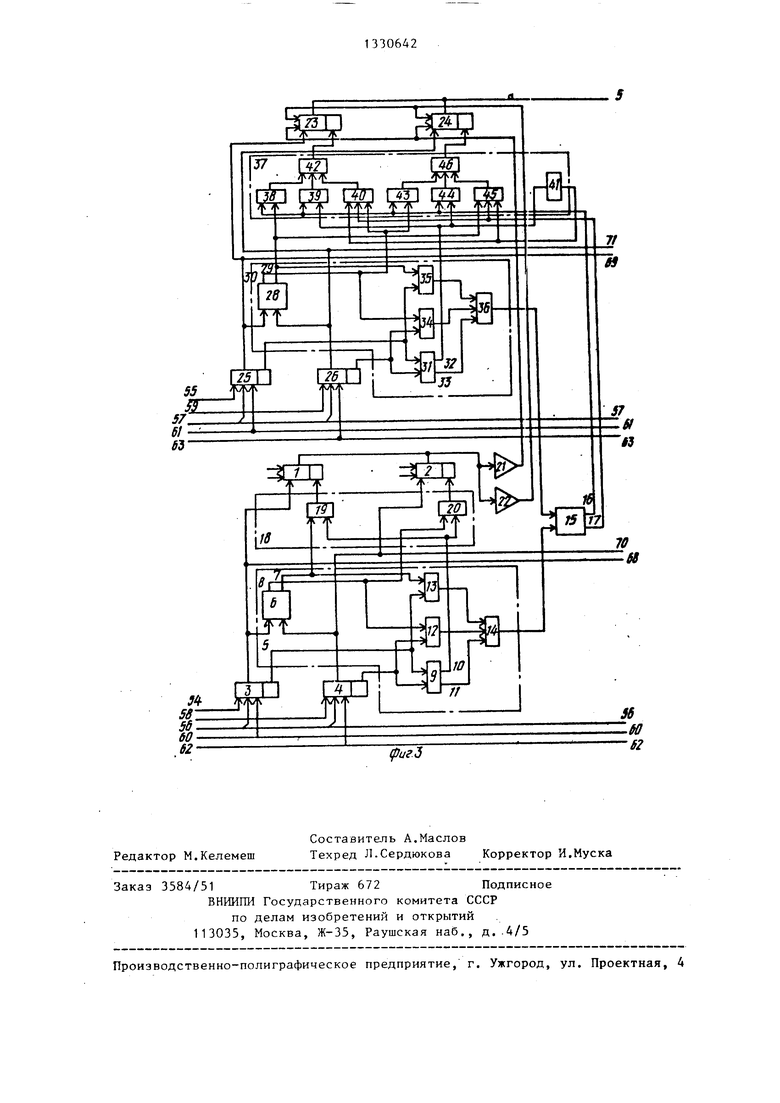

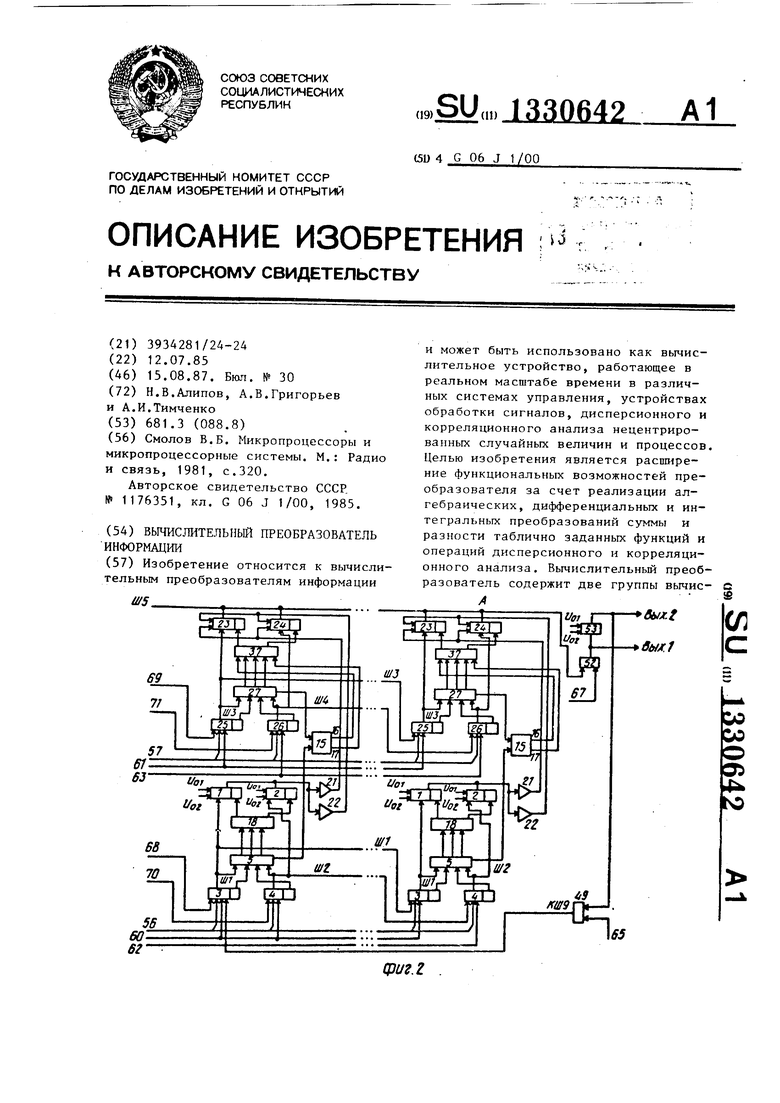

На фиг. 1 и 2 приведена функциональна схема вычислительного преобразовател информации; на фиг.З - то же, вычислительного блока.

Схема вычислительного преобразователя информации (ВШ ) содержит 2п вычислительных блоков (ВБ), которые своими выходами объединены. На схеме (фиг.1) i-й вычислительный блок выделен пунктиром.

Любой i-й вычислительный блок (фиг.1-3) содержит первьй и третий преобразователи код - напряжение (ПКН) 1 и 2; первый и третий входные регистры 3 и 4; узел 5 выбора знакового разряда большего по абсолютному значению числа из регистров 3 и 4, включающий цифровой компаратор 6 с двумя выходами 7 и 8, на первом вьгхо де 7 появляется сигнал тогда, когда число из регистра 3 больше или равно числу регистра 4, на втором выходе

блоков элементов И для связи групп вычислительных блоков между собой. Поставленная цель достигается за счет изменения структуры каждого из вычислительных блоков, входящих в состав вычислительного преобразователя информации, направленного на то, чтобы каждьй вычислительный блок реализовал операции над скобочными формами, а также введением дополнительных шин синхронизации, кодовых шин и шин управления. 3 ил.

0

5

0

Ь

0

5

8 - сигнал тогда, когда число из регистра 4 больше числа из регистра 3; первый элемент И 9, на первом выходе 10 которого появляется сигнал в том случае, когда числа регистров 3 и 4 имеют равные знаки (знаковые разряды регистров и ПКН выделены), а на втором его выходе 11 в такой ситуации появляется сигнал, эквивалентный значению знакового разряда чисел из регистров 3 и 4 второй элемент И 12, входы которого подсоединены к выходу

8цифрового компаратора 6 и к цифровому выходу знакового разряда третьего входного регистра 4; третий элемент И 13, входы которого подсоединены к выходу 7 цифрового компаратора 6 и цифровому выходу знакового разряда первого входного регистра 3; элемент ИЛИ 14, входы которого подсоединены к выходам логических элементов

И 12, 13 и к выходу. 11 элемента И 9, а его выход - к входу сумматора 15 по модулю два, используемого для формирования результирующего знака и имеющего два выхода: первый (инверсный) 16 и второй (прямой) 17J первый шифратор 18 для коммутации знаковьЕХ разрядов ПКН 1 и 2, содержащий пер- вьм элемент ИЛИ 19, входы которого подсоединены к выходу 10 элемента И

9и к выходу 7 цифрового компаратора 6, а его выход подключен к входу знакового разряда ПКН 1, второй элемент ИЛИ 20, входы которого подсоединены

к выходу 10 элемента И 9 и к выходу В цифрового компаратора 6, а его выход - к входу знакового разряда ПКН

2 (логическая единица на выходах элементов ИЛИ 19,20 соответствует знаку , логический нуль - знаку -).

Любой i-й вычислительный блок содержит также первый и второй согласующие элементы 21 и 22 (усилитель 21 является повторителем сигнала, поступающего на его вход из ПКН 1 и 2, а уси- Ю ДУЛю два и выходу 32 литель 22 инвертирует знак сигнала, поступающего на его вход из ПКН 1 и 2); второй и четвертый ПКН 23 и 24, выходы которых объединены; второй и четвертый регистры 25 и 26; узел 27 выбора знакового разряда большего по абсолютному значению числа из регистров 25 и 26, включающий в себя цифровой компаратор 28 с двумя выходами 29 и 30 (на первом выходе 29 появляется сигнал тогда, когда число из регистра 25 больше или равно числу из регистра 26, на втором выходе 30 - сигнал тогда, когда число из регистра 26 больше числа из регистра 25), первый элемент И 31, на первом выходе 32 которого появляется сигнал в том случае, когда числа из регистров 25 и 26 имеют равные знаки, а на втором выходе 33 в такой ситуации - сигнал, эквивалентный значению знакового разряда чисел из регистров 25 и 26, второй элемент И 34, входы которого подсоединены к выходу 30 цифрового коммектов И 38-40, а ег чен к входу знаковог 23, четвертый элемен которого подключены матора 15 по модулю д 30 цифрового компара элемент И 44, входы чены к выходу 16 сумм

шестой элемент И 45, подключены к выходу паратора 28, к выход и к выходу 17 суммат

15 два, второй элемент которого подсоединен ментов И 43-45, а ег знакового разряда ПК

Преобразователь и

20 чает в себя также пе третий, четвертый и ментов И соответстве доуправляемый суммат шесть информационных

25 четыре входа 60-63 с

три входа 64-66 зада ты. Вход 67 кодоупра тора 52 является вхо квантования ВПИ. Пер седних ВБ связаны ме 68, вторые регистры тьи регистры - шинам регистры - шинами 71

Взаимодействие бл

30

паратора 28 и к выходу знакового раз- 35 информации в преобразователе информа- ряда регистра 26, третий элемент И ции осуществляется следующим образом.

к

35, входы которого подсоединены к выходу 29 цифрового компаратора 28 и выходу знакового разряда регистра 25, элемент ИЛИ 36, входы которого подключены к выходам элементов И 31,34, 35, а его выход - к входу сумматора 15 по модулю два, второй шифратор 37 для коммутации знаковых разрядов ПКН 23 и 24, содержащий первый элемент И 38, входы которого подсоединены к выходу 16 сумматора 15 по модулю два и к выходу 29 цифрового компаратора 28, второй элемент И 39, входы котоПодлежащая обработке цифровая информация в виде т-разрядных чисел N(, N, N и N параллельно поступает

40 на третий и четвертый информационные входы 56 и 57 преобразователя информации, являющиеся одновременно вторыми входами первых, вторых, третьих и четвертый регистров 3,25,4 и 26

45 всех 2п вычислительных блоков, либо - последовательно на первый, второй, пятый и шестой входы 54 - 59 преобразователя информации, являющиеся первыми входами регистров 3,25,4 и

рого подключены к выходу 16 сумматора 50 первого вычислительного блока,

15 по модулю два и к выходу 32 эле- При последовательном занесении информента И 31, третий элемент И 40, входы которого подключены к второму выходу 17 сумматора 15 по модулю два, к выходу 30 цифрового компаратора 28 и к выходу инвертора 41, вход которого подсоединен к выходу 32 элемента И 31, первый элемент ИЛИ 42, входы которого подсоединены к выходам элеДУЛю два и выходу 32

мектов И 38-40, а его выход подключен к входу знакового разряда ПКН 23, четвертый элемент И 43, входы которого подключены к выходу 16 сумматора 15 по модулю два и к выходу 30 цифрового компаратора 28, пятый элемент И 44, входы которого подключены к выходу 16 сумматора 15 по моэлемента И 31,

шестой элемент И 45, входы которого подключены к выходу 29 цифрового компаратора 28, к выходу инвертора 41 и к выходу 17 сумматора 15 по модулю

два, второй элемент ИЛИ 46, входы которого подсоединены к выходам элементов И 43-45, а его выход - к входу знакового разряда ПКН 24.

Преобразователь информации вклю-

0 чает в себя также первый, второй, третий, четвертый и пятый блоки элементов И соответственно 47 - 51, ко- доуправляемый сумматор 52, ПНК 53, шесть информационных входов 54-59,

5 четыре входа 60-63 синхронизации,

три входа 64-66 задания режимов работы. Вход 67 кодоуправляемого сумматора 52 является входом задания шага квантования ВПИ. Первые регистры соседних ВБ связаны между собой шинами 68, вторые регистры - шинами 69, третьи регистры - шинами 70 и четвертые регистры - шинами 71.

Взаимодействие блоков и обработка

0

Подлежащая обработке цифровая информация в виде т-разрядных чисел N(, N, N и N параллельно поступает

на третий и четвертый информационные входы 56 и 57 преобразователя информации, являющиеся одновременно вторыми входами первых, вторых, третьих и четвертый регистров 3,25,4 и 26

всех 2п вычислительных блоков, либо - последовательно на первый, второй, пятый и шестой входы 54 - 59 преобразователя информации, являющиеся первыми входами регистров 3,25,4 и

55

мации возможно независимое перемещение информации вдоль регистров 3,25, 4 и 26 всех вычислительных блоков за счет того, что выходы первых, вторых, третьих и четвертых регистров 3,25, 4 и 26 i-ro вычислительного блока соединены г. первыми входами первых 3, соответственно вторых 25, третьих 4

5133064

и четвертых 26 регистров (1+1)-гоВБ. Занесение, а также независимое перемещение чисел N,, NJ, NJ и N вдоль всех вычислительных блоков 2п возможно только при подаче синхроимпульсов (СИ) на входы 60-63 синхронизации (сдвига), которые соответственно соединены с первыми 3, вторыми 25, третьими 4 и четвертыми 26 регистрами всех ВБ.

10

В каждом i-M вычислительном блоке информация обрабатывается следующим образом.

В первый 3, второй 25, третий 4 и четвертый 26 регистры заносятся соответственно числа N, N3, N, N, имеющие знаковые разряды. Регистры 3,4,25 и 26 своими выходами соответственно подключены к цифровым входам ПКН 1,2,23 и 24. Полярность напряжения на выходе ПКН 23 и 24 соответствует результирующему знаку перемножаемых скобок. ((У, N, lyjNj ) (oijNj+ci N) где о(., , 06 f , знаковые разря ды. Полярность напряжения на выходе ПКН 23 и 24 определяется выходными сигналами узла 5 выбора знакового разряда больщего по абсолютному значени числа из регистров 3 и 4, шифратора 18, сумматора 15 по модулю дв, согласующих элементов 21 и 22, выходы которых соответственно подключены к первым и вторым аналоговым (умножающим) входам положительного и отрицательного напряжений ПКН 23 и 24, узл 27 выбора знакового разряда большего по абсолютному значению числа из ре- гистоов 25 и 26, шифратор 37.

-

При этом на выходах узлов 5 и 27 появляются цифровые сигналы Г; и у. , для которых

Х.:, если Ы.,; 0(.j;

где 2п - число блоков. Из точки А сигнал подается на аналоговый вход кодоуправляемого сумматора 52, масштаб которого может изменяться путем задания чисел N и N

- 1 / I ; I f 45 - цифровом входе так, что на его

л,., если 06,; /oL,;; и /N,;|i/N,i/ (1) выходе (1) формируется напряжение.

LO,;.

IV,,

если ot,,; cij; и / N, N,;/, j,, если ( 0,4;

Otj;, еСЛИоб,; 4ci4 И /N, (2) oi.;, еСЛИО,; /Ы4;И I . J- I J ;

на выходе сумматора 15 по модулю два - цифровые сигналы z;, z;, для которых z; r;®y; Z; Г; @у.; (3) на выходах шифратора 18 коммутации знаковых разрядов ПКН 1 и 2 - сигналы 3,i и которых

l, если /N,.,;/ Hcd,i ° 1, если (X,; (4)

р.равное

U,,,,KN, Z ,;/Nj+|i,JN,,; /N,;/ +

50 ,;| ,(11)

которое является аналоговым выходом преобразователя информации.

Выход сумматора 52 подключен к входу ПНК 53, на выходе которого (выход 2) образуется двоичный цифро55

-1, еслис,; oL-,( И / N,/ ,

вой эквивалент напряжения U рый равен

.«„/К2

вых,

кото(12)

П, если oi,; с,. и /N,j/ /Nj;/ j; 1, если oi,;(5)

, если/М,;/Ь/Nj,;/ ио,; oi,; a на объединенных выходах ПКН 1 и 2 формируется напряжение

U,(fi,rN,; +/3,; N,;), (6) где K Ujj/2 - коэффициент преобразования,

на выходе шифратора 37 коммутации знаковых разрядов ПКН 23 и 24 формируются два сигнала J,,; и jf ;, для которых

1, еслио 5; и

1, если /N,i/5:/N,j/,o6,,

1, если /Nii/ /N /.odjif ot ;, z-«0 (7)

-1, если /N,i/ / N4i/,otj; ot,, z; 1

-1, еслиаб, ,

5 2030

40

25

1,если 06j; ei, и

1,если /N,i| /N4i/,

1,если /N,/ь|Nц,|,вiз

-1,если /N,i| /N4;/;od,; «сц;; (8)

-1,еслиог.. и Z; 0,

a на объединенных выходах преобразователей ПКН 23 и 24 формируется напряжение

jrK { ;/N,,,; /N,;/4

f,;lN,;/ ,(9)

где K,K /2 Uo /2 Своими выходами все вычислительные блоки гальванически соединены в одну , точку А, в которой формируется напряжение и, равное

7 п

U,K,/2nj: p,/N,;/-H jNji/j y3i/N,;/ - Ь К;У}(10)

где 2п - число блоков. Из точки А сигнал подается на аналоговый вход кодоуправляемого сумматора 52, масштаб которого может изменяться путем задания чисел N и N

равное

U,,,,KN, Z ,;/Nj+|i,JN,,; /N,;/ +

50 ,;| ,(11)

которое является аналоговым выходом преобразователя информации.

Выход сумматора 52 подключен к входу ПНК 53, на выходе которого (выход 2) образуется двоичный цифро55

эквивалент напряжения U равен

.«„/К2

вых,

кото(12)

1

где - масштаб преобразования преобразователя 53; разрядность преобразователя 53.

Подставляя в вьфажение (12) вместо его значение, полученное из формулы (11), после преобразований получим соотношение

, I p,./N J -./N,,,;/N,,.//

/N,;/J V (13)

Информация с ПКН 53 при наличии разрешающего сигнала на входе 65 задания режимов работы через блок элементов И 49 поступает на третий вход первого регистра 3(п+1)-го вычислительного блока. Все 2п блоков разделены на две секции: от 1 до п-го и от (п+1)- го до 2п-го блока. Секции при наличии разрешающих сигналов на первых 64 и на третьих 66 входах задания режимов работы соединяются между собой через блоки элементов И 47,48,50,51.

Вычисления в предлагаемом преобра- зователе информации осуществляется на базе следующих элементарных операций.

1. Операция сложения первой и второй, третьей и четвертой функции и умножения полученных сумм функций, отсчеты которых записаны соответственно Б регистры 3,4,25 и 26 вычислительных блоков. При этом отсчеты функций могут быть занесены либо параллельно за один такт во все реги- стры по входам 54 и 57, либо последовательно за 2п тактов по входам 54, 58,55,59.

После полного занесения информации во все регистры 3,4,25 и 26 на цифро- вом выходе преобразователя информа

рого определяется выражением

2п

K3N,i:(x;+A;)(y,-+B,-) ,. ,

где К,

х,А-,у-,В. - соответственно циф- 15овые отсчеты первой, второй, третьей и четвертой функции.

В случае обработки информации в реальном масштабе времени соотношение (14) для момента t записывается в виде

K,N,,|l(x..,M.,)(y;,,-HB.,)

N

(15)

5,t

2, Операция занесения информации по синхроимпульсу в момент t на первый регистр 3 первого ВБ через вход 54 с одновременной передачей (сдвигом) информации с первого регистра 3 (i-l)-ro ВБ на первый регистр 3 i -ro ВБ.

Условимся эту операцию обозначить

5

°

Л

.-t .-t

х

-

Х;

t

если 1 если

i 1,

(16)

s-i,i-(

где х; - код, поступающий на вход 54 ВПИ и на первый вход первого регистра 3 первого ВБ в момент t (стрелка над числом обозначает сдвиг на первых регистрах 3 этого числа по синхроимпульсу) .

При выполнении такой операции преобразователь информации осуществляет преобразование информации для момента t в соответствии с соотношением

0 5

5

,1

N

y.t

ZL(x,,M,)(y,,B.). (17)

1

3. Операция занесения информации А. либо У;, либо В; по синхроимпульсу в момент t соответственно на третий регистр 4 или второй регистр 29, или четвертый регистр 26 первого ВБ соответственно через вход 58 или 55, или 59 с одновременной передачей (сдвигом) информации соответственно с третьего регистра 4 (1-1)-го ВБ на третий регистр 4 i-ro ВБ или с второго J регистра 25 (i-1)-ro ВБ на второй регистр 25 i-ro ВБ, или с четвертого регистра 26 (i-l)-ro ВБ на четвертый регистр 26 i-ro ВБ.

Условимся эту операцию обозначать

(18)

R S-. - 5 i.t .,., , если

0

5

где

5

, если используется вход 58; У;, если используется вход 55;

L.-.t.

если используется вход 59.

R - код, поступающий на вход 58 или 55, или 59 соответственно на вход третьего регистра 4 или второго регистра 25, или четвертого регистра 26 первого ВБ ( fА,у,). Стрелка над числом R;, обозначает сдвиг на регистрах 4 или регистрах 25, или регистрах 26 этого числа по синхроимпульсу.

При выполнении этой операции преобразователь информации осуществляет для момента t преобразование информации в соответствии с одним из вьфа- жений:

91330642

информация поступает по входу 58

K,N,t -2

Z:(x.,M..,)(y,,,-bB,.,); (19)

информация поступает по входу 55 K.N

М, J p,Mt. если

- Lf p.,,-tM . если р Т, М Z , 1 J

J Zj. i- ,i4 если ,

(23)

fO

где MI - код, поступаемый в момент t на вход 54 или 58, или 55, или 59 соответственно на вход первого 3 или третьего А, или второго 25, или четвертого 26 регр.стров первого ВБ (Мб х, А, у, .

При выполнении этой операции преобразователь информации осуществляет разнообразные преобразования информа- ( ) (7,-,+В; ). (22) J5 ции, заданные :оотношениями:

Zt 4---- i,,t)(.,t); (20)

Fi t: 1 1

информация поступает по входу 59

ё(х.,М,.,)(у;,, -.t); (21)

информация одновременно поступает по входам 58,55,59 K,N

2ti

3 6,-Ь

,t

С учетом первой элементарной операции возможны и другие комбинации перемещения информации вдоль первых 3, третьих 4, вторых 25 и четвертых 26 регистров.

Число возможных комбинаций перемещения информации вдоль регистров соответствует, 15 (четыре для случая, когда информация перемещается вдоль одной одноименной группы регистров; шесть для случая, когда информация перемещается вдоль двух одноименных групп регистров; четыре для случая, когда информация перемещается вдоль трех одноименных групп регистров одна для случая, когда информация перемещается вдоль четьфех одноимен- ных групп регистров).

4. Операция занесения информации х либо А, либо у, по синхроимпульсу в момент t . соответственно на первый 3 либо на третий 4, либо на второй 25, либо на четвертый 26 регистры первого ВБ соответственно либо по входу 55, либо по входу 58, либо по входу 54, либо пс входу 59 и занесение информации z по синхроК N

Z,

6,-t Г JL ,0 о , о т

р

{|(xj,,M.,,)(y.,,Bj,,) , (24),

20 где Xp,,i; p., V Ai,,t. yp.,t. Ур.Л; У СУ;Л yj. Врде{в ,, Вр,,; .Bj.tffBj.t, Bj.i} .

25 Условная

п

6

запись.

к

, (),t}

примеру,

о

означает, что х

P,t либо

может принимать значение Хрд, значение З. .

Соотношение (24) описывает доста30 точно большое множество различных преобразований информации, расположенной в преобразователе информации, время выполнения всех элементарных операций равно периоду следования

г синхроимпульсов по входам 60-63 синхронизации. Информация с выхода блока элементов И 49 поступает только при реализации элементарной операции (23),

4Q Выполнение рассмотренных вьщю элементарных операций, на базе которых обуществляется преобразование информации, расположенной в регистрах преобразователя информации, в виде пре- импульсу в момент t по третьему вход 45 образований (15), (17), (19)-(22), в первый регистр 3 (п+1)-го ВБ с од- (24) обеспечивается в зависимости от новременным сдвигом информации с пер- различных комбинаций сигналов на ин- вого регистра 3 либо третьего реги- формационных входах 54-59, входах стра 4, либо второго регистра 25, 64-65 задания режимов работы и вхо- либо четвертого регистра 26 (р-1)-го 50 60-63 синхронизации реализации ВБ соответственно в регистр 3 либо в натуральном масштабе времени опе- в регистр 4, либо в регистр 25, либо рации алгебраического сложения, умножения и деления двух чисел, интегрирования, дифференцирования, вычисле- 35 ния корреляционной функции центрированного эргодического случайного процесса, прямого преобразования Фурье, операции фильтрации в соответствии с адгоритмами работы нерекурсивного

в регистр 26р-го ВБ (,2,...,q; п-1, ) и сдвигом информации с первого регистра 3 (j-1)-ro ВБ в первый регистр 3 j-ro ВБ (j(n+1), (п+2), (п-|-23)...(2п)).

Условно эту операцию обозначим так:

10

М, J p,Mt. если

- Lf p.,,-tM . если р Т, М Z , 1 J

J Zj. i- ,i4 если ,

(23)

К N

Z,

6,-t Г JL ,0 о , о т

р

{|(xj,,M.,,)(y.,,Bj,,) , (24),

20 где Xp,,i; p., V Ai,,t. yp.,t. Ур.Л; У СУ;Л yj. Врде{в ,, Вр,,; .Bj.tffBj.t, Bj.i} .

5 Условная

п

6

запись.

к

, (),t}

примеру,

о

означает, что х

P,t либо

может принимать значение Хрд, значение З. .

Соотношение (24) описывает доста0 точно большое множество различных преобразований информации, расположенной в преобразователе информации, время выполнения всех элементарных операций равно периоду следования

г синхроимпульсов по входам 60-63 синхронизации. Информация с выхода блока элементов И 49 поступает только при реализации элементарной операции (23),

И133064

или рекурсивного цифрового фильтра, а также реализация операций над скобочными формами, таких как умножение числа на скобку, умножение скобок, интегри 5ование, диф(1)еренцирование и разности двух функций, операции корреляционного и дисперсионного анализа нецентрированных случайных величин и процессов.

Формула изобретения

Вычислительный преобразователь информации, содержащий первьш, второй и третий блоки элементов И, преобразователь напряжение - код, кодо- управляемый сумматор и 2п вычислительных блоков, каждый из которых содержит первый и второй входные регистры, первый и второй преобразователи код - напряжение, первый согласующий элемент и сумматор по модулю два, информационный вход первого преобразователя код - напряжение соединен с информационным выходом первого входного регистра, а его выход подключен через первый согласующий элемент к первому аналоговому входу второго преобразователя код - напряжение, цифровой вход которого подключен к информационному выходу второго входного регистра; выходы вторых преобразователей код - напряжение всех вычислительных блоков соединены между собой и подключены к аналоговому входу кодоуправляемого сумматора, цифровой вход которого является входом задания шага квантования вычислительного преобразователя, а выход подключен- ко входу преобразователя напряжение - код и является аналоговым выходом вычислительного преобразователя, причем 2п вычислительных блоков разделены на две группы по п вычислительных блоков в каждой группе, информационные выходы первых и вторых регистров i-ro вычислительного блока в каждой группе соединены с первыми информационными входами соответственно первого и второго входных регистров (i+1)-ro вычислительного блока, первые информацион- ,ные входы первого и второго входных регистров первого вычислительного блока являются первым и вторым информационными входами вычислительного преобразователя, вторые информаци энные входы соответственно первых и вторых входньгх регистров всех вы5

5

4

0

5

0

5

0

5

212

числительных блоков объединены и являются соответственно третьим и четвертым информационными входами вычислительного преобразователя, входы синхронизации первых и вторых входных регистров соответственно объединены и является соответственно первым и вторым входами синхронизации вычислительного преобразователя, первые входы первого и второго блоков элементов И объединены и являются первым входом задания режима работы вычислительного преобразователя, их вторые входы соединены с информационными выходами соответственно первого и второго входных регистров п-го вычислительного блока, а выходы подключены к первым информационным входам соответственно первого и второго входньгх регистров (п+1)-го вычислительного блока, один из входов третьего блока элементов Н является вторым входом задания режима работы вычислительного преобразователя, а его другой вход и выход подключены соответственно к выходу преобразователя напряжение - код и к третьему информационному входу перво- входного регистра (п+1)-го вычислительного блока, выход преобразователя напряжение - код является цифровым выходом вычислительного преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации алгебраических, дифференциальных и интегральных преобразований суммы и разности таблично заданных функций и операции дисперсионного и корреляционного анализа, он содержит четвертый и пятый блоки элементов И и в каждом вычислительном блоке третий и четвертьш входные регистры, третий и четвертьй преобразователи код - напряжение, второй согласующий элемент, первый и второй шифраторы и первый и второй узлы выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах, каждьп из которых выполнен в виде цифрового компаратора, первого, второго и третьего элементов И и элемента ИЛИ, три входа которого подключены соответственно к одному из выходов первого элемента И и к выходам второго и третьего элементов И, другие выходы первых элементов И первого и второго узлов выбора знаковых разрядов больших по абсолютному значению чисел во входных

регистрах соединены с первыми входам соответственно первого и второго раторов, первые входы первого и второго и первый вход третьего элементов И первого узла выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах подключены к выходам знаковых разрядов соответственно третьего и первого входных регистров соответствующего вычислительного блока, первые входы первого и второго и первый вход третьего элементов И второго узла выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах - к выходам знаковых разрядов соответственно четвертого и второго входных регистров соответствующего вычислительного блока, первый вход третьего и второй вход первого элементов И в каждом узле выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах объединены, а вторые входы третьих и вторых элементов И по;;ключены в каждом из этих узлов соответственно к первому и второму выходам цифровых компараторов, входы цифровых компараторов первого и второго узлов выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах в каждом вычислительном блоке подключены, к информационным выходам соответственно первого и третьего и второго и четвертого входных регистров этих блоков, а их выходы соединены соответственно со вя орыми и третьими входами соответствующих шифраторов, информационные входы третьего и четвертого преобразователей код - напряжение подключены к информационным выходам соответственно третьего

5

0

5

0

5

0

И четвертого вхэдных регистров, два выхода первого шифратора подключены в каждом вычислительном блоке к входам знаковых разрядов соответственно первого и третьего преобразователей код - напряжение, выходы которых объединены и подключены через первый и второй согласукщие элементы соответственно к первому аналоговому входу четвертого и к вторым аналоговым входам второго и четвертого преобразователей код - напряжение, выходы которых объединены, четвертый и пятый входы второго шифратора подключены соответственно к первому и второму выходам сумматора по модулю два, а два его выхода - к входам знаковых разрядов соответственно второго и четвертого преобразователей код - напряжение, пе1)вые входы четвертого и пятого блоков элементов И объединены и являются третьим входом задания режима работы 1зьмислительного преобразователя, их вторые входы соединены с информационными выходами соответственно третьего и четвертого входных регистров п-го вычислительного блока, а выходы подключены к первым информационным входам соответственно третьего и четвертого входных регистров (п+1)-го вычислительного блока, первые информационные входы третьего и четвертого входных регистров первого вычислительного блока являются соответственно пятым и шестым информационными входами вычислительного преобразователя, входы синхронизации третьих и четвертых входных регистров соответственно объединены и являются соответственно третьим и четвертым входами синхронизации вычислительного преобразователя.

Г

.

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный преобразователь информации | 1983 |

|

SU1176351A1 |

| Комбинированный вычислительный преобразователь информации | 1988 |

|

SU1599849A1 |

| Анализатор спектра | 1986 |

|

SU1691852A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Обратимый преобразователь координат | 1982 |

|

SU1035617A1 |

| Экстраполятор видеосигнала изображения | 1989 |

|

SU1718246A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1589395A1 |

Изобретение относится к вычислительным преобразователям информации и может быть использовано как вычислительное устройство, работающее в реальном масштабе времени в различных системах управления, устройствах обработки сигналов, дисперсионного и корреляционного анализа нецентриро- ванных случайных величин и процессов. Целью изобретения является расширение функциональных возможностей преобразователя за счет реализации алгебраических, дифференциальных и интегральных преобразований суммы и разности таблично заданных функций и операций дисперсионного и корреляционного анализа. Вычислительный преобразователь содержит две группы вычис/4 с (Л Фиг.г

| Смолов В.Б | |||

| Микропроцессоры и микропроцессорные системы | |||

| М.: Радио и связь, 1981, с.320 | |||

| Авторское свидетельство СССР | |||

| Вычислительный преобразователь информации | 1983 |

|

SU1176351A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-15—Публикация

1985-07-12—Подача