Изобретение относится к вычислите льной технике и может быть использовано при построении устройств для решения задач математической физики описываемых уравнениями в частных производных. Известен вычислительный узел цифровой сетки, содержащий процессор, выполняющий последовательно разряд за разрядом, арифметические и логические операции, и два блока памяти емкостью по 2048 единиц каждый 1. Недостаток узла - большое количество оборудования, поскольку каждый вычислительный узел представляет собой универсальную вычислительную Мсшдину, программно настраиваемую на выполнение требуемой последо вательности действий, и низкое быстродействие, ввиду последовательно го способа обработки информации. Наиболее близким к предлагаемому по технической сущности является вычислительный узел цифровой сеточной модели для решения дифференциал ных уравнений в частных производных содержащий многовходовый сумматор, регистр сдвига, элемент И, группу элементов -И и блок умножения.Входы сумматора со инены со входами узла выход сумматора соединен с последовательным входом блока умножения. Параллельные входы блока умножения соединены с группой кодовых входов узла, выход блока умножения соединен с последовательным входом регистра сдвига. Последовательный выход регистра соединен с первым входом элемента И, параллельные выходы регистра сдвига соединены с первыми входами элементов И группы элементов И. Выход элемента И соединен с выходом узла.. Выходы элементов И групп у элементов И соединены с параллельными выходами узла. Управляющие входы регистра и элементов И соединены с управляющими входами узла . Недостаток узла - низкая скорость решения задач, так как узел реализует метод простой итерации решения конечно-разностных уравнений с медленной сходимостью. Поэтому решение уравнений в частных производных с применением узла требует большого количества итераций и больших затрат времени. Цель изобретения - повышение быстродействия. Указанная цель достигается тем, что в вычислительный узел цифровой

сеточной модели для решения дифференциальных уравнений в частных производных, содержащий многовходовой сумматор, первая группа входов котоpofo является первой груггпой информационных входов вьлчислительного узла, блок умножения, группа входовкоторого является входами вычислительного узла,, первый регистр и элемент И, управляющий вход которого является первым управляющим входом вычислительного узла, введены триггер, преобразователь прямого кода в дополнительный, сумматор, второй, третий и четвертый регистры сдвига и коммутаторы, выходы первого из которых подключены ко входам старших разрядов регистров сдвига, выходы младших разрядов регистров сдвига соединены со входами первого, второго/ и третьего коммутаторов, входы четвертого коммутатора соединены с разрядными выходами регистров сдвига, входы являются первой группой управляющих входов вычислительного узла, выходы четвертого коммутатора являются информационньлми выходами вычислительного узла, выходы второго коммутатора подключены ко входу триггера, к первому входу сумматора и ко второй группе входов многовходового сумматора, соответственно, второй вход триггера является вторым управляющим входом вычислительного узла, выход триггера соединен со вторым входом су 1матора, выход которого через преобразователь прямого кода в дополнительный подключен ко входу многовходового сумматора, выход которого соединен с инфо эмационными входами элемента И и первого комутатора, управляющие входы которого являются второй группой управляющих входов вычислительного узла, группа входов пятого коммутатора является второй информационной группой входов вычислительного узла, управляющие входы пятого комму/гатора являются третьей группой управляющих входов вычислительного узла, выход элемента И подключен ко входу блока умножения выход которого соединен со входом пятого коммутатора, управляющие входы sToporo, третьего и четвертого комстаторов являются, соответственно, четвертой, пятой и шестой группой управляющих входов вычислительного узла, выход третьего коммутатора является информационным выходом вычислительного узла.

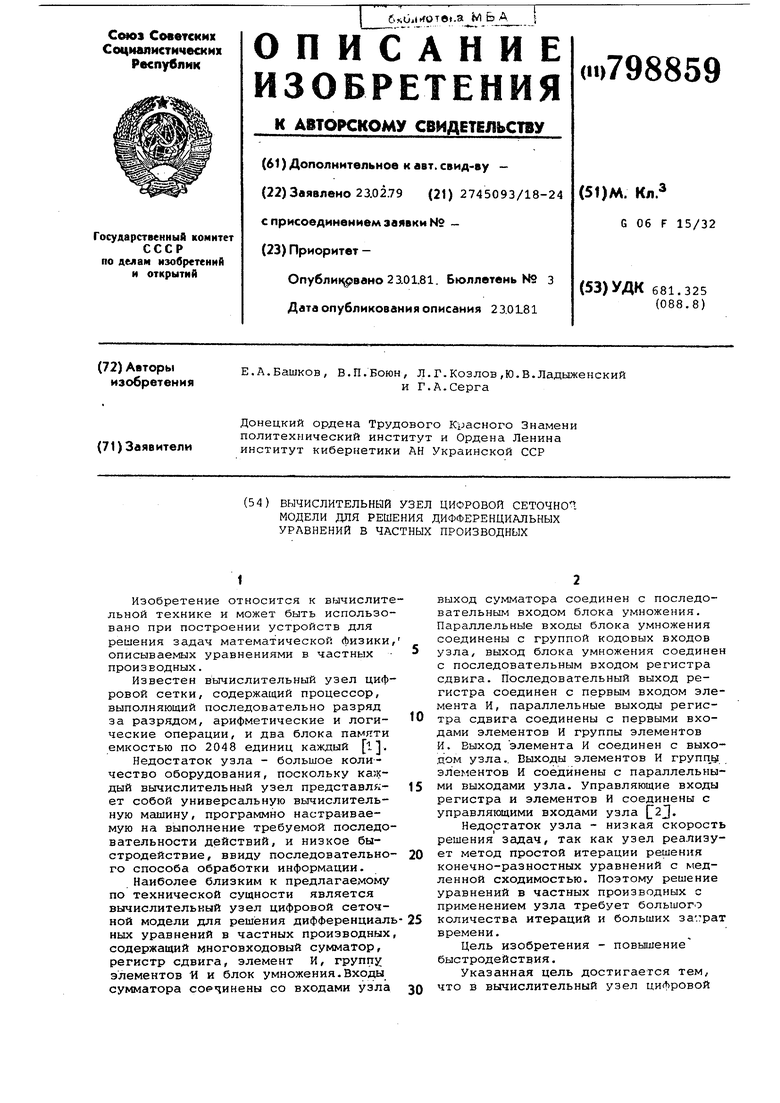

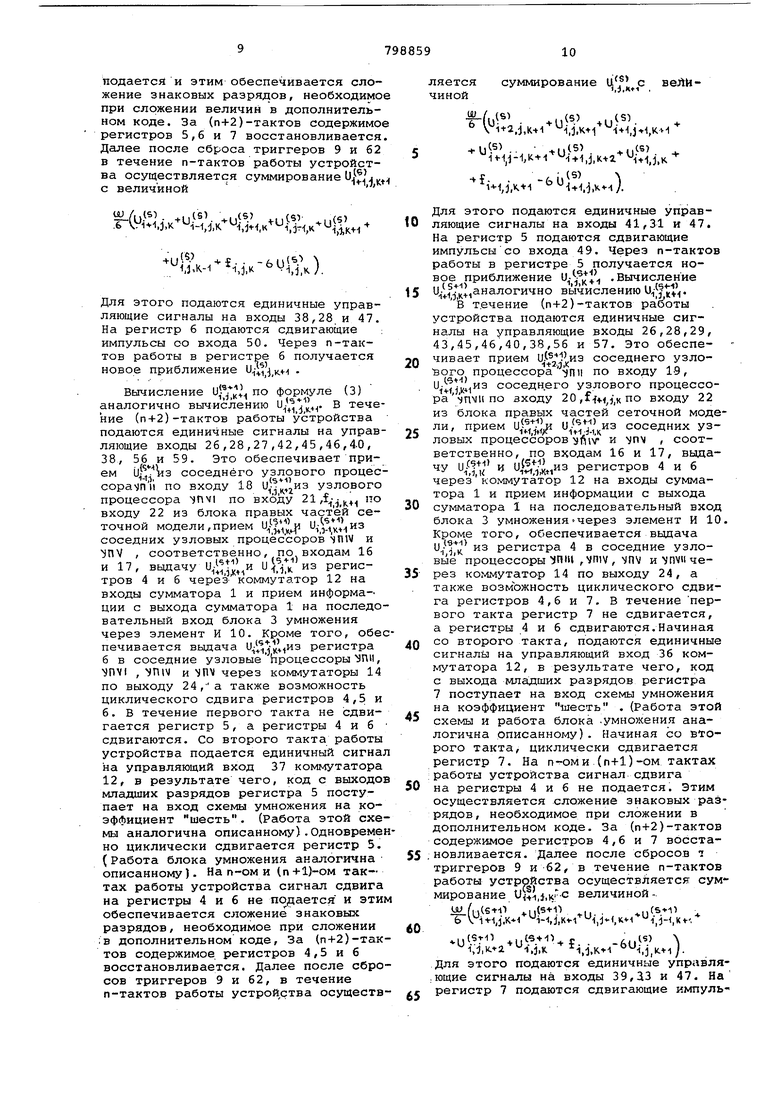

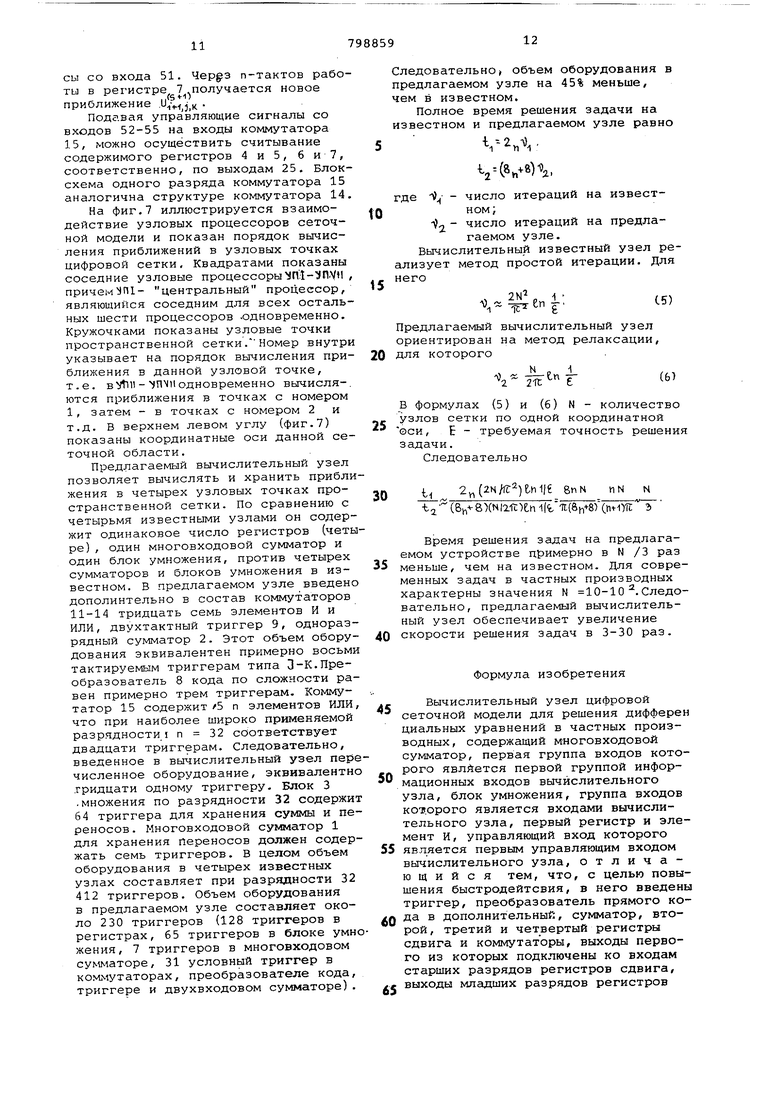

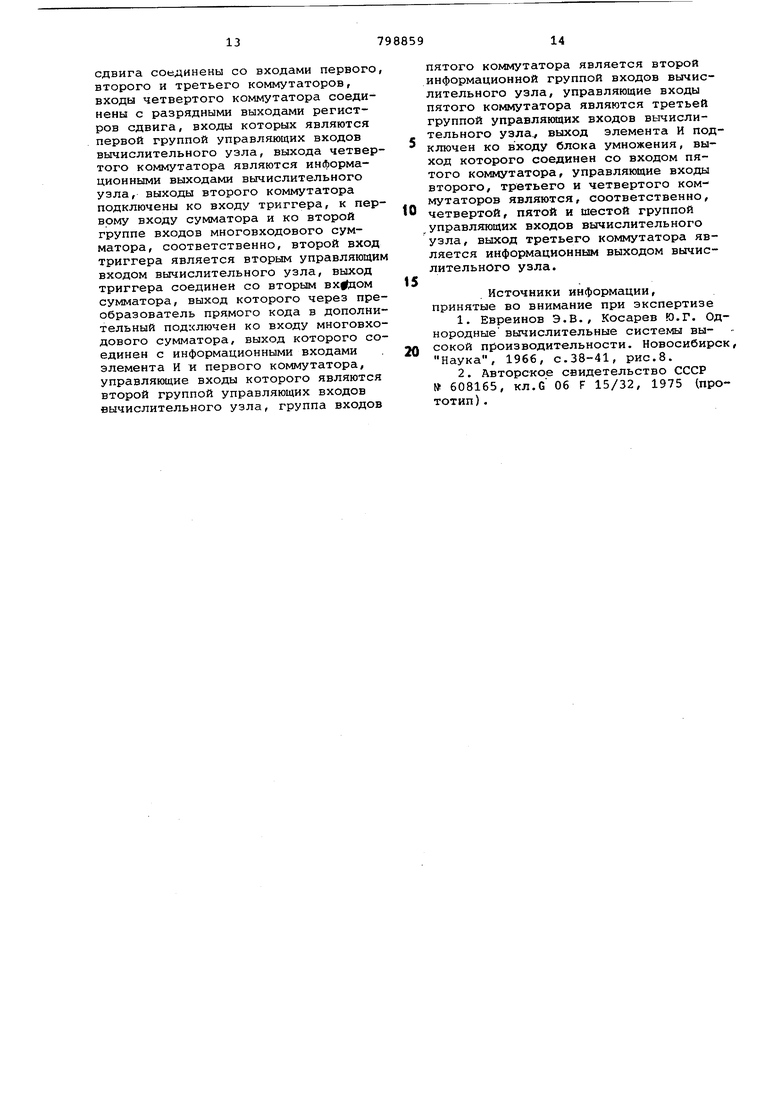

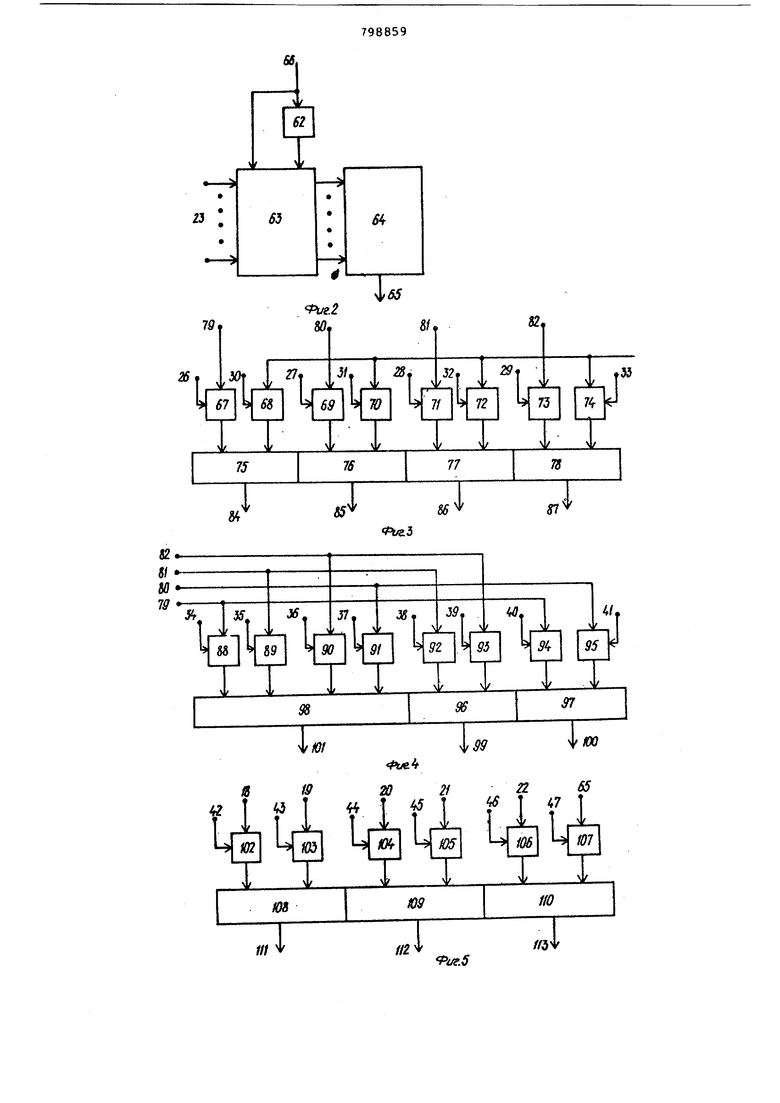

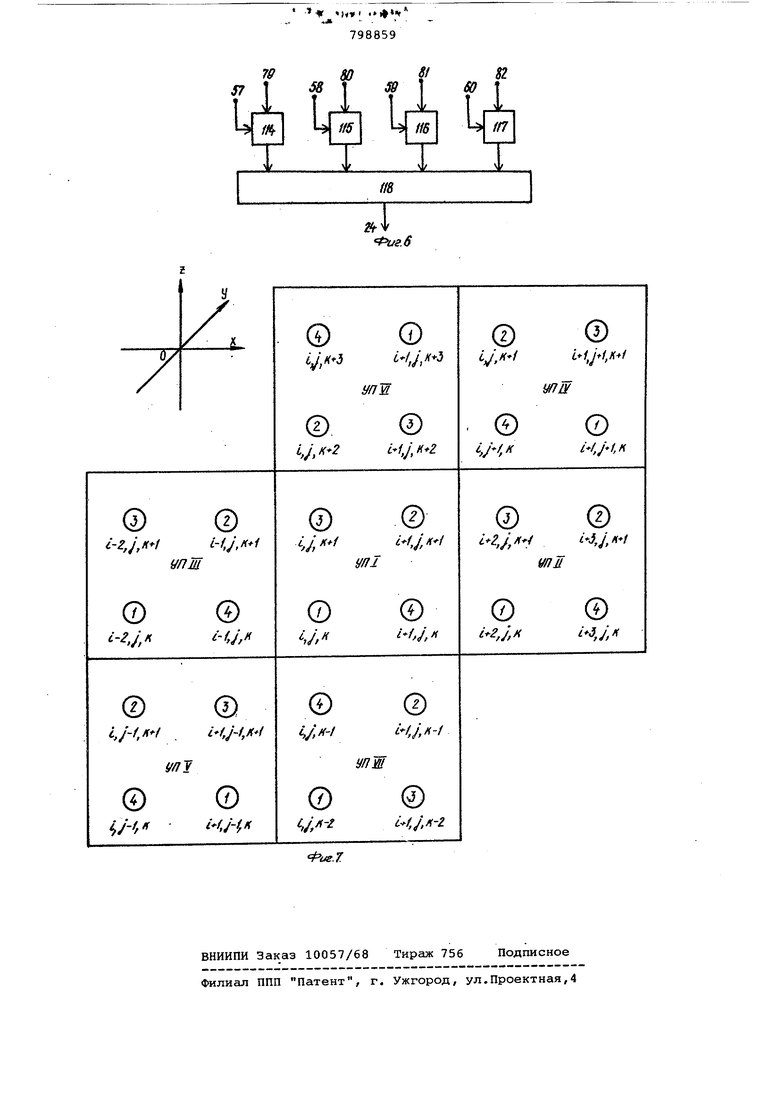

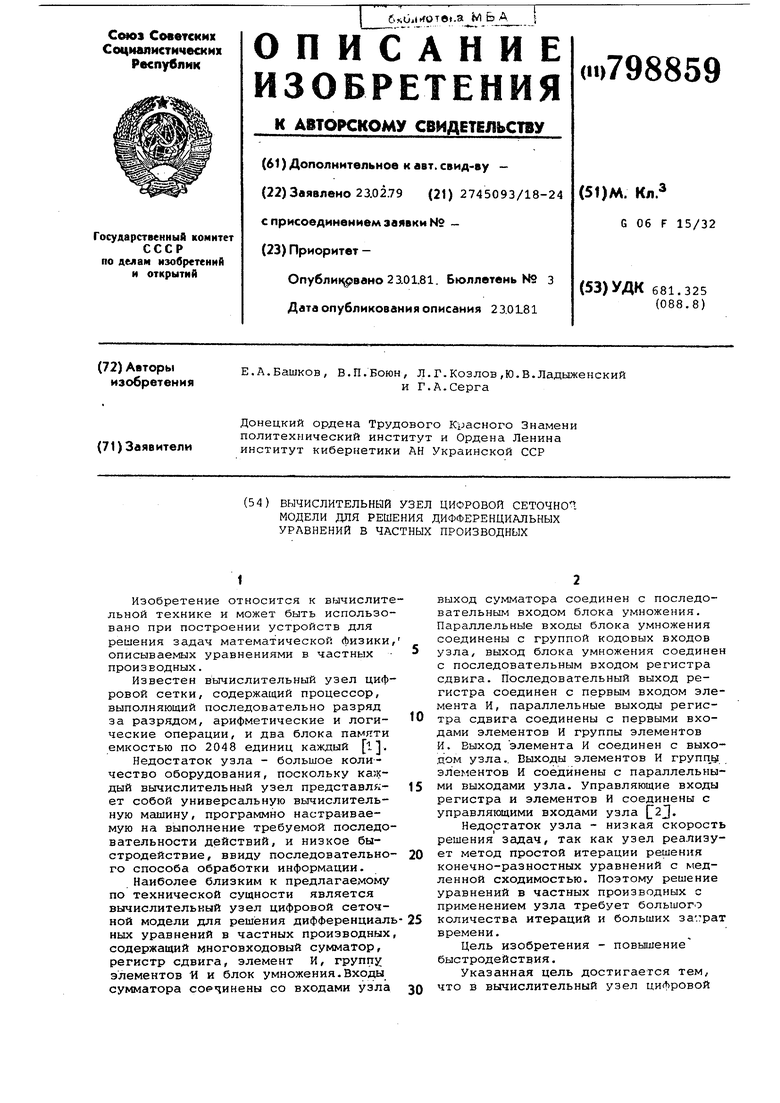

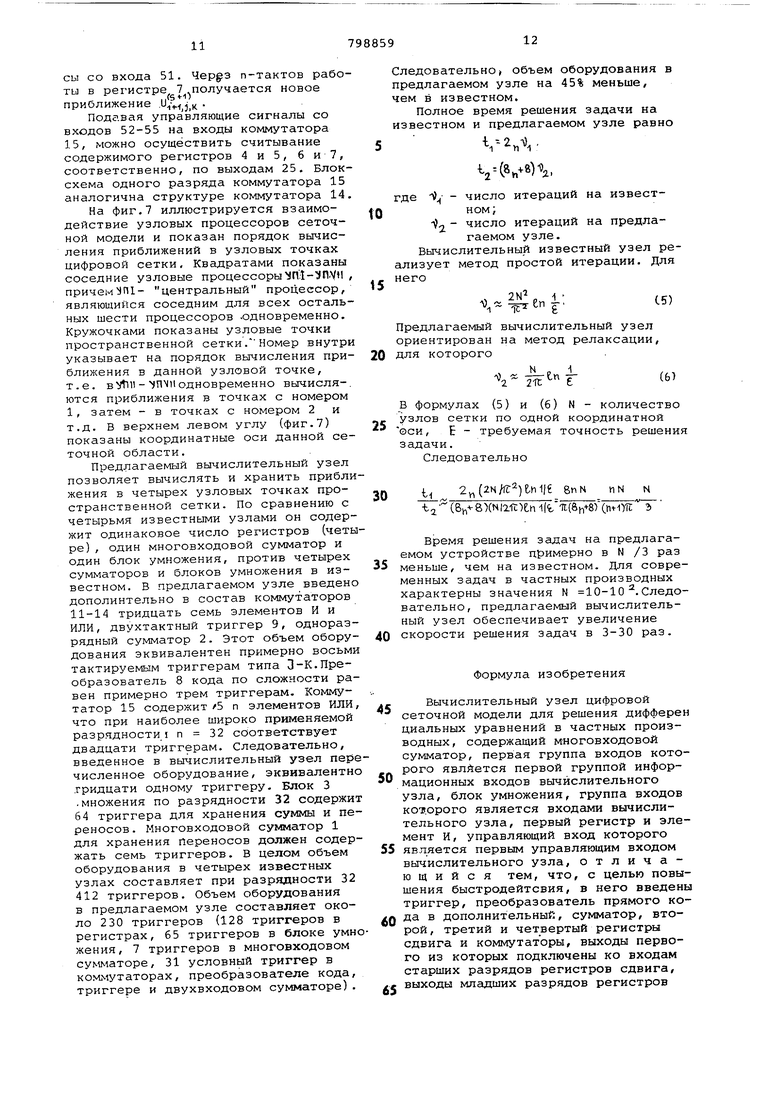

На Лиг.1 показана блок-схема устройства; на фиг.2 - блок-схема умножения ; на фиг. 3-6 - блок-схемы коммут торов-, на фиг. 7 - взаимодействие узловых процессоров (УП) цифровой сетки УП1 -ynvil .

Устройство содержит многовходовой сумматор 1, сумматор 2, .блок 3 умножения, регистры 4-7 сдвига, преобразователь 8 прямого кода в дополнительйый,триггер 9,элемент и 10, коммутаторы 11-15, информационные входы 16-23 узла, информационный выход 24 узла, информационные выходы 25 узла, управляющие входы 26-61 узла.

Входы сумматора 1 соединены со входами 16 и 17- выходами коммутаторов 12 и 13 преобразователя 8 кода, выход сумматора 1 соединен со входом коммутатора 11 и первым входом элемента И 10, выход которого соединен с входом блока 3 умножения, входы которого соединены с информационными входами 23 узла. Выход блока 3 умножения соединен с входом коммутатора 13, остальные пять входов которого соединены с информационными входами 18-22 узла, соответственно. Вход преобразователя 8 кода в дополнительный соединен с выходом сумматора 2, входы которого соединены с выходами триггера 9 и коммутатора 12, первый выход которого соединен со входом триггера 9. Входы коммутатора 12 соединены со входами коммутаторов 11 и 14 и выходами младших разрядов регистров 4-7, входы старших разрядов которых соединены с выходами коммутатора 11. Выход коммутатора 14 соединен с последовательным информационным выходом 24 узла. Выходы регистров 4-7 соединены со входами кo lмyтатора 15, выходы которого соединены с выходами 25 узла. Управляющие входы регистров, коммутаторов, триггера и элемента И соединены с соответствующими управляющими входами узла.

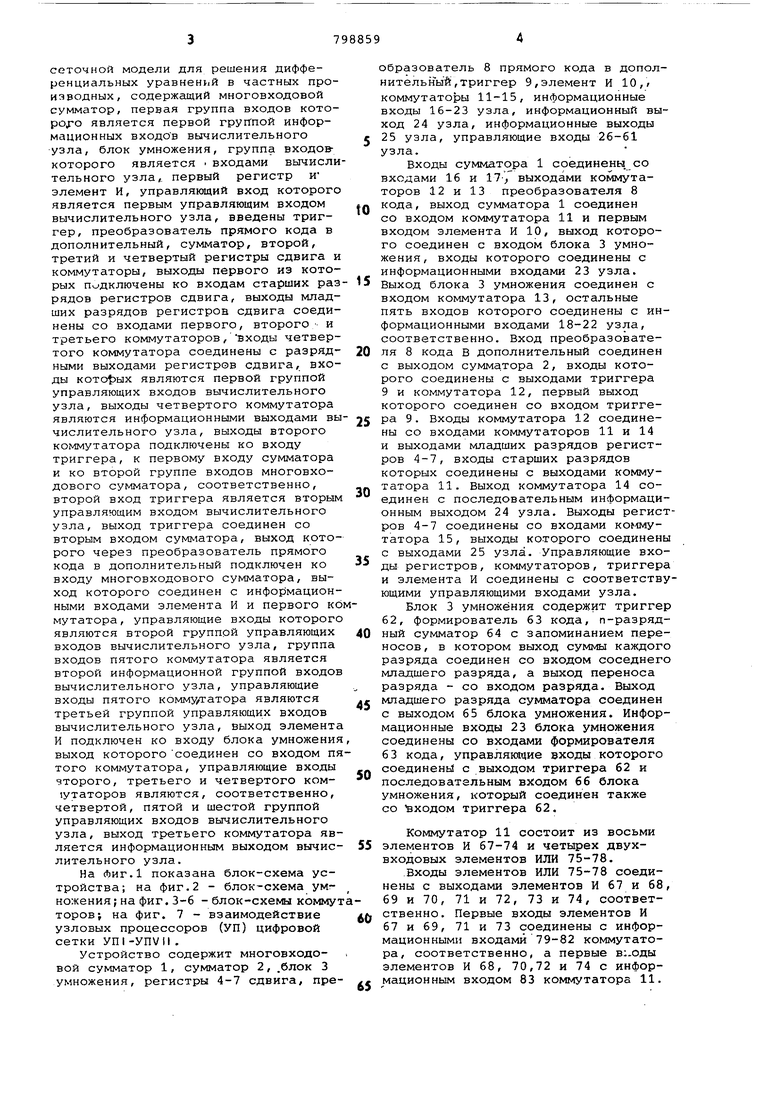

Блок 3 умножения содержит триггер 62, формирователь 63 кода, п-разрядный сумматор 64 с запоминанием переносов , в котором выход суммы каждого разряда соединен со входом соседнего младшего разряда, а выход переноса разряда - со входом разряда. Выход младшего разряда сумматора соединен с выходом 65 блока умножения. Информационные входы 23 блока умножения соединены со входами формирователя 6 3 кода, управляклцие входы которого соединень с выходом триггера 62 и последовательным входом 66 блока умножения, который соединен также со входом триггера 62.

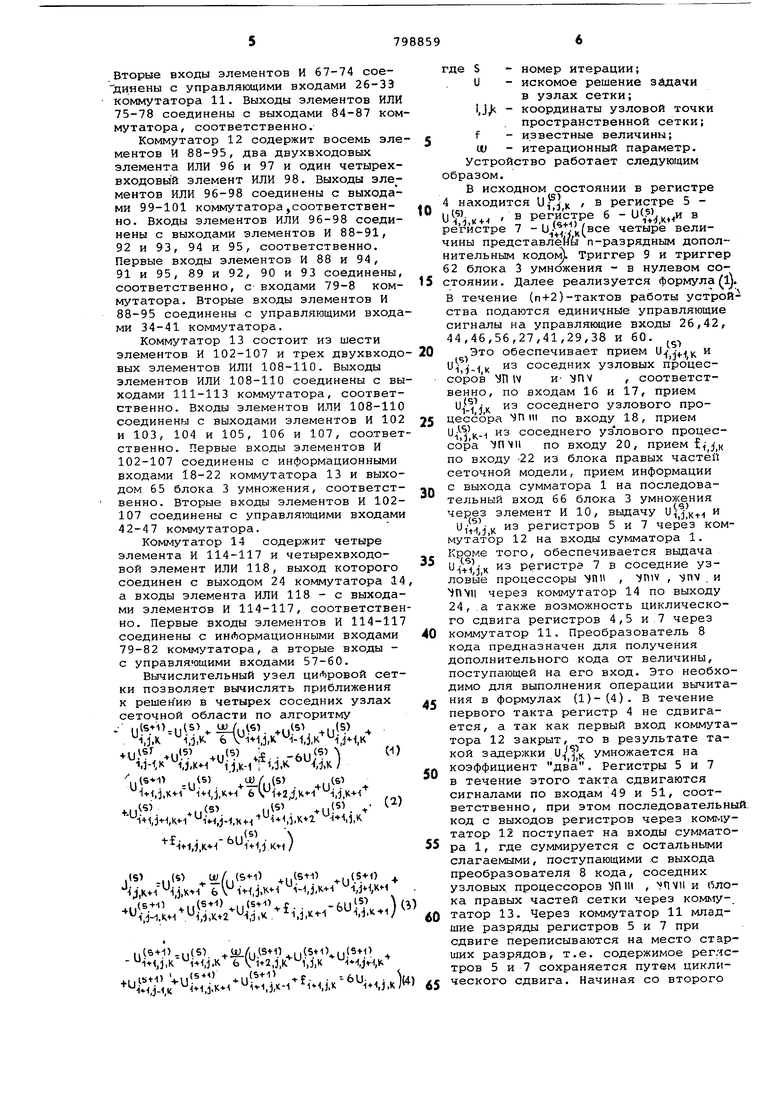

Коммутатор 11 состоит из восьми элементов И 67-74 и четырех двухвходовых элементов ИЛИ 75-78.

Входы элементов ИЛИ 75-78 соединены с выходами элементов И 67 и 68, 69 и 70, 71 и 72, 73 и 74, соответственно. Первые входы элементов И 67 и 69, 71 и 73 соединены с информационными входами 79-82 коммутатора, соответственно, а первые в:.оды элементов И 68, 70,72 и 74 с информационным входом 83 коммутатора 11. Вторые входы элементов И 67-74 сое динены с управляющими входами 26-33 коммутатора 11. Выходы элементов ИЛИ 75-78 соединены с выходами 84-87 ком мутатора, соответственно. Коммутатор 12 содержит восемь эле ментов И 88-95, два двухвходовых элемента ИЛИ 96 и 97 и один четырехвходовый элемент ИЛИ 98. Выходы элементов ИЛИ 96-98 соединены с выходами 99-101 коммутатора соответственно. Входы элементов ИЛИ 96-98 соединены с выходами элементов И 88-91, 92 и 93, 94 и 95, соответственно. Первые входы элементов И 88 и 94, 91 и 95, 89 и 92, 90 и 93 соединены, соответственно, с входами 79-8 коммутатора. Вторые входы элементов И 88-95 соединены с управляющими входа ми 34-41 коммутатора. Коммутатор 13 состоит из шести элементов И 102-107 и трех двухвходо вых элементов ИЛИ 108-110. Выходы элементов ИЛИ 108-110 соединены с вы ходами 111-113 коммутатора, соответственно. Входы элементов ИЛИ 108-110 соединены с выходами элементов И 102 и 103, 104 и 105, 106 и 107, соответ ственно. Первые входы элементов И 102-107 соединены с информационными входами 18-22 коммутатора 13 и выходом 65 блока 3 умножения, соответственно. Вторые входы элементов И 102107 соединены с управляющими входами 42-47 коммутатора. Коммутатор 14 содержит четыре элемента И 114-117 и четырехвходовой элемент ИЛИ 118, выход которого соединен с выходом 24 коммутатора 14 а входы элемента ИЛИ 118 - с выходами элементов И 114-117, соответствен но. Первые входы элементов И 114-117 соединены с инЛормационными входами 79-82 коммутатора, а вторые входы с управляощими входами 57-60. Вычислительный узел цигЪровой сетки позволяет вычислять приближения к решению в четырех соседних узлах сеточной области по алгоритму - i,(S+1).y(S) tlJJ Ле .151 .(5) 4i.K 1ЛЛ 1ЧЗЛ У ...4iu-6U .1-(,х i.j..и. - 4( , 1,J,K 6 V i-i-2,j, .iK-n + +1.5 ,Ккн 1Чз-1,нн i,i. 1-1Л IH.J-I.H+I , i .,,(0 /м( (sti) ( ,j, 6 i4j.i -1. iУ-,л.,UЙ:кV ;J:Г «.i,) ( .i....i где S - номер итерации; и - искомое решение зйдачи в уэлах сетки; ij - координаты узловой точки пространственной сетки; f - известные величины; Ш - итерационный параметр. Устройство работает следующим образом. В исходном состоянии в регистре I (5 4 находится U,- j , в регистре 5 ,K4 , Н егистре 7 четыре велиины представлен п-разрядным дополнительным кодом). Триггер 9 и триггер 62 блока 3 умножения - в нулевом состоянии. Далее реализуется формула (l. В течение (п+2)-тактов работы устройства подаются единичные управляющие сигналы на управлякяцие входы 26,42, 44,46,56,27,41,29,38 и 60. Это обеспечивает прием . и U.j.,-.,( из соседних узловых процессоров )П W и- УПУ , соответственно, по входам 16 и 17, прием u|.j из соседнего узлового процессора sn 111 по входу 18, прием соседнего узлового процессора nNll по входу 20, прием по входу -22 из блока правых частей сеточной модели, прием информации с выхода сумматора 1 на последовательный вход 66 блока 3 умножения через элемент И 10, выдачу из регистров 5 и 7 через комму татор 12 на входы сумматора 1. Кроме того, обеспечивается выдача из регистра 7 в соседние узловые процессоры пч , , -jnv . и ПЧП через коммутатор 14 по выходу 24, а также возможность циклического сдвига регистров 4,5 и 7 через коммутатор 11. Преобразователь 8 кода предназначен для получения дополнительного кода от величины, поступающей на его вход. Это необходимо для выполнения операции вычитания в формулах (1)-(4). В течение первого такта регистр 4 не сдвигается, а так как первый вход коммутатора 12 закрыт, то в результате такой задержки U умножается на коэффициент два. Регистры 5 и 7 в течение этого такта сдвигаются сигналами по входам 49 и 51, соответственно, при этом последовательный, код с выходов регистров через коммутатор 12 поступает на входы сумматора 1, где суммируется с остальньтми слагаемыми, поступающими .с выхода преобразователя 8 кода, соседних узловых процессоров УШИ , vrivil и блока правых частей сетки через комму-, татор 13. Через коммутатор 11 младшие разряды регистров 5 и 7 при сдвиге переписываются на место старших разрядов, т.е. содержимое регистров 5 и 7 сохраняется путем циклического сдвига. Начиная со второго .такта работы устройства, подается единичный сигнал на управляющий вход 34, чем обеспечивается передача кода с выхода младшего разряда регистра 4 на вход триггера 9 и сумматора 2 через коммутатор 12. Триггер 9 двухтактный,, так как необходимо одновременно осуществлять прием-информации с выхода коммутатора 12 и выдачу информации на вход сумматора 2, На триггере 9 запоминается значение младшего разряда регистра 4 и этот разряд суммируется на сумматоре 2 с предБщушим разрядом, запомненным на триггере 9 в предыдущем такте. Таким образом, вследствие задержки в первом такте на коммутаторе 12 зна чение U|,,K умножается на коэффициент , а вследствие задержки на двухтактном триггере 9 получается фактически значение U , умноженное на коэффициент- четыре -. Складывая эти два значения на сумматоре 2 получался умножение величины, посту пающей на вход триггера 9, на коэффи циент шесть. Результат суммирования с выхода сумматора 3 поступает на вход преобразователя 8 кода, а с выхода преобразователя 8 кода - на вход сумматора 1, где суммируется с остальными слагаемыми. Начиная со второго такта, подаются сигналысдвига на управ ляющий вход 48. В результате, через коммутатор 11 выполняется циклический сдвиг регистра- 4. Очередной разряд суммы с выхода сумматора 1 через элемент И 10 поступает на вход 66 блока 3 умножения На входы 23 блока 3 умножения параллельным кодом подается величина и с входов 23 (у/6 поступает на входы формирователя 63 кода. На упр ляющие входы формирователя 63 кода поступает очередной разряд суммы со входа 66 и предыдущий разряд суммы с выхода триггера 62. В зависимости от значений этой пару разрядов формирователь 63 кода вкщает на входы сумматора 64 значение , дополнител ный код от (jy/6 или нулевой код. Код с выхода формирователя 63 суммируется с содержи1 аам сумматора 64. На сумматоре 64 образуется очеред ное частичное произведение, младший разряд которого поступает на вход 66 блока 3 умножения. На п-ом и {п+1)-м тактах работы устройства сигналы сдвига со входов 49 и 51 на регистры 5 и 7, соответственно, не подаются. Этим обеспечи вается на (п+1) и {п+2)-ом тактах необходимое в дополнительном коде сложение знаковых разрядов старшими разрядами U и других соответствующих неизвестных в соседних узловых процессорах. На (п+2)-ом такте работы устрой,ства сигналы сдвига со входов 49 и 51 подаются на регистры 5 и 7, соответственно. В результате такой организации работы устройства, через (п+2)-тактов содержимое регистров 5 и 7 восстанавливается. Далее триггер 9 управляющим сигналом со входа 61 и триггер 62 блока умножения сбрасываются в нуль и в течение п-тактов работы устройства осуществляется суммирование с величиной Для этого подаются единичные уТаравляющие сигналы на входы 40,30 и 47. Остальные управляющие сигналы .нулевые. На регистр 4 подаются сигналы сдвига со входа 48. В результате последовательный код с выхода регистра 4 через коммутатор 12 суммируется со старшими разрядами произведения, поступающими с выхода 65 блока 3 умножения через коммутатор 13 на вход сумматора 1. Результат с выхода сумматора через коммутатор 11 записывается в регистр 4. Таким образом, через (2п+2)-тактов работы устройства в регистре 4 хранится вычисленное новое приближение ..(6+1) i,i.« .Цальнейшие вычисления .V--t аналогично вычислению . В течение (п-ь2)-тактов работы устройства подаются единичные сигналы на управляющие входы 27-29, 43,45,46,41,39, 56 и 58. Это обеспечивает прием -Ifi о к+ соседнего узлового процессораvn и по входу- 19, U.,,j .3 узлового процессора ;jnvi по входу 21, входу 22 из блока правых частей сеточной модели, прием ( соседних узловых процессорбв iniv и StlV , соответственно, по входам 16 и 17, выдачу и|, U.j.j из регистров 5 и 7 через коммутатор 12 на входы сумматора 1 и прием информации с выхода сумматора 1 на последовательный вход блока 3 умножения через элемент И 10.Крометого, обеспечивается выдача ..)Из регистра 5 в соседние узловыепроцессоры П1И , , WV и vnv через .коммутатор 14 по-выходу 24, а также возможность циклического сдвига регистров 5,6 и 7. В течение первого такта не сдвигается регистр 6, а регистры 5 и 7 сдвигаются. Со второго такта работы подается единичный сигнал на управляющий вход 35 коммутатора 12, в результате чего, код с выхода младшего разряда регистра 6 поступает на вход схемы умножения на коэффициент шесть. Работа этой схемы, состоящей из триггера 9 и сумматора 2, аналогична описанному. Одновременно циклически сдвигается регистр 6. Работа блока умножения аналогична описанному. На п-ом и (п+1)-ом тактах работы устройства с.игнал сдвига на регистры 5 и 7 не

подается и этим обеспечивается сложение знаковых разрядов, необходимое при сложении величин в дополнительном коде. За (п+2)-тактов содержимое регистров 5,6 и 7 восстановливается. Далее после сброса триггеров 9 и 62 в течение п-тактов работы устройства осуществляется суммирование . с величиной ,7,

.,-,K44;« 4i:.,si,,.,,

.,к-ЧЙк),

Для этого подаются единичные управляющие сигналы на входы 38,28 и 47. На регистр 6 подаются сдвигающие : импульсы со входа 50. Через п-тактов работы в регистре б получается новое приближение (. .

Вычисление u. по формуле (3) аналогично вычислению . В течение (пч-2)-тактов работы устройства подаются единичные сигналы на управляющие входы 26,28,27,42,45,46,4.0, 38, 59. Это обеспечивает прием соседнего узлового процесcopavnVi по входу 18 узлового процессора nvi по входу 21 ,, по входу 22 из блока правых частей сеточной модели,прием ,VK соседних узловых процессоров jnw и , соответственно, по входам 16 и 17, выдачу иД, U , из регистров 4 и 6 через- коммутатор 12 на входы сумматора 1 и прием информации с выхода сумматора 1 на последовательный вход блока 3 умножения через элемент И 10. Кроме того, обеспечивается выдача (H3 регистра 6 в соседние узловыеПроцессоры ЗПН, Vnvi , П( и jnM через коммутаторы 14 по выходу 24,а также возможность циклического сдвига регистров 4,5 и 6. В течение первого такта не сдвигается регистр 5, а регистры 4 и 6 сдвигаются. Со второго такта работы устройства подается единичный сигнал на управляющий вход 37 коммутатора 12, в результате чего, код с выходов младших разрядов регистра 5 поступает на вход схемы умножения на коэффициент шесть. (Работа этой схемы аналогична описанному).Одновременно циклически сдвигается регистр 5. (Работа блока умножения аналогична описанному). На п-ом и (п +1)-ом тактах работы устройства сигнал сдвига на регистры 4 и 6 не подается и этим обеспечивается сложение знаковых разрядов, необходимое при сложении ;в дополнительном коде. За (п+2)-тактов содержимое регистров 4,5 и 6 восстановливается. Далее после сбросов триггеров 9 и 62, в течение п-тактов работы устрой ства осуществ

ляется суммирование веЛИчиной

(,j(S .i.(5 +i,(Sl Р1 + 2.1, + 1,ЗЧКИ

- SniH lj,. / .iXMJ.

Для этого подаются единичные управляющие сигналы на входы 41,31 и 47. На регистр 5 подаются сдвигающие импульсы со входа 49. Через п-тактов работы в регистре 5 получается новое приближение .Вычисление .j.a.nasloгичlto вь1числению . в течение (п+2)-тактов работы устройства подаются единичные сигналы на управляющие входы 26,28,29/ 43,45,46,40,38,56 и 57. Это обеспечивает прием соседнего узлоTT -jJiH.

вого процессора упч по входу 1-9, iMjuM соседнего узлового процессорачпми по входу 20,, входу 22 из блока правых частей сеточной модели, прием соседних узловых процессоров N)fnv- и и , соответственно, по входам 16 и 17, выдачу и и||,-д,,из регистров 4 и 6 черезкоммутатор 12 на входы сумматора 1 и прием информации с выхода

сумматора 1 на последовательный вход блока 3 умноженияЧерез элемент И 10. Кроме того, обеспечивается выдача иД из регистра 4 в соседние узловые процессоры пт ,vnw , vnv и ПУЧчерез коммутатор 14 по выходу 24, а также возмЪжность циклического сдвига регистров 4,6 и 7. В течение первого такта регистр 7 не сдвигается, а регистры 4 и 6 сдвигаются.Начиная

со второго такта, подаются единичные сигналы на управляющий вход 36 коммутатора 12, в результате чего, код с выхода младших разрядов регистра 7 поступает на вход схемы умножения на коэффициент шесть . (Работа этой

схемы и работа блока .умножения аналогична описанному). Начиная со второго такта, циклически сдвигается регистр 7. На (п+1)-ом тактах :работы устройства сигнал сдвига

на регистры 4 и 6 не подается. Этим осуществляется сложение знаковых разрядов, необходимое при сложении в дополнительном коде. За (п+2)-тактов содержимое регистров 4,6 и 7 восста.новливается. Далее после сбросов i триггеров 9 и 62, в течение п-тактов работы устройства осуществляется суммирование ,j,K--c величиной -.

MlfiiCs-ni «.иСв-и 1, . ч. Ь V ini-K i i-i,,J-,4«-i 1,,кt:

А( .3,к ti,.j,,j,KM).

Для этого подаются единичные управля.ющие сигналы на входы 39,33 и 47, На регистр 7 подаются сдвигающие импульсы со входа 51. п-тактов работы в регистре 7 .получается новое приближение ..K

Подавая управляющие сигналы со входов 52-55 на входы коммутатора 15, можно осуществить считывание содержимого регистров 4 и 5, 6 и 7, соответственно, по выходам 25. Блоксхема одного разряда коммутатора 15 аналогична структуре коммутатора 14.

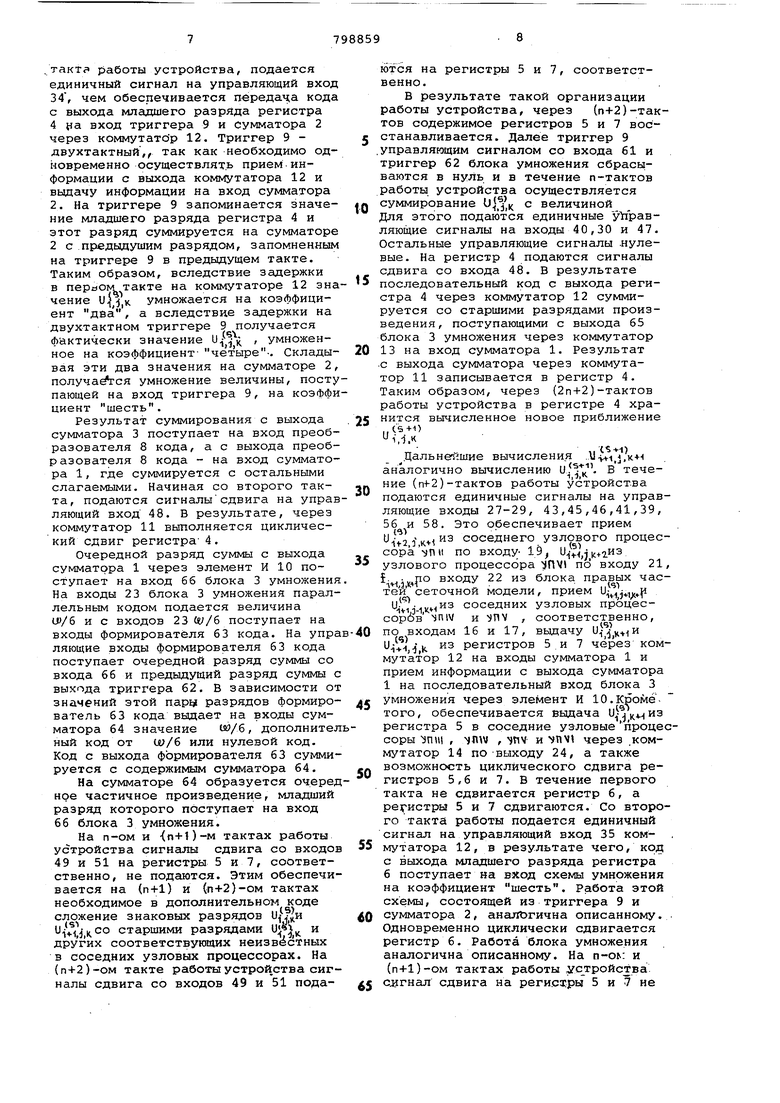

На фиг.7 иллюстрируется взаимодействие узловых процессоров сеточной модели и показан порядок вычисления приближений в узловых точках цифровой сетки. Квадратами показаны соседние узловые процессоры inl-an.Vll , причемУП - центральный npoiieccop, являющийся соседним для всех остальных шести процессоров .одновременно. Кружочками показаны узловые точки пространственной сетки/Номер внутри указывает на порядок вычисления приближения в данной узловой точке, т.е. вVtili - MTlNiiодновременно вычисля-. ются приближения в точках с номером 1, затем - в точках с номером 2 и т.д. В верхнем левом углу (фиг.7) показаны координатные оси данной сеточной области.

Предлагаемый вычислительный узел позволяет вычислять и хранить приближения в четырех узловых точках пространственной сетки. По сравнению с четырьмя известными узлами он содержит одинаковое число регистров (четыре) , один многовходовой сумматор и один блок умножения, против четырех сумматоров и блоков умножения в известном. В предлагаемом узле введено дополинтельно в состав коммутаторов 11-14 тридцать семь элементов И и ИЛИ, двухтактный триггер 9, одноразрядный сумматор 2. Этот объем оборудования эквивалентен примерно восьми тактируемым триггерам типа 3-К.Преобразователь 8 кода по сложности равен примерно трем триггерам. Коммутатор 15 содержит/5 п элементов ИЛИ, что при наиболее широко применяемой разрядности п 32 соответствует двадцати триггерам. Следовательно, введенное в вычислительный узел перечисленное оборудование, эквивалентно тридцати одному триггеру. Блок 3 .множения по разрядности 32 содержит 64 триггера для хранения суммы и переносов. Многовходовой сумматор 1 для хранения переносов должен содержать семь триггеров. В целом объем оборудования в четырех известных узлах составляет при разрядности 32 412 триггеров. Объем оборудования в предлагаемом узле составляет около 230 триггеров (128 триггеров в регистрах, 65 триггеров в блоке умножения, 7 триггеров в многовходовом cyNwaTope, 31 условный триггер в коммутаторах, преобразователе кода, триггере и двухвходовом сумматоре).

Следовательно объем оборудования в предлагаемом узле на 45% меньше, чем в известном.

Полное время решения задачи на известном и предлагаемом узле равно

t.

),,,

где т} - число итераций на извест0

- число итераций на предлагаемом узле.

Вычислительный известный узел реализует метод простой итерации. Для него

2N „ 1

С5)

А).

.

Предлагаемый вычислительный узел ориентирован на метод релаксации, для которого

(ь)

в формулах (5) и (6) N - количество узлов сетки по одной координатной оси, Б - требуемая точность решения задачи.

Следовательно

ij 2y(2N/fr)tn1|e 8nN ON N t2-(8h 8XNliir-)e.n-i((8M+8)4tiH)

Время решения задач на предлагаемом устройстве примерно в N /3 раз

меньше, чем на известном. Для современных задач в частных производных характерны значения N 10-10 .Следовательно, предлагаемый вычислительный узел обеспечивает увеличение

скорости решения задач в 3-30 раз.

Формула изобретения

Вычислительный узел цифровой сеточной модели для решения дифферен циальных уравнений в частных производных, содержащий многовходовой сумматор, первая группа входов которого явлйется первой группой информационных входов вычислительного узла, блок умножения, группа входов KOi.oporo является входами вычислительного узла, первый регистр и элемент И, управляющий вход которого

5 является первым управляющим входом вычислительного узла, отличающийся тем, что, с целью повышения быстродейтсвия, в него введены триггер, преобразователь прямого коQ да в дополнительный, сумматор, второй, третий и четвертый регистры сдвига и коммутаторы, выходы первого из которых подключены ко входам старших разрядов регистров сдвига,

выходы младших разрядов регистров

сдвига соединены со входами первого, второго и третьего коммутаторов, входы четвертого коммутатора соединены с разрядными выходами регистров сдвига, входы которых являются первой группой управляющих входов вычислительного узла, выхода четвертого коммутатора являются информационными выходами вычислительного узла, выходы второго коммутатора подключены ко входу триггера, к первому входу сумматора и ко второй группе входов многовходового сумматора, соответственно, второй вход триггера является вторым управляющим входом вычислительного узла, выход триггера соединен со вторым сумматора, выход которого через преобразователь прямого кода в дополнительный подключен ко входу многовходового сумматора, выход которого соединен с информационными входами элемента И и первого коммутатора, управляющие входы которого являются второй группой управляющих входов вычислительного узла, группа входов

пятого коммутатора является второй информационной группой входов вычислительного узла, управляющие входы пятого коммутатора являются третьей группой управляющих входов внчисли тельного узла., выход элемента И подключен ко входу блока умножения, выход которого соединен со входом пятого коммутатора, управляющие входы второго, третьего и четвертого коммутаторов являются, соответственно, 0 четвертой, пятой и шестой группой ,управляющих входов вычислительного узла, выход третьего коммутатора является информационным выходом вычислительного узла. 5

Источники информации, принятые во внимание при экспертизе

1.Евреинов Э.В., Косарев Ю.Г. Однородные вычислительные системы высокой производительности. Новосибирск, Наука, 1966, с.38-41, рис.8.

2.Авторское свидетельство СССР

№ 608165, кл.с 06 F 15/32, 1975 (прототип) .

Cvj

e « illl

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Вычислительный узел цифровойСЕТКи | 1979 |

|

SU800997A1 |

| Сеточный микропроцессор | 1978 |

|

SU763904A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Вычислительный узел цифровой моделисетки для решения дифференциальных уравнений в частных производных | 1975 |

|

SU608165A1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ТРЕХМЕРНЫХ ЗАДАЧ МАТЕМАТИЧЕСКОЙ ФИЗИКИ | 1991 |

|

RU2051411C1 |

Г

,-

«

t.

liL

{

I

55

, JJ5,

HI

FT

7

t

J7.38, 59.

IrilrS L

да I р/ 1 2 Й5

ее 89

jkJL

ж

т

Ю1

в19202iгг65

rlfi rXfX Гг1тХ

UTim иГш U ДЭ4- U Л2У U /Д5 - /07

т

///

SB

W.4/.

41г г

5 4 95

f f . I

96

Т

т

ЮО

т

80SIК

S9 so

I J I L I Jc.

U ifS U //5 U //7

V/

&

i) () L-1,j, i-2j,f(4 ./И

(V)(:

(

4/V-/ ЧЛ -/

HJ-f,f

,к

mw

УПШ

(У

,f

i

упт

()

H/,fs-z 0 C) 4/ ч 4/ ,/

Авторы

Даты

1981-01-23—Публикация

1979-02-23—Подача