Изобретение относится к вьтисли- тельной технике, в частности к сетям связи ЭВМ, использующим модемы,

Цель изобретения - повышение коэффициента готовности коммутатора за счет блокировки запрещенных комбинаций соединений.

На фиг.1 изображена функциональная схема коммутатора каналов; на фиг.2 -4 - примеры реализации первого и второго шифраторов и блока памяти соединений соответственно; на фиг.5 - граф-схема состояний коммутатора; на .фиг. 6 - временные диаграммы ра- боты,блока формирования ошибки; на фиг. 7 - пример мнемосхемы возможных соединений в коммутаторе.

Коммутатор каналов содержит (фиг, блоки 1 коммутации блок 2 памяти соединений, блок 3 управления коммутацией, блок 4 формирования ошибки,, Блок 3 содержит одновибратор 5, ключ 6, первьм 7 и второй 8 шифраторы,, элемент 9 задержки, элемент И 10, ре версивный счетчик 11, дешифратор }., элемент ИЛИ 13, элемент НЕ 14 Блок, 4 содержит элементы ИЛИ 15 и 16,, элемент 17 задержки, триггер 18, элемент И 19, первый 20 и второй 21 од- новибраторы.

.Настроечная информация (команды коммутации) поступает на вход 22 коммутатора 3 сопровождении стробирующе го импульса по входу 23. Дешифратор 12 формирует на своих выходах потенциальные сигналы, которые по шинам 24 - 26 поступают на соответствующие входы ключа 6 и шифраторов 7 и 8. На выходах 27 и 28 коммутатора форми руются код состояния и признак ошибки соответственно, которые могут пос т упать на блок отображения мнемосхемы устанавливаемых соединений и на ЭВМ. Выходы первого шифратора 7 и ключа 6 подключены соответственно череэ шины 29 и 30 к четвертому и третьему информационным входам второго шифратора Bj, выход которого через шину 31 подключен к информацион.ном у входу блока 2 памяти соединений,

Первый шифратор 7 (фиг„2) может быть выполнен на группах.элементов И 32 и элементов ИЛИ 33.

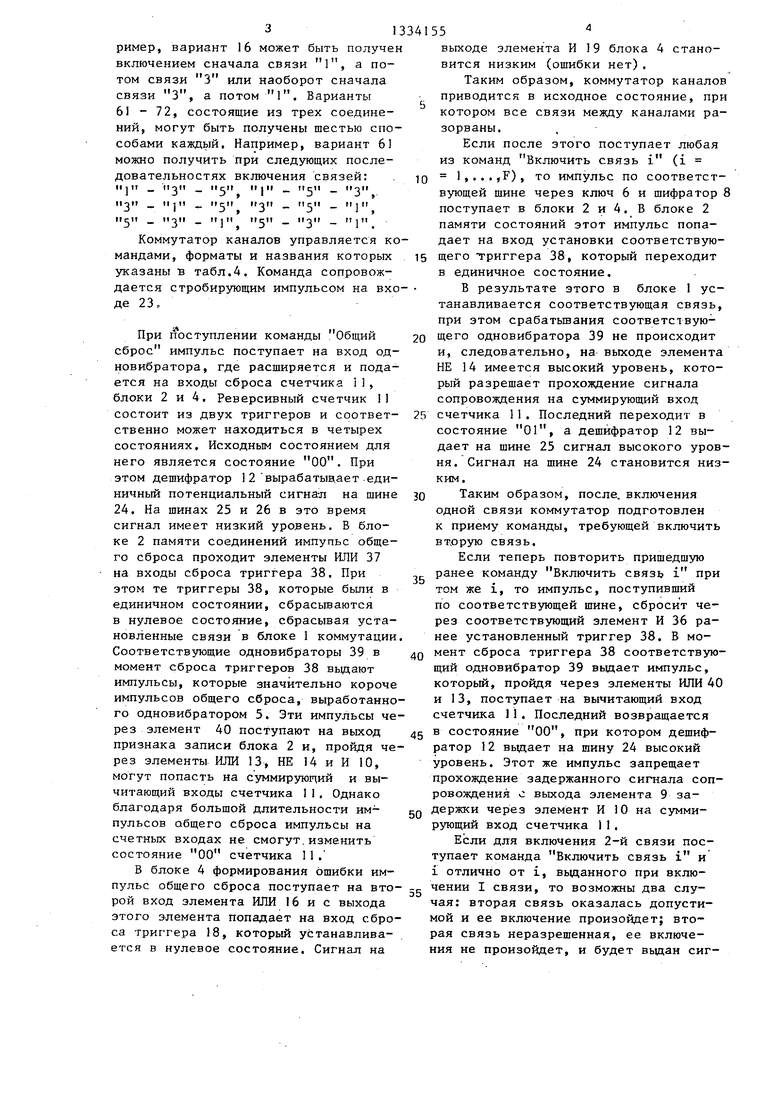

Второй шифратор 8 (фиг.З) может быть выполнен на группах элементов ИЛИ 34 и элементов И 3.5.

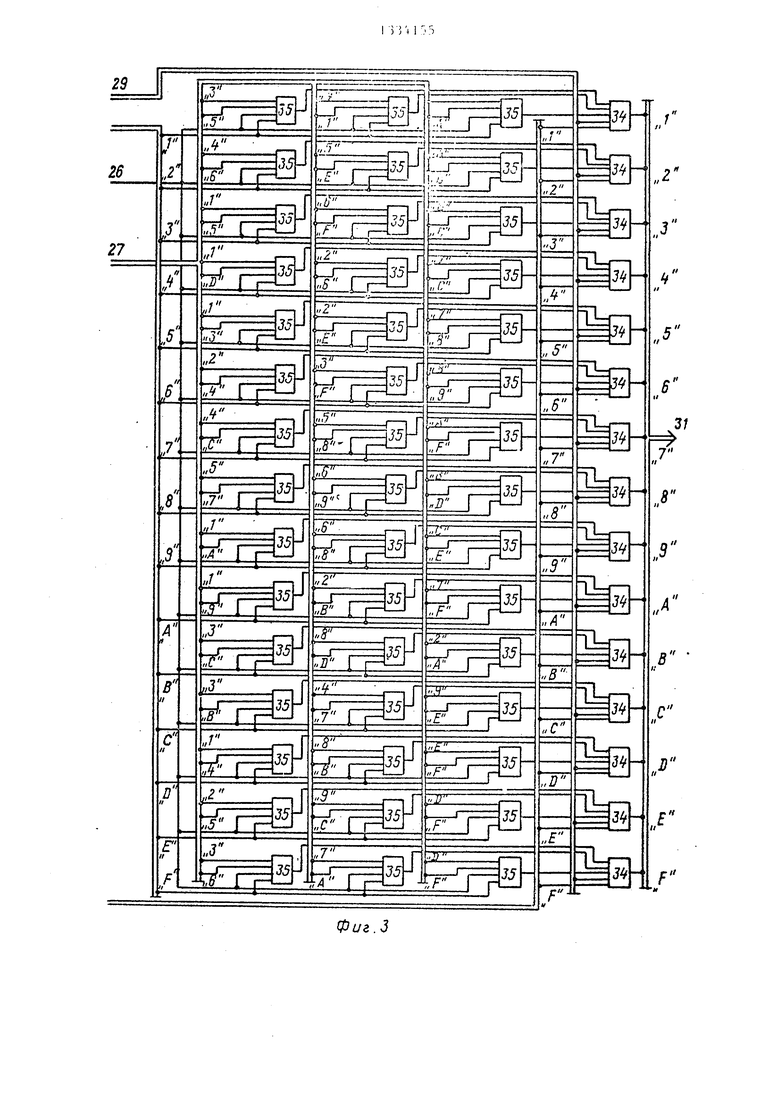

Блок 2 памяти соединений (фиг.4) содержит группу ячеек памят и (кой И

д 5 ,-

;

чество ячеек соответствует числу связей, устанавливаемых блоком 1 коммутации) , причем каждая ячейка памяти состоит из элемента И 36, элемента Ш1И 37, триггера 38 и одновибратора 39. Сигналы с выходов одновибраторов объединяются на элементе ИЛИ 40, на выходе которого формируется признак записи информации блока 2.

Работу коммутатора рассмотрим на примере шести коммутируемых каналов МО - М5 и пятнадцати возможных связей между ними 1,;.., 9,А,,.., F (используется запись чисел в шестнадцатиричной системе счисления), которые обозначены на фиг.7.

Коммутатор каналов обеспечивает следующие возможности: включение любой из 15-ти связей 1, ,.,

А, В, ...., Е, F между двумя из шести коммутируемых каналов;включение разрешенной второй связи в со.- ответствии с табл.; включение третьей разрешенной связи в зависимости от двух уже включенных в соответствии с табл.2; выключение по од- „ной любой из включенных связей; од повременное выключение всех связей.

Коммутатор каналов предназначен ,. для осуш.ествления связей типа точка с точкой шестью коммутируемыми .каналами, к которым присоединены выходы модемов в линию связи с коммутируемой сетью.

Разрешены только попарные соединения коммутируемых каналов, -которые могут состоять из одной, двух или трех пар соединеннь;(х каналов, Присое-- динение к работающей паре соединен- ных каналов третьего приводит к отказу аппаратуры связи и поэтому недопустимо. При помощи имеющихся в коммутаторе каналов 15-ти связей можно было бы создать - 1 32767 вари- анто-в соединений, однако по указан- HKJ-J причинам разрешены только 75 вариантов связей, перечисленньк в табл,3.

Таким образомf коммутатор исключает возможность 32767-75 32692 вари- а;.;гов недопустимых соединений, приводящих к отказу аппаратуры. Связи, образ ующие некоторьй вариант соединения, включаются последовательно.Поэтому, варианты 16-60, состоящие из двух попарньпс соединений, могут быть получены двумя способами каждый.Нап31

ример, вариант 16 может быть получен включением сначала связи 1, а потом связи 3 или наоборот сначала связи 3, а потом 1. Варианты 61 - 72, состоящие из трех соединений, могут быть получены шестью способами каждый. Например, вариант 61 можно получить при следующих последовательностях включения связей: .

II 1 It ItollMr HIMttcllllQll

IJ - .), I- ) - J, 3 II „ c 3 - 5

с oil 111 clt lloll Itill

Коммутатор каналов управляется командами, форматы и названия которых указаны в табл.4. Команда сопровождается стробирующим импульсом на вхо де 23,

При 1 оступлении команды Общий сброс импульс поступает на вход од- новибратора, где расширяется и подается на входы сброса счетчика i1, блоки 2 и 4. Реверсивный счетчик II состоит из двух триггеров и соответ- ственно может находиться в четырех состояниях. Исходным состоянием для него является состояние 00. При этом дешифратор 12 вырабатывает.единичный потенциальный сигнал на шине 24. На шинах 25 и 26 в это время сигнал имеет низкий уровень. В блоке 2 памяти соединений импульс общего сброса проходит элементы ИЛИ 37 на входы сброса триггера 38. При этом те триггеры 38, которые были в единичном состоянии, сбрасываются в нулевое состояние, сбрасывая установленные связи в блоке 1 коммутации Соответствующие одновибраторы 39 в момент сброса триггеров 38 вьщают импульсы, которые значительно короче импульсов общего сброса, выработанного одновибратором 5. Эти импульсы через элемент 40 поступают на выход признака записи блока 2 и, пройдя через элементы ИЛИ 13, НЕ 14 и И 10, могут попасть на суммируюпий и вычитающий входы счетчика I1. Однако

благодаря большой длительности им

пульсов общего сброса импульсы на счетных входах не смогут.изменить состояние 00 счетчика 11 .

В блоке 4 формирования ошибки импульс общего сброса поступает на вто- рой вход элемента ИЛИ 16 и с выхода этого элемента попадает на вход сброса триггера 18, который устанавливается в нулевое состояние. Сигнал на

ю

is

20 25 зо ,g 0 5

0

д

55

выходе элемента И 19 блока 4 становится низким (ошибки нет).

Таким образом, коммутатор каналов приводится в исходное состояние, при котором все связи между каналами разорваны.

Если после этого поступает любая из команд Включить связь i (i i,...,F), то импульс по соответствующей шине через ключ 6 и шифратор 8 поступает в блоки 2 и 4. В блоке 2 памяти состояний этот импульс попадает на вход установки соответствующего триггера 38, который переходит в единичное состояние.

В результате этого в блоке 1 устанавливается соответствующая связь, при этом срабатьшания соответс1вую- щего одновибратора 39 не происходит и, следовательно, на выходе элемента НЕ 14 имеется высокий уровень, который разрешает прохождение сигнала сопровождения на суммирующий вход счетчика 11. Последний переходит в состояние 01, а дешифратор 12 выдает на шине 25 сигнал высокого уровня. Сигнал на шине 24 становится низким.

Таким образом, после, включения одной связи коммутатор подготовлен к приему команды, требующей включить вт.орую связь.

Если теперь повторить пришедшую ранее команду Включить связь i при том же i, то импульс, поступивший по соответствующей шине, сбросит через соответствующий элемент И 36 ранее установленный триггер 38. В момент сброса триггера 38 соответствующий одновибратор 39 выдает импульс, который, пройдя через элементы ИЛИ 40 и 13, поступает на вычитающий вход счетчика 11. Последний возвращается в состояние 00, при котором дешифратор 12 выдает на шину 24 высокий уровень. Этот же импульс запрещает прохождение задержанного сигнала сопровождения с выхода элемента 9 задержки через элемент И 10 на суммирующий вход счетчика 11.

Если для включения 2-й связи поступает команда Включить связь i и i отлично от i, вьщанного при включении I связи, то возможны два случая: вторая связь оказалась допустимой и ее включение произойдет; вторая связь неразрешенная, ее включения не произойдет, и будет вьдан сиг

51

нал ошибки оператору. Допустимость включения второй связи зависит от того, какая включена I связь. Разрешенные 1Г связи в функции от включен™ ных I связей приведены в табл.1.

В первом случае команда проходит через первый шифратор 7 и через второй шифратор 8 устанавливает соответствующую вторую связь в блоке 2 памяти аналогично описанному. После этого импульс сопровождения с выхода элемента 9 задержки проходит через элемент И 10 на суммирующий Вход счетчика 11 и переводит его в состояние 10. При.этом дешифратор 12 выдает высокий уровень только на шину 26 и тем самым подготавливает коммутатор к включению третьей связи. В этом состоянии можно выключить любую из двух включенньк уже связей, для чего необходимо повторно подать команду включения этой связи. Работа логики коммутатора при отключении связи происходит так же, как описано при рассмотрении отключения первой связи. Далее, если для включения 3-й связи поступает команда Включить связь i и i отлично от i выданного, как при включении первой связи так при включении второй связи, то возможны также два случая: третья связь оказалась допустимой и ее включение произойдет; третья связь, за- данная командой, неразрешенная, ее включения не произойдет, и будет выдан сигнал ошибки.

Допустимость включения третьей связи зависит от того, какие включены I и П связи. Разрешенные П1 связи в функции от включенных I и 1Г связей приведены в табл.2.

Первый случай аналогичен рассмотренному. После установления третьей связи счетчик 11 переходит в состояние 1 и сигналы на шинах 24 - 26 дешифратора 12 становятся низкими, т.е. прохождение команд включения связей через блоки I, II и 1ГТ тактов невозможно. Однако если такая команда поступит, то она приведет к появлению сигнала ошибки и не будет выполнена .. ,

Если команда включения связи оказалась допустимой, то работа блока 4 формирования ошибки (фиг.ба) происходит так. Сигнал сопровождения с выхода элемента 9 задержки устанавливает триггер 8 в единичтсое соетоя

5

0

5

0

5

0

5

0

5

55fi

ние и запускает одновременно одновиб- ратор 20. Сигнал на выходе однонибра- тора 20 становится низким и поэтому сигнал высокого уровня на единичном выходе триггера 18 не может пройти через элемент И 19. Поскольку включение новой связи оказалось допустимым, то на выходе элемента ИЛИ 15 должен появиться импульс, который будет задержан в элементе 17 задержки на время, в течение которого произойдет установка в единичное состояние триггера 18. Спустя это время импульс с выхода элемента задержки 17 проходит через элемент ИЛИ 16 на вход сброса триггера 18 и сбрасьшает его. После этого отрицательный импульс на выходе одновибратора 20 заканчивается, но на единичном выходе триггера 18 -уже имеется низкий потенциал и сигналы Ошибка на выходах элемента И 19 и одновибратора 21 не появляются.

В отличие от этого (фиг.66), если команда включения новой связи оказалась недопустимой, то на выходе элемента ИЛИ 15 импульс не появляется. Триггер 18 не будет сброшен, и после окончания импульса на выходе одновибратора 20 высокий уровень с единичного выхода триггера 18 может пройти через элемент И 19 на выход 28, Это вызьшает срабатывание одно- вибратора 21, который выдает импульсный сигнал ошибки, который, пройдя через логический элемент ИЛИ 13 на вычитающий вход счетчика 11, .уменьшает его состояние на единицу, т.е. восстанавливает заполнение счетчика 11 .бьшшее до поступления ошибочной команды. Ошибочная команда не выполнилась, но коммутатор каналов готов к приему следующей команды.

Коммутатор каналов может находиться в четырех основных состояниях 00, 01, 10 и 11, соответствующих состояниям счетчика 5. Эти состояния и возможные переходы между ними показаны на графе (фиг,5)/ Состояние 00 устанавливается после включения коммутатора каналов,при общем сбросе и при сбросе на один. такт из состояния 01. В состояние 00 возможно включение любой одной

из 5-ти связей

tl I ч М oil

iTlt

J , . . , ,

9, А, Е, F. При

этом происходит переход Б состояние 01.

71

В состоянии 01 разрешено включение второй связи в зависимости от уже включенной первой связи. При включении допустимой связи коммута- тор переходит в состояние 10. При попытке включения недопустимой второй связи коммутатор выдает сигнал ошибки и остается в состоянии 01. При нажатии (повторном) клавиши кла- виатуры 1, соответствующей уже включенной связи, происходит сброс на один такт в состояние 00 и эта связь размыкается.

В состоянии 10 возможно включе- ние третьей связи в зависимости от двух ранее включенных св.язей. Если произведено включение допустимой связи, то коммутатор переходит в состояние 1 I . При попытке включения за- прещенной связи коммутатор остается в состоянии 10 и вьщается сигнал ошибки. При нажатии клавиши, соответствующей одной из уже включенных связей, происходит выключение этой свя- зи (сброс на один такт) и коммутатор переходит в состояние 01.

В состоянии 11 включены три связи. При попытке включить четвертую связь коммутатор не изменяет своего состояния и выдает сигнал ошибки.При нажатии любой из трех клавиш, соответствующих включенным связям, происходит сброс на один такт, связь.раз- рьшается, и коммутатор переходит в состояние 10.

Сигнал общего сброса переводит коммутатор из любого состояния (01 10 или 11) всостояние 00.

Сигнал ошибки не препятствует вы- полнению операции по установлению следующей связи. Если э та операция допустимая, то сигналы ошибки снимаются.

Предлагаемый коммутатор каналов автоматически контролирует допустимость выполнения поступившей команды включения некоторой связи. Команды, требующие включения недопустимых в момент принятия команды связей, не. вьпшлняются. Благодаря этому повьшга- ется надежность работы сети-связи, так как уменьшается вероятность потери ценной информации. Прием команды, которая не вьтолняется, не выводит коммутатор из рабочего состояния.

Оператор и ЭВМ уведомляются о том, что выданная команда отвергнута, пос

15 0 5

о

Q

5

5

0

5

1558

ле чего коммутатор готов к приему и анализу следующей команды.

Формула изобретения

1. Коммутатор каналов, содержащий блок коммутации, блок памяти соединений и бло к управления коммутацией, причем информационные входы-выходы блока коммутации являются одноименными входами-выходами коммутатора, вход настроечной информации и вход сопровождения которого соединены с входом настройки и входом тактирования блока управления коммутацией соответственно, выход которого подключен к информационному входу блока памяти соединений, выход которого подключен к управляющему входу блока коммутации, причем блок управления коммутацией содержит счетчик, дешифратор, ключ и элемент И, выход счетчика подключен к информационному входу дешифратора, первый выход которого подключен к управляющему пходу ключа, информационный вход которого соединен с .входом настройки блока управления коммутацией, о тличаю- щ и и с я тем, что, с целью повышения коэффициента готовности коммутатора за счет блокировки запрещенных комбинаций соединений, в него введен блок формирования ошибки, а в блок управления коммутацией введены одно- вибратор, элемент ИЛИ, элемент НЕ, элемент задержки, два шифратора, причем счетчик выполнен реверсивным, второй и третий выходы дешифратора подключены к входам стробирования первого и второго шифраторов соответственно, первые информационные входы которых подключены к входу настройки блока управления коммутацией, вторые информационные входы первого и второго шифраторов соединены с входом признака состояния блока управления коммутацией, вход разрешения перезаписи блока памяти соединений соединен с входом настроечной информации коммутатора, выходы ключа и первого информатора подключены к третьему и четвертому информационным входам второго шифратора соответственно, выход которого соединен с выходом блока управления коммутацией, вход тактирования которого соединен через элемент задержки с первым входом элемента И, выход которого подключен к суммирующему входу счетчика, вычитаюий ВХОД которого подключен к вьтходу элемента ИЛИ, первый и второй входы которого являются входами первого и второго логических условий блока управления коммутацией, второй вход элемента ИЛИ соединен через элемент НЕ с вторым входом элемента И, вы- ход элемента задержки является выходом синхронизации блока управления коммутацией, вход одновибрйтора соединен с входом разряда сброса входа настройки блока управления коммутацией, выход сброса которого соединен с выходом одновибратора и с входом сброса блока памяти соедине.ний,выход которого соединен с выходом признака состояния блока управления коммутацией, вход второго логического условия которого подключен к выходу признака записи информации блока памяти соединений, причем блок фор- . мирования ошибок содержит два элемента ИЛИ, элемент задержки, триггер, элемент И и два одновибратора, выход первого элемента ИЛИ подключен через элемент задержки к первому входу второго элемента ШШ, выход которого подключен к входу сброса триггера, вход установки которого соединен с входом первого одновибратора и с выходом синхронизации блока управления коммутацией, вход первого логического условия которого соединен с второго одновибратора, вход кото- 35 элементов И ячеек памяти груп- рого соединен с выходом эле мента И пы образуют вход разрешения переза- блока формирования ошибки, первый...и писи блока.

5

второй входы которого соединены с выходами триггера и первого одновибратора соответственно, входы первого элемента ИЛИ соединены с соответствующими разрядами выхода блок управления коммутацией, второй вход второго элемента ИЛИ соединен с выходом сброса блока управления коммутацией, выход элемента И блока формирования ошибки является выходом признака ошибки коммутатора, выход состояния которого соединен с выходом блока памяти соединений.

2, Коммутатор по п.1, о т л и - ч а ю щ и и с я тем, что блок памяти соединений содержит группу ячеек памяти и элемент ИЛИ, выход которого является выходом признака записи ин- Q формации блока, причем каждая ячейка памяти группы содержит элемент И, элемент ШШ, триггер и одновибратор, вход которого соединен с выходом триггера и с первым входом элемента И, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к входу сброса триггера, входы установки триггеров ячеек памяти группы образуют информационный вход группы, выходы одновибрато- ров подключены к соответствующим входам элемента ИЛИ, блока, вторые входы элементов ИЛИ ячеек памяти соединены с входом сброса блока, вторые

5

0

11

1334155

.12

Таблица 1

13

1334155

Таблиц

14

а 2

Таблица 3

171334155

Таблица А

фие,1

Фиг.З

,

2

3 V

г

,5 6

7 8

Л В

к

г , / f

п .

Включение

Вклю ение -и сдйзи

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации | 1987 |

|

SU1451674A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1327031A2 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для диагностики цифровых блоков | 1988 |

|

SU1674129A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для моделирования маршрутов сообщений и управления процессом коммутации в сети связи | 1980 |

|

SU922757A1 |

| Система передачи и приема информации | 1987 |

|

SU1411795A1 |

Изобретение относится к вычислительной технике и позволяет повысить надежность установления связей за счет блокировки запрещенных ком-. бинаций связей. Коммутатор каналов содержит блок коммутации, блок памяти соединений, блок управления коммутацией и блок формирования ошибки. Коммутатор автоматически контролирует допустимость выполнения поступившей команды включения некоторой связи. Команды, требующие включения недопустимых в момент принятия команды связей, не выполняются и не приводят к выводу коммутатора из рабочего состояния. Попытка ввода недопус- , тимой команды сопровояодается сигналом на вьпсоде признака ощибки коммутатора. 1 з.п. ф-лы, 7 ил., 4 табл. со со ел ел

Bx.Sm И

L

Вл.Кщ

Sivt.Srjf

Bbit.eiio

ffw-V

Л/jf. Chji

Врепя iput.S

BpfHfl

Редактор Е.Копча

Составитель А.Ушаков Техред и «Попович

Заказ 3964/46 Тираж 672 Подписное

ВНИИПИ Государственног о комитета. СССР

по делам изобретений т открытий 113035., Москва, Ж-35, Раушская наб.д д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Шекмар

| Коммутационное устройство для вычислительной системы | 1978 |

|

SU746492A1 |

| Коммутационное устройство | 1985 |

|

SU1251095A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-30—Публикация

1985-03-19—Подача