ньте возможности. Ко тутационное усл ройство содержит матричный коммутатор , матрицу 2 управления цией, блок 3 синхронизации и блок 4 памяти Информационные входы 5 и выходы 6 матричного коммутатора 1 являются соответствуюпдагми информационными входами и вьгходаки устрой- ства, к которым подключаются устУстройство относится к вычисли- , тельной технике и может быть использовано в многопроцессорных вычисли- тапьных, системах с программируемой коммутацией,

Целью изобретения является уве-- личение быстродействия устройства за счет устранения потерь времени при опросе незадействованных связей и расширение функциональнь х возмож- ностей путем обеспечения возможное-- тн централизованной настройки.

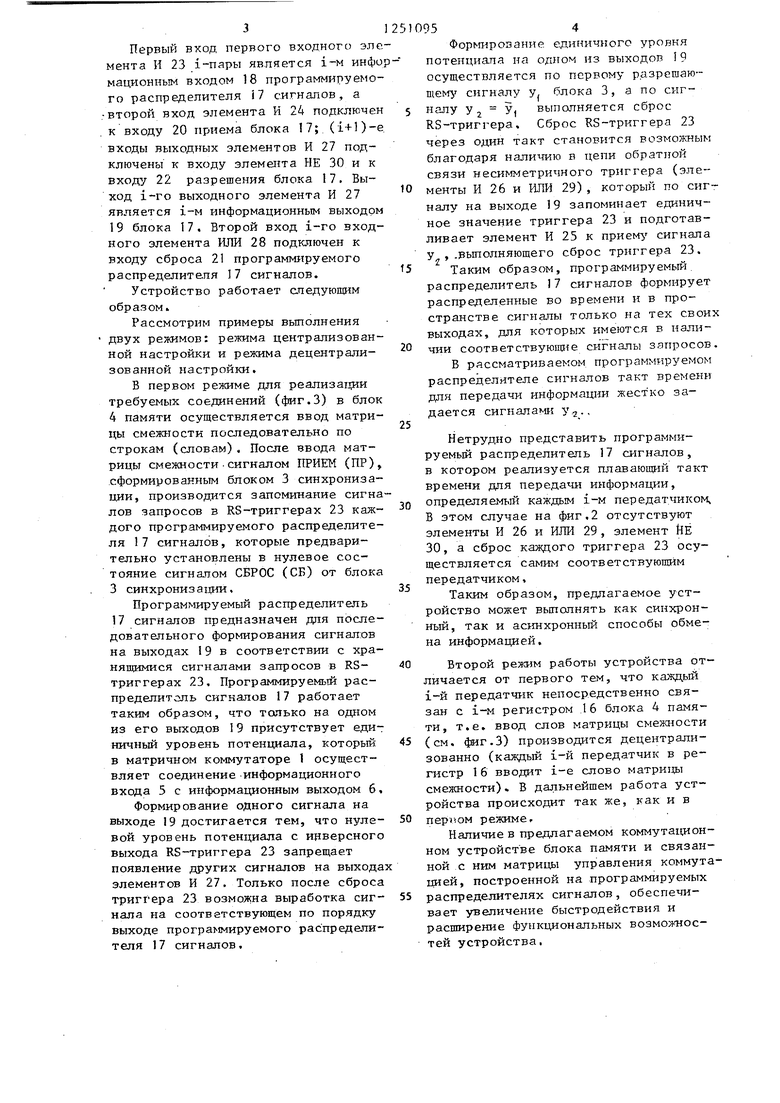

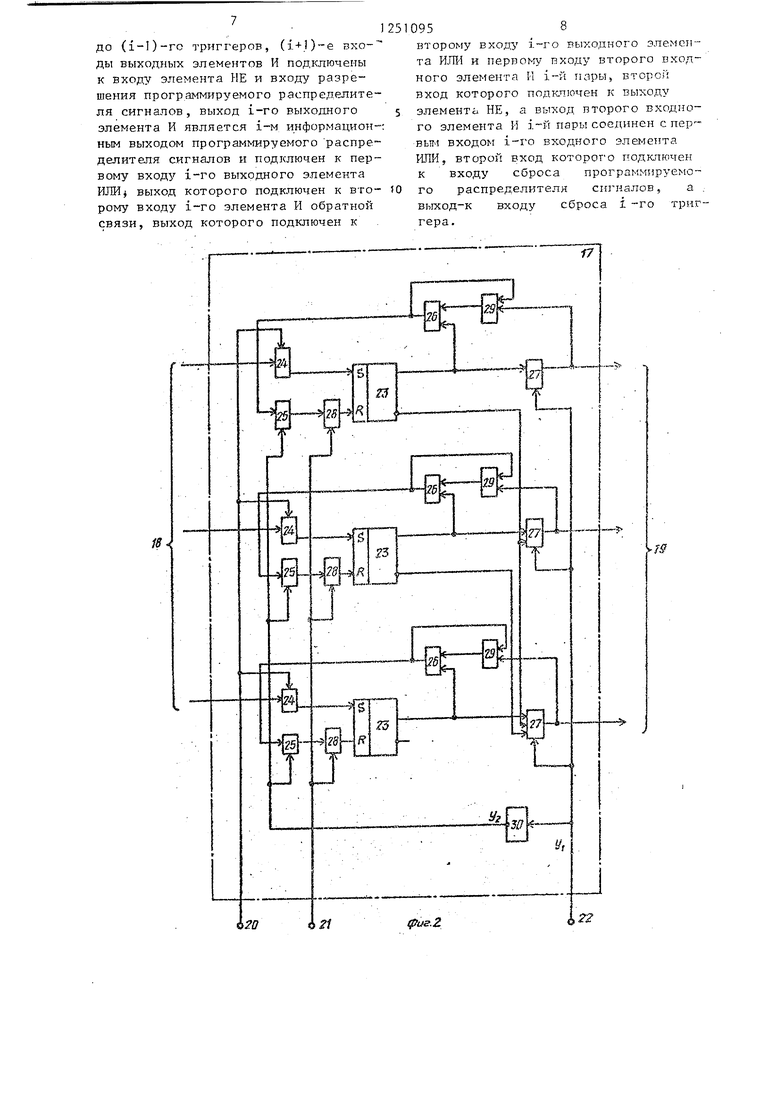

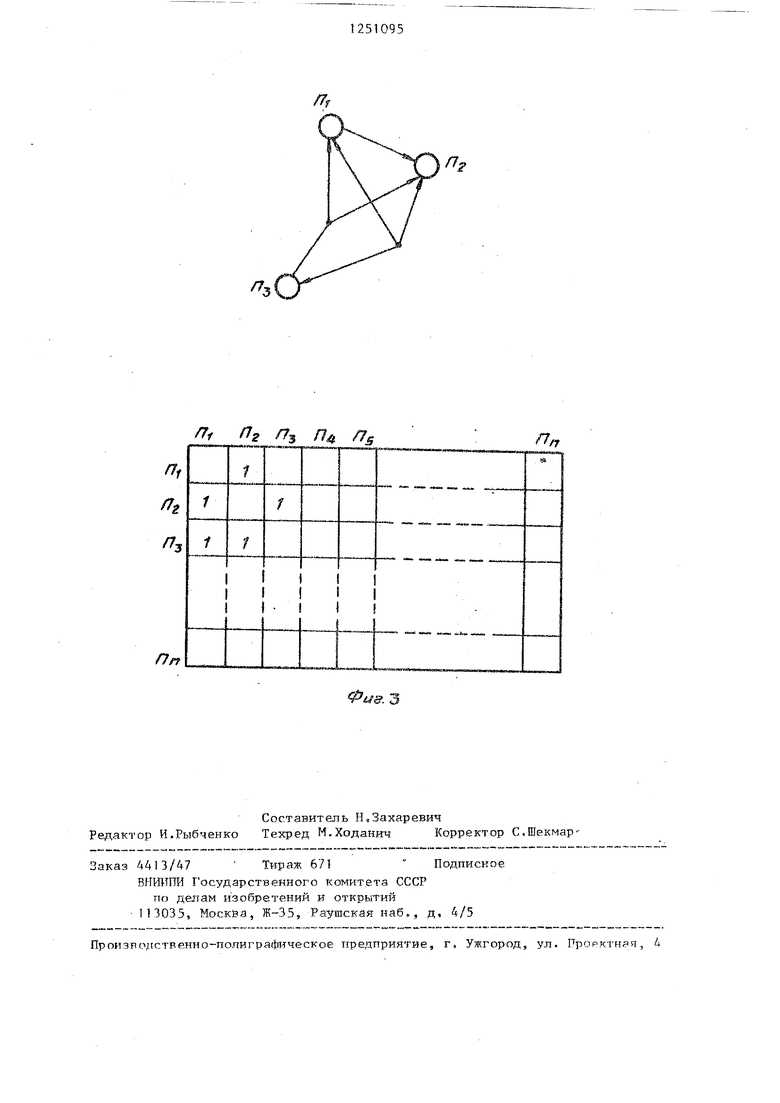

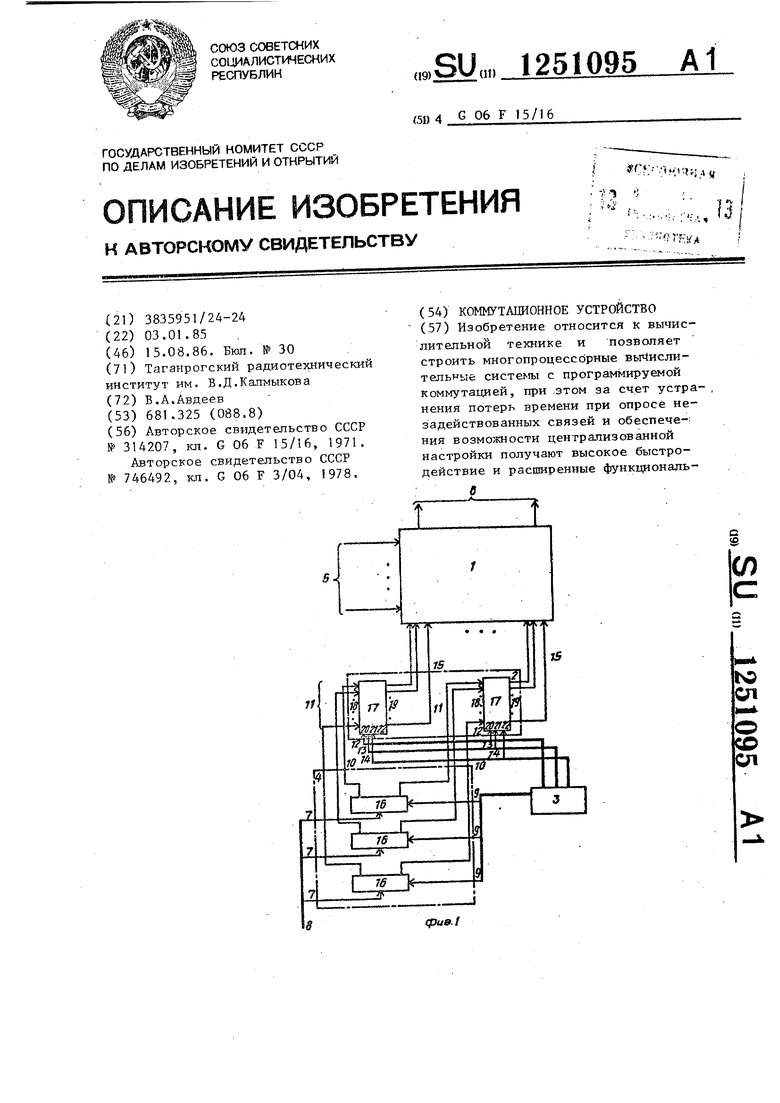

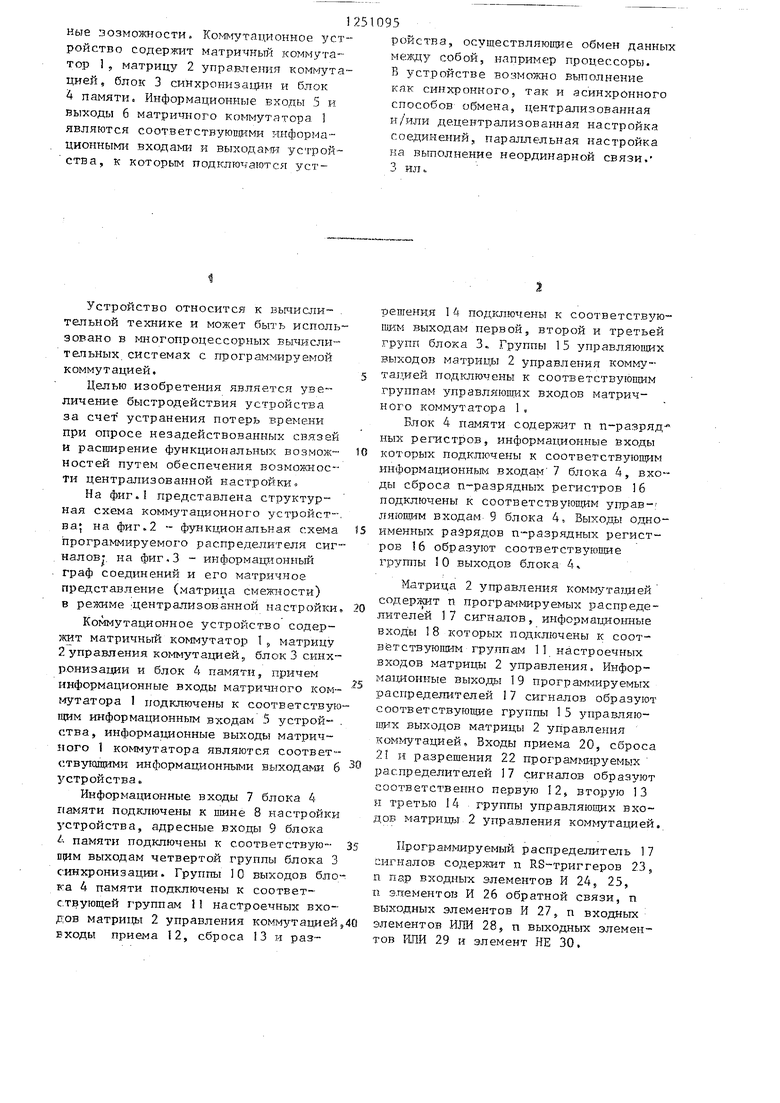

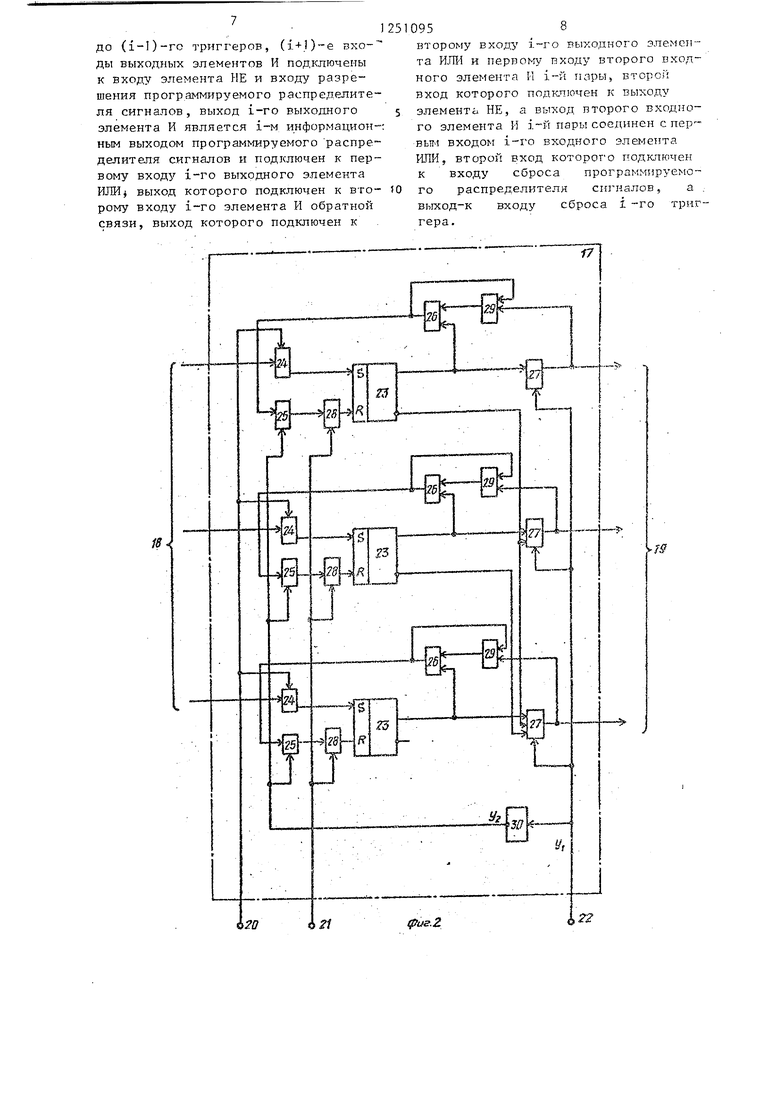

На фиг. представлена структурная схема коммутационного устройст-, вa на фиг.2 - функциональная схема программируемого распределителя сигналов-, на фиг.З - информационный граф соединений и его матричное представление (матрица смежности) в режиме :централизованной настройки,

Коммутационное устройство содержит матричный коммутатор 1 ,, матрицу 2 управления коммутацией, блок 3 синхронизации и блок 4 памяти, причем информационные входы матричного коммутатора I подключены к соответствующим информационным входам 5 устрой- ства, информационные выходы матричного 1 коммутатора являются соответствующими информационными 6 устройства

Информационные входы 7 блока 4 памяти подключены к шине 8 настройки устройства, адресные входы 9 блока i-- памяти подключены к соответствую- выходам четвертой группы блока 3 синхронизации. Группы 10 выходов блока 4 памяти подключены к соответствующей группам 11 настроечных входов матри1ДзТ 2 управления коммутацией входы приема 12, сброса 13 и раз

51095

ройства, осуществляющие обмен данных между собой, например процессоры. В устройстве возможно выполнение как синхронного, так и асинхронного способов обмена, централизованная и/или децентрализованная настройка соединений, параллельная настройка на выполнение неординарной связи. 3 ил

решения 14 подключены к соответствующим выходам первой, второй и третьей групп блока 3. Группы 15 управляющих выходов матрицы 2 управления коммутацией подютючены к соответствующим группам управляюЕгих входов матричного коммутатора 1.

Блок 4 памяти содержит п п-разряд ных регистров, информационные входы которых подключены к соответствующим информационным входам 7 блока 4, входы сброса п разрядных регистров 16 подключены к соответствующим управ- ляющ1- м входам 9 блока 4, Выходы одноименных разрядов п-разрядных регистров 6 образуют соответствующ11е группы 0 выходов блока 4..

Матрица 2 управления коммутатдией содерзшт п. пpoгpaммиpye ыx распределителей 17 сигналов, информатднонные вход ь 18 которых подключены к соответствующим rpynnai- 11 настроечных входов матрицы 2 управления, Инфор- мадаонные выходы 19 программируемых распределителей 7 сигналов образуют соответствующие группы 15 управляю- 1ДИХ выходов матрицы 2 управления коммутацией. Входы приема 20, сброса 2 и разрешения 22 программируемых распределителей 17 сигналов образуют соответственно первую 12, вторую 13 и третью 14 группы управляющих входов матрнирьт 2 управления коммутацией.

Программируемый распределитель 17 с;игналов содержит п RS-триггеров 23, п пар входных элементов И 24, 25, 11 элементов И 26 обратной связи, п выходных элементов И 27, п входных элементов ИЛИ 28, п выходных элементов IVm 29 и элемент НЕ 30.

10

f5

31251

Первый вход первого входного элемента Н 23 i-пары является i-м информационным входом 18 программируемого распределителя 17 сигналов, а второй вход элемента И 24 подключен 5 к входу 20 приема блока 17; (i+l)-e входы выходных элементов И 27 подключены к входу элемента НЕ 30 и к входу 22 разрешения блока 17. Выход i-ro выходного элемента И 27 является i-M информационным выходом 19 блока 17. Второй вход i-ro входного элемента ИЛИ 28 подключен к входу сброса 21 программируемого распределитепя 17 сигналов.

Устройство работает спедующим образом.

Рассмотрим примеры вьтолнения двух режимов: режима централизованной настройки и режима децентрали- зованной настройки.

В первом режиме для реализации требуемых соединений (фиг.З) в блок 4 памяти осуществляется ввод матрицы смежности последовательно по строкам (словам), После ввода матрицы смежности-сигналом ПРИЕМ (ПР), сформированным блоком 3 синхронизации, производится запоминание сигналов запросов в RS-триггерах 23 каж- 30 дого программируемого распределителя 17 сигналов, которые предварительно установлены в нулевое состояние сигналом СБРОС (СБ) от блока 3 синхронизации,35

Программируемый распределитель 17 сигналов предназначен для последовательного формирования сигналов на выходах 19 в соответствии с хранящимися сигналами запросов в RS- 40 триггерах 23, Программируемый распределитель сигналов 17 работает таким образом, что только на одном из его выходов 19 присутствует единичный уровень потенциала, который 45 в матричном коммутаторе 1 осуществляет соединение-информационного входа 5 с информационным выходом 6,

Формирование одного сигнала на ыходе 19 достигается тем, что нуле- 50 вой уровень потенциала с ирверсного ыхода RS-триггера 23 запрещает появление других сигналов на выходах элементов И 27. Только после сброса триггера 23 возможна выработка сиг- 55 ала на соответствующем по порядку ыходе программируемого распределиеля 17 сигналов.

0

1

5

0954

Формирование единичного уровня потенциала на одном из выходов I9 осуществляется по первому разрешаю- щемз сигналу у. блока 3, а по сигналу у 2 У) выполняется сброс RS-триггера, Сброс RS-триггера 23 через один такт становится возможным благодаря наличию в цепи обратной связи несимметричного триггера (э-пе-- менты И 26 и ИЛИ 29), который по сигналу на выходе 19 запоминает единичное значение триггера 23 и подготавливает элемент И 25 к приему сигнала у ,.выполняющего сброс триггера 23,

Таким образом, программируемый распределитель 17 сигналов формирует распределенные во времени и в пространстве сигналы только на тех своих выходах, для которых имеются в наличии соответствующие сигналы запросов.

В рассматриваемом, программ фуемом распределителе сигналов такт времени для передачи информации жест ко задается сигналам ; y.j.,

Нетрудно представить программируемый распределитель 17 сигналов, в котором реализуется плавающий такт времени для передачи информации, определяемый каждым i-м передат .чиком, В этом случае на фиг,2 отсутствуют элементы И 26 и ИЛИ 29, элемент ЙЁ 30, а сброс каждого триггера 23 осуществляется самим соответствующим передатчиком,

Таким образом, предлагаемое устройство может выполнять как синхронный, так и аст1хронный способы обмена информацией.

Второй режим работы устройства отличается от первого тем, что каждьш i-й передатчик непосредственно связан с i-M регистром 16 блока 4 памяти, т.е. ввод слов матрицы смежности (см, фиг.З) производится децентрализованно (каждый i-й передатчик в регистр 16 вводит i-e слово матриц смежности). В дальнейщем работа устройства происходит так же, как и в nepvioM режиме.

Наличие в предлагаемом коммутационном устройстве блока памяти и связанной с ним матрицы управления коммутацией, построенной на программируемых распределителях сигналов, обеспечивает увеличение быстродействия и расширение функциональных возможностей устройства.

Увеличение быстродействия достигается, во-первых5 благодаря тому, что наличие програмг-гнруемых распределителей сигналов в матрице управления коммутащтей позволяет опрапги- вать только те ее входы (выходы блока памяти) , на которых имеются ничные уровни потен1диалов , В известном устройстве матрипа управления коммутацией содер жит регистры сдаи га с циркулирующим единичным разрядом, которые производят последовательный опрос всех ее входов, имею пшх и единичные и нулевые уровни потенциалов, имеются непроизводительные затраты времени.

Во-вторых, в предлагаемом устройстве одновременно выполняется режим настройки связей одного передатчика с несколькими приемниками (неординарная связь) В устройстве-лрото- типе неординарная, связь из-за наличия одного депифратора реагшзуется последовательно во времени, т,е. в г раз медленнееJгде г - число приемников, соединенных с передатчиком.

Коме того, предлагаемое коммутационное устройство обладает более широкими функ1щональньп т возможностями по сравнению с из вестньм устройством; возможность выполнения как синхронного, так и асинхронного способов обмена, централизованная и (или) децентрализованная настройка на вьтолнение желаемых соединений, паралле-пьная настройка устройства на выполнение неординарной связи. . В устройстве-прототипе возмо)сна лишь последовательная децентрализованная настройка на вьтолнение требу емых со един ений.

Формула изобретени

Коммутационное устройство, содержащее матричный коммутатор,, матрицу управления комм:утацией и блок синхронизации, причем информационные входы матричного коммутатора подключены к соответствующим информационным входам устройства, а информационные выходы матричного коммутатора являются соответствуюащми информационными выходами устройства. группы управляющих входов матричного коммутатора соединены с соответствующими группами управляющих вы5

0

5

0

5

0

5

ходов матрицы управления комт.1утацией|, входы приема, сброса и разрешения которой подключены к соответствующим выходам соответственно первой, второй и третьей групп блока синхронизации, отлич ающе еся тем, что, с целью увеличения быстродействия за счет устранения огфосов незадействованных связей и расширения функциональных возможностей устройства путем обеспечения централизованной настройки, устройство содержит блок памяти, информационные входь которого подключены к шине настройки устройства, адресные входы- к срответствующим выходам четвертой,, группы блока синхронизации, an групп (где п число направлений, контролируемых устройством) выходов блока памяти подключены к соответствующим группам настроечных входов матрицы управления коммутацией, причем матрица управления коммутацией содержит п програмг ируемых распределителей сигналов, информационные входы которых образуют соответствуюБ ие группы настроечных входов матрипы управления кoммyтaп eй информационные выходы программируемых распределителей сигналов образуют соответствующие группы управляюптих выходов матрицы управления коммутапдей, а входы приема, сброса и разрешения прог рамми- распределителей сигналов об- разуют соответственно вхо,пы приема, сброса и разрешения матрнць управления ком1-1утацией и каждый программируемый распределитель сигналов содер- 7-сит п триггеров, п пар входных элементов И, п элементов И обратной связи, п выходных элементов И, п входных элементов ИЛИ, п выходных элементов ИЛИ и элемент НЕ, причем вход установки i-ro тригтера (i 1. ,,, п)подключен к выходу перйо- го входного элемента И i-пары, первый вход которого является ин- формагщонным входом программируемого распределителя сг гналов, а второй вход является входом приема ,програм- чаруемого распределителя сигнапов, прямой выход i-ro триггера подключен к первому входу элемента И обратной связи и к первому входу i-ro выходного элемента И, входы с 2--го по i-й которого подклюггены соответственно к инверсньм выходам с 1-го

до (i-l)-ro триггеров, (i+l)e входы выходных элементов И подключены к входу элемента НЕ и входу разрешения прогр.аммируемого распределителя сигналов, выход i-ro выходного элемента И является i-м информациоттным выходом программируемого распределителя сигналов и подключен к первому входз i-ro выходного элемента ИЛИ выход которого подключен к второму входу i-ro элемента И обратной связи, выход которого подключен к

2510958

второму входз i-ro выходного элемента И.ГШ и первому входу второго входного элемента И 1-й пары, второй вход которого подкпючен к выходу 5 элемента НЕ, а выход второго входного элемента И i-й пары соединен с пер- ВЫ1-. входом i-ro входного элемента ИЛИ, второй вход которот о подключен к входу сброса программируемо 0 го распределителя си1 налов, а выход-к входу сброса i-го триггера.

Ь20

й

V/.

Ipue.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство умножения булевых матриц | 1980 |

|

SU959063A1 |

| Многоканальный матричный коммутатор | 1981 |

|

SU964690A1 |

| Устройство для контроля блоков управления | 1986 |

|

SU1365086A1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

Изобретение относится к вычислительной технике и позволяет строить многопроцессбрные выЧисли- тельные системы с программируемой коммутацией, при .этом за счет устранения потерь времени при опросе незадействованных связей и обеспече-; ния возможности центрапизованной настройки получают высокое быстродействие и расширенные функциональtNd СП

/7/ /TS

Фив.Ъ

П,

| УСТРОЙСТВО ДЛЯ СВЯЗИ В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 0 |

|

SU314207A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутационное устройство для вычислительной системы | 1978 |

|

SU746492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-03—Подача