мационный вход третьего регистра сдвига соединен с выходом третьего триггеразадержки, информационный вход которого соединен с выходом первого триггера задержки, вход синхронизации которого соединен с входами синхронизации второго и третьего триггеров задержки, с входами синхрониз-ации первого, второго и третьего регистров сдвига, с входом синхронизации блока сравнения, прямой выход первого триггера соединен с информационным входом второго триггера задержки, выход которого соединен с вторым входом второго элемента ИЛИ, информационный вход первого триггера соединен с выходом пятого элемента И, прямой выход второго триггера соединен с вторыми входами третьего, четвертого и пятого элементов И, вход сброса второго триггера соединен с выходом второго элемента И, первый и второй выходы блока сравнения соединены соответственно с вторым и третьим входами третьего элемента ИЛИ, входы ввода данных первого, второго и третьего регистров сдвига соединены с нулевой шиной устройства, первый и второй информационные входы блока сравнения соединены соответственно с выходами ко «1мутатора устройства и блока задания аргумент а, пер вый и второй входы коммутатора устройства соединены с выходами первого сумматора и первого элемента И соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее три регистра сдвига,два . сумматора., два триггера, три элемента ИЛИ, два элемента И, два триггера задержки, причем выход первого регистра сдвига соединен с первым входом первого сумматора, выход которого соединен с информационным входом первого регистра сдвига, выход второго регистра сдвига соединен с первым входом первого элемента ИЛИ. и с первым входом второго сумматора, вьрсод которого соединен с информационным входом второго регистра сдвига, выход третьего регистра сдвига соединен с входом сброса первого триггера и с первым входом второго элемента ИЛИ, выход которого соединен с первым входом первого элемента И, инверсньай выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с информационным входом первого триггера задержк 1, выход третьего элемента ИЛИ соединен с первым входом второго элемента И, отличающееся тем, что, с целью расширения функциональных возможностей путем получения возможностей выполнения операции извлечения кубического корня наряду с выполнением операции возведения в куб, в него введены третий сумматор, блок сравнения, коммутатор, блок задания аргумента, . третий, четвертый, пятый элементы И, третий триггер задержки, блок управления, содержащий генератор тактовых импульсов, распределитель импульсов, генератор одиночных импульсов, коммутатор, элемент НЕ и элемент задержки, причем выход генератора тактовых импульсов соединен с входом распределителя импульсов и с входом синхронизации блока сравнения, выход п-1-го разряда распределителя импульсов соединен с информационным входом генератора одиночных импульсов, выход п-го разряда распределителя импульсов- соединен с первым входом пятого элемента И и входом сброса блока сравнения, выход первого разряда распределителя импульсов соединен с вторым входом ® первого элемента ИЛИ, выход (n-l)-ro разр}зда распределителя импульсов соединен через элемент задержки с вторым входом второго элемента И, выход генератора одиночных импульсов соединен с информационньи входом второго триг- 2 гера, вход управления генератора одиночных импульсов соединен с первым выходом коммутатора блока, управляющий вход коммутат ора блока через элемент НЕ соединен с нулевой шиной устройства, второй выход коммутатора блока соединен спервым входом сл третьего элемента ИЛИ и с управля1 сл ющими входами первого, второго и третьего регистров сдвига, выходы с первого по п-й разряды распределителя импульсов соединены соответственно с входами блока задания аргумента, второй вход первого сумматора соединен с выходом третьего элемента И, первый вход которого соединен с выходом первого элемента ИЛИ, второй вход второго сумматора соединен с выходом четвертого элемента И, первый вход которого соединен с выходом третьего сумматора, первый и второй входы которого соединены с выходами первого и третьего триггеров задержки соответственно, инфор

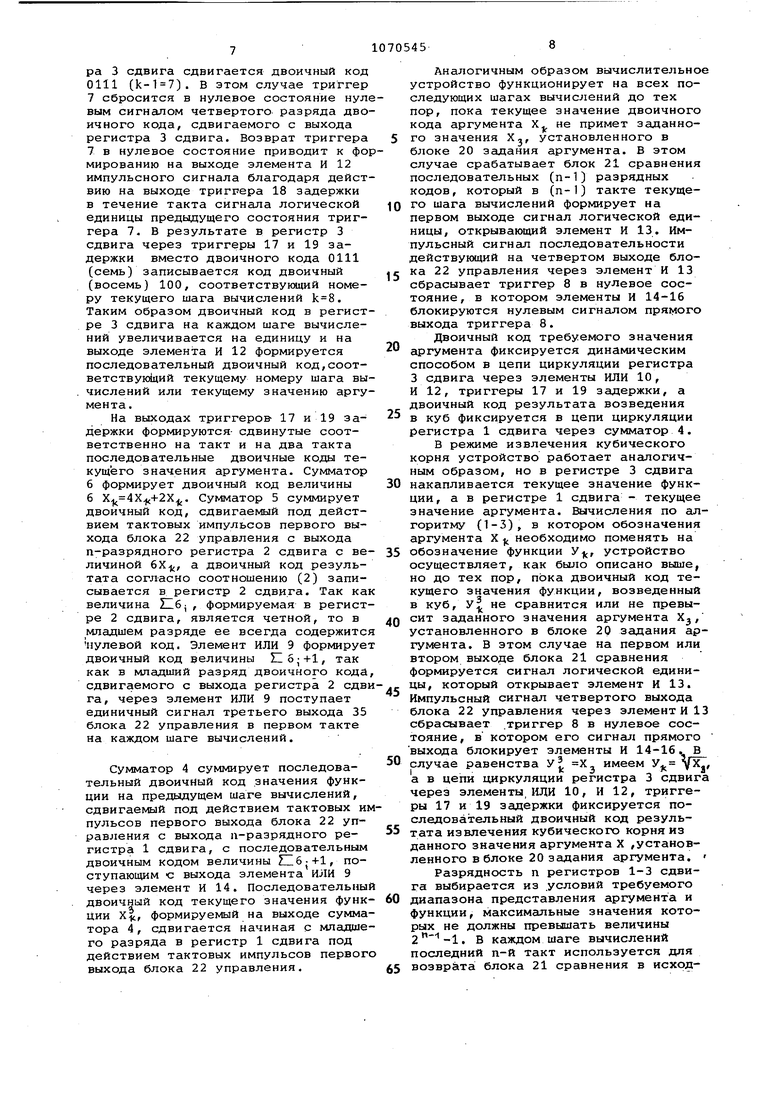

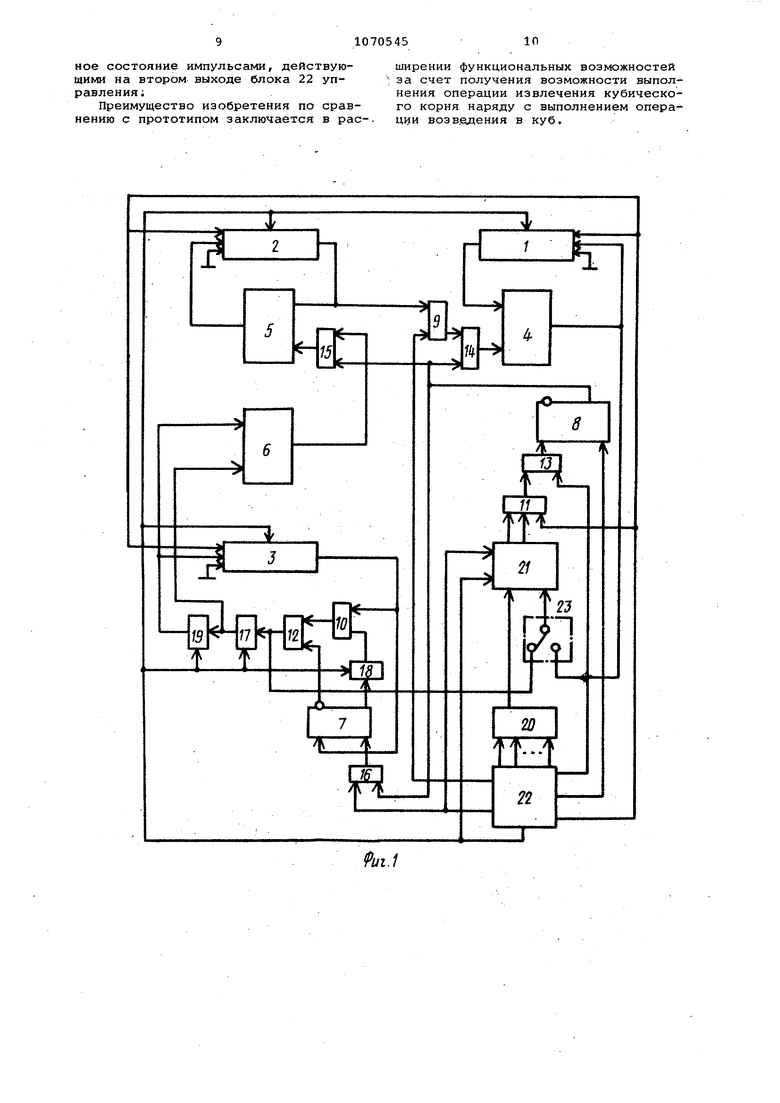

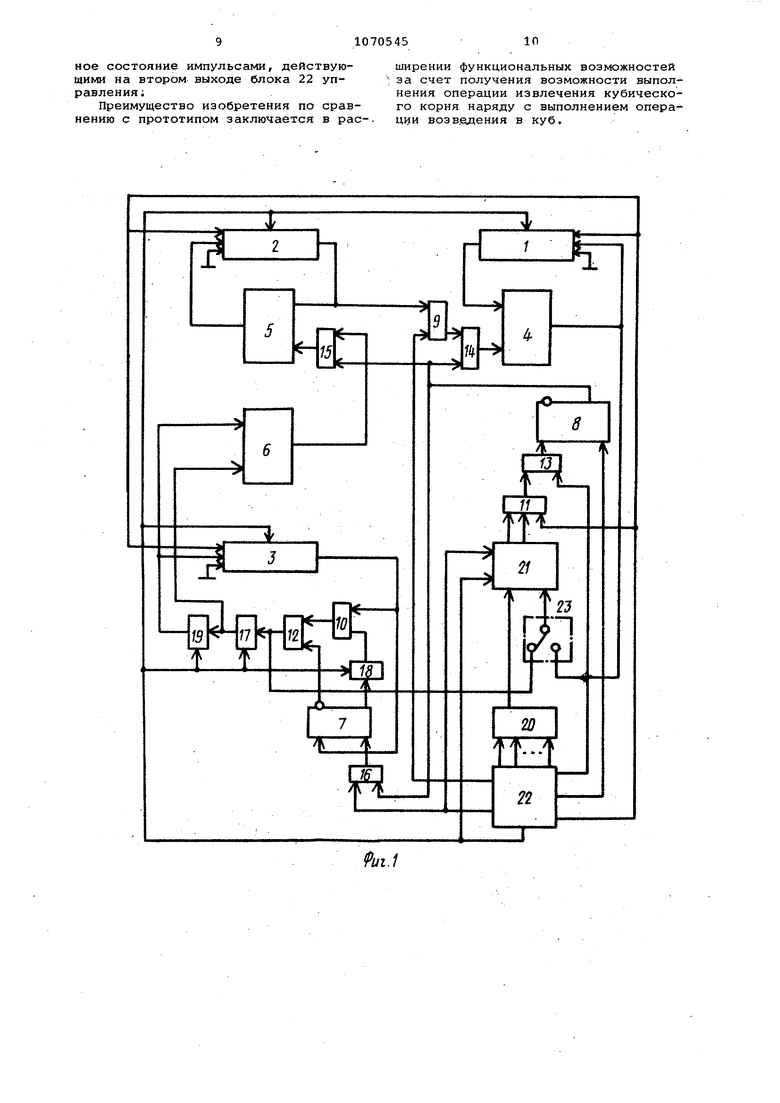

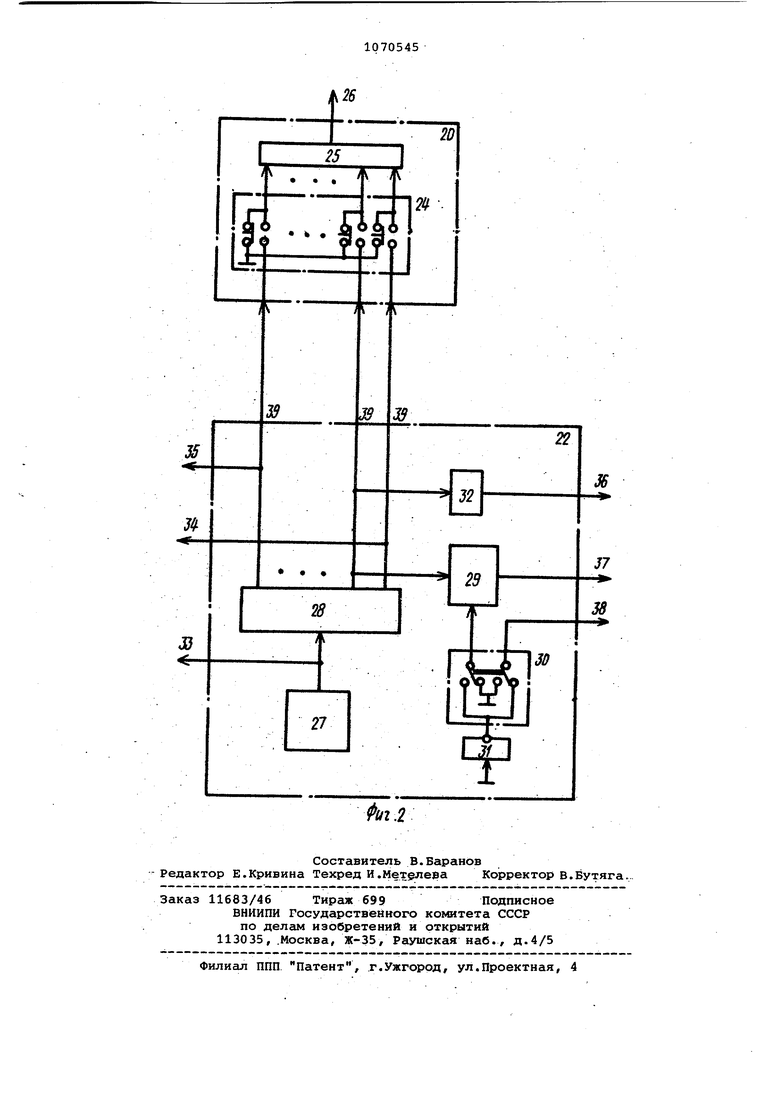

Изобретение относится к автомати ке и вычислительной технике и может быть использовано в цифровых системах управления и в устройствах воспроизведения функциональной зависумости. Известно устройство для возведения в куб, содерж идее три регистра, два сумматора, две группы элементов И, элемент ИЛИ, элемент задержки, вычитающий счетчик и блок управления С1 .. Недостаток данного устройства за ключается в относительной сложности его реализации. Наиболее близким по технической сущности к предлагаемому является устройство для возведения в куб, со держащее три регистра сдвига, два сумматора, два триггера, три элёмен та ИЛИ, два элемента И, два триггера задержки, причем выход первого регистра сдвига соединен с первым входом первого сумматора, выход которого соединен .с информационным входом первого регистра сдвига, выход второго регистра сдвига соедине с первым входом первого элемента ИЛ и с первым входом второго сумматора выход которого соединен с информаци онным входом второго регистра сдвига, выход третьего регистра сдвига соединен с входом сброса первого триггера и с первым входом второго элемента ИЛИ, выход которого соединен с первым входом первого элемента И, инверсный выход первого тригг ра соединен с вторым входом первого элемента И, выход которого соединен с информационным входом первого три гера задержки, выход третьего элемента ИЛИ соединен с первым входом второго элемента И С23. Недостаток известного устройства заключается в ограниченных функциональных возможностях, которые не позволяют вычислять кубический корень. Цель изобретения - расишрение функциональных возможностей Устройства за счет получения возможности выполнения операции извлечения кубического корня наряду с выполнением операции возведения в куб. Поставленная цель достигается тем, что в вычислительное устройство, содержащее три регистра сдвига, два сумматора, два триггера, три элемента ИЛИ, два элемента И, два триггера задержки, причем выход первого регистра сдвига соединен с пер.вым входом первого сумматора, выход которого соединен с информационным входом первого регистра сдвига, выход второго регистра сдвига соединен с первым входом первого элемента ИЛИ и с первым входом второго сумматора, выход которого соединен с информационным входом второго регистра сдвига, выход третьего регистра сдвига соединен с входом сброса первого триггера и с первым входом второго элемента ИЛИ, выход которого соединен с первым входом первого элемента И, инверсный выход первого триггера соединен с вторым входом первого элемента , выход которого соединен с информационным входом первого триггера задержки, выход третьего элемента ИЛИ соединен с первым входом второго элемента И, введены третий сумматор, блок сравнения, коммутатор, блок задания аргумента, тре- . тий, четвертый, пятый элементы И, . ; третий триггер задержки, блок управ ления, содержащий генератор тактовы импульсов, распределитель импульсов генератор одиночных импульсов, коммут.атор, элемент НЕ и элемент задержки , причем выход генератора тактовы импульсов соединен с входом распределителя импульсов и с входом синхронизации блока сравнения, выход (n-l)-ro разряда распределителя импульсов соединен с информационным входом генератора одиночных импульсов, выход п-го разряда распределителя импульсов соединен с первым входом пятого элемента И и входом сброса блока сравнения, выход перво го разряда распределителя импульсов соединения с вторым входом первого элемента ИЛИ, выход (n-l)-ro разряд распределителя импульсов соединен через элемент задержки с вторым вхо дом второго элемента И, выход 1 екератора одиночных импульсов соедкнен с информационным входом второго триггера, вход управления генератор одиночных импульсов соединен с первы выходом коммутатора блока, управляющий вход коммутатора блока через эл мент НЕ соединен с нулевой шиной ус ройства, второй выход коммутатора блока соединен с первым входом третьего элемента ИЛИ и с управлягацими входами первого, второго и третьего регистров сдвига, выходы с первого . по п-й разряды распределителя импуль сов соединены соответственно с входа ми блока задания аргумента, второй вход первого сумматора соединен с выходом третьего элемента И, первый вход которого соединен с выходом пер вого элемента ИЛИ, второй вход второ го сумматора, соединен с выходом чет вертого элемента И, первый вход которого соединен с выходом третьего .сумматора, первый и второй входы которого соединены с выходами первого и третьего триггеров задержки соответственно, информационный вход третьего регистра сдвига сгоединен с выходом третьего триггера задержки, информационный вход которого соединен с выходом первого триггера задержки, вход синхронизации которого соединен с входами синхронизации второго и третьего триггеров задержки, со входами синхронизации первого, второго и третьего регистров сдвига, с входом синхронизации блока сравнения, прямой выход первого триг гера соединен с информационным входом второго триггера задержки, выход которого соединен с вторым входом второго элемента ИЛИ, информадионный вход первого триггера соединен с выходом пятого элемента И, прямой выход второго триггера соединен с вторыми входс1ми третьего, четвертого и пятого элементов И, вход сброса второго триггера соединен с выходами второго элемента И, первый и второй выходы блока сравнения соединены соответственно с вторым и третьим входс ми третьего элемента, ИЛИ, входы ввода данных, первого, второго и третьего регистров сдвига соединены с нулевой шиной устройства, первый и второй информационные входы блока сравнения соединены соответственно с выходами коммутатора устройства и блока задания аргумента, первый и второй входы коммутатора устройства соединены с выходами первого сумматора и первого элемента И соответственно. На фиг.1 изображена структурная схема вычислительного устройства; на фиг.2 - структурные схемы блока задания аргумента и блока управления. Вычислительное устройство содержит три регистра 1-3 сдвига, три сумматора.4-6, S-триггер 7, RS-триггер 8, три элемента ИЛИ 9-11, пять элемен.тов И 12-16, три триггера 17-19 задержки, блок 20 задания аргумента, блок 21 сравнения, блок 22 управления и коммутатор 23. Блок 20 задания аргумента содержит коммутатор 24 и элемент ИЛИ 25, выход 26. Блок 22 управления содержит генератор 27 тактовых импульсов, распределитель 28 импульсов, генератор 29 одиночных импульсов, коммутатор 30, элемент НЕ 31 и элемент 32 задержки на длительность тактового импульса, йлход генератора 27 тактовых импульсов соединен с входом распределителя 28 импульсов и является первым выходом 33 блока 22 управления. Выход п-го и первого разрядов распределителя 28 импульсов соединены соответственно шинами 34 и 35 с вторым и третьим выходами блока 22 управления. Выход (п-1)-го разряда распределителя 28 импульсов соединен с информационным входом генератора 29 одиночных импульсов и через элемент 32 задержки - с четвертым выходом 36 блока 22 управления, пятый выход .37 которого соединен с выходом генератора 29 одиночных импульсов, вход управления которого соединен с первым выходом коммутатора 30, вход которого через элемент НЕ 21 соединен с нулевой шиной устройства. Второй выход коммутатора 30 соединен с шестым выходом 38 блока 22 управления. Выходы с первого по п-й разряды распределителя 28 импульсов являются седьмой группой выходов 39 блока.22 управления. Шлчислительное устройство работает следующим образом. В исходном состоянии на шестом выходе 38 блока 22 управления действует сигнсШ логической единицы, который поступает на управляющие входы регистров 1-3 сдвига и устанавливает их в нулевое состояние, поскольку н их входах ввода данных действует си нал логического нуля с нулевой шины устройства. Сигнал логической едини цы на шестом выходе 38 блока 22 управления формируется с помощью комм татора 30. В исходном состоянии ком мутатор 30 подключает выход элемента НЕ 31 к шине шестого выхода 38 блока 22 управления (фиг.2).Сигнал логической единицы шестого выхода 38 блока 22 управления через элемент ИЛИ 11 открывает элемент И 13, через который на вход сброса тригге ра 8 поступает последовательность импульсов четвертого выхода блока 22 управления, на пятом выходе кото рого действует сигнал логического нуля. Триггер 8 устанавливается в нулевое состояние и блокирует сигна лом прямого выхода элементы И 14-16 Триггер 7 устанавливается в нулевое состояние нулевым сигналом выхода регистра 3 сдвига. Таким образом в исходном состояНИИ регистры 1-3 сдвига, а также триггеры 7 и 8 находятся в нулевом состоянии. Из сигналов генератора 27 тактовых импульсов распределитель 28 импульсов формирует на п выходах (и количество разрядов регистров 1 и 2 п последовательностей импульсов дли тельностью Т , периодом Tsn.f и сдвинутых друг относительно друга . на время С 1/, где f - частота тактовых импульсов. С помощью коммутатора 24 блока 2 задания аргумента набирают требуемый двоичный код аргумента. Коммутатор 24 подключает в единичных разрядах п-разрядного двоичного кода аргумента соответствующий выход распредели теля 28 импульсов к входу элемента ИЛИ 25, на выходе которого форми руется последовательный двоичный код заданного значения аргумента. С помощью коммутатора 23 устанав ливают вид выполняемой операции. В режиме возведения в куб комг татор 23 подключает к первому информацион ному, входу блока 21 сравнения выход элемента И 12, а в режиме вычисления кубического корня - выход сумматора 4 . Рассмотрим работу устройства в режиме возведения в куб. В этом режиме устройство для возведения в куб реализует следующие операции: .й ( 6, d 6,+бХ.. (2) in к 1. ,(3) где ЛХ.1; X ik - значение аргумента на k шаге вычисленияj значение функции на k и k-1 шагах вычисления. После установки в блоке 20 задания аргумента двоичного кода заданного значения аргумента и установки режима работы с помощью коммутатора 23 осуществляется пуск устройства посредством коммутатора 30 блока 22 управления. Переключение коммутатора 30 в режим вычислений обеспечивает поступление сигнала логической единицы с выхода элемента НЕ 31 на вход управления генератора 29 одиночных импульсов, который формирует из последовательности импульсов (п-1)-го разряда распределителя 28 импульсов одиночный импульс, поступающий по шине на пятый выход 37 блока 22 управления и на информационный вход триггера 8. Триггер 8 устанавливается в единичное состояние, в котором сигнал логической единицы его прямого выхода откр ывает элементы И 14-16. Элемент И 16 подключает информационный вход триггера 7 к второму выходу блока 22 управления, на котором -действует последовательность импульсов п-го разряда распределителя 28 импульсов. Каждый импульс этой последовательности определяет конец одного шага вычислений. За один шаг вычислений содержимое регистра 3 сдвига увеличивается на единицу. Регистр 3 сдвига имеет п-2 двоичных разрядов и дополняется триггералш 17 и 19 задержки на такт до п разрядов. В регистре 3 сдвига формируется текущий двоичный код аргумента X согласно, соотношению (3). Рассмотрим работу регистра 3 сдвига на k-M шаге вычислений в течение п-тактов, так как предыдущие и все последующие шаги вычислей1ий выполняются аналогичным образом. Триггер 7 устанавливается в единичное состояние в п-м такте k-1 шага вычислений импульсом второго выхода блока 22 управления К моменту первого такта следующего k-ro шага на выходе триггера 18 задержки на такт формируется сигнал логической единицы, который через элемент ИЛИ 10 поступает на первый вход элемента И 12, закрытого сигналом логического нуля инверсного выхода триггера 7. Возврат триггера 7 в нулевое состояние обеспечивает первый нулевой сигнал в любом разряде, начиная с младшего двоичного кода, который сдвигается с выхода регистра 3 сдвига под действием тактовых импульсов первого выхода блока 22 управления. Например, если рассматривается восьмой шаг (), то с выхода регистpa 3 сдвига сдвигается двоичный код 0111 (). В этом случае триггер 7 сбросится в нулевое состояние нулевым сигналом четвертого разряда двоичного кода, сдвигаемого с выхода регистра 3 сдвига. Возврат триггера 7 в нулевое состояние приводит к формированию на выходе элемента И 12 импульсного сигнала благодаря действию на выходе триггера 18 задержки в течение такта сигнала логической единицы предыдущего состояния триггера 7. В результате в регистр 3 сдвига через триггеры 17 и 19 задержки вместо двоичного кода 0111 (семь) записывается код двоичный (восемь) 100, соответствующий номеру текущего шага вычислений . Таким образом двоичный код в регистре 3 сдвига на каждом шаге вычислений увеличивается на единицу и на выходе элемента И 12 формируется последовательный двоичный код,соответству1Ыдий текущему номеру шага вычислений или текущему значению аргумента.

На выходах триггеров 17 и 19 задержки формируются- сдвинутые соответственно на такт и на два такта последовательные двоичные коды текущего значения аргумента. Сумматор 6 формирует двоичный код величины 6 . Сумматор 5 суммирует двоичный код, сдвигаемый под действием тактовых импульсов первого выхода блока 22 управления с выхода п-разрядного регистра 2 сдвига с величиной 6Х, а двоичный код результата согласно соотношению (2) записывается в регистр 2 сдвига. Так как величина Щб , формируемая в регистре 2 сдвига, является четной, то в младшем разряде ее всегда содержится нулевой код. Элемент ИЛИ 9 формирует двоичный код величины 11б;+1, так как в младший разряд двоичного кода, сдвигаемого с выхода регистра 2 сдвига, через элемент ИЛИ 9 поступает единичный сигнал третьего выхода 35 блока 22 управления в первом такте на каждом шаге вычислений.

Сумматор 4 суммирует последовательный двоичный код .значения функции на предыдущем шаге вычислений, сдвигаемый под действием тактовых импульсов первого выхода блока 22 управления с выхода 11-разрядного регистра 1 сдвига, с последовательным двоичным кодом величины ZIl6j+l, поступающим с выхода элемента ИЛИ 9 через элемент И 14. Последовательный двоичный код текущего значения функции Х, формируемый на выходе сумматора 4, сдвигается начиная с младшего разряда в регистр 1 сдвига под действием тактовых импульсов первого выхода блока 22 управления.

Аналогичным образом вычислительное устройство функционирует на всех последующих шагах вычислений до тех пор, пока текущее значение двоичного кода аргумента Х не примет заданно5 го значения Xj, установленного в блоке 20 защания аргумента. В этом случае срабатывает блок 21 сравнения последовательных (п-1) разрядных кодов, который в (п-1) такте текуще0 го шага вычислений формирует на

первом выходе сигнал логической единицы, открывающий элемент И 13. Импульсный сигнал последовательности действующий на четвертом выходе блос ка 22 управления через элемент И 13 сбрасывает триггер 8 в нулевое состояние, в котором элементы И 14-16 блокируются нулевым сигналом прямого выхода триггера 8.

Двоичный код требуемого значения

аргумента фиксируется динамическим способом в цепи циркуляции регистра 3 сдвига через элементы ИЛИ 10, И 12, триггеры 17 и 19 задержки, а двоичный код результата возведения

5 в куб фиксируется в цепи циркуляции регистра 1 сдвига через сумматор 4. В режиме извлечения кубического корня устройство работает аналогичным образом, но в регистре 3 сдвига

0 накапливается текущее значение функции, а в регистре 1 сдвига - текущее значение аргумента. Вычисления по алгоритму (1-3), в котором обозначения аргумента X необходимо поменять на

5 обозначение функции У, устройство осуществляет, как было описано выше, но до тех пор, пока двоичный код текущего значения функции, возведенный в куб, У не сравнится или не превыQ сит заданного значения аргумента Х, установленного в блоке 20 задания аргумента. В этом случае на первом или втором выходе блока 21 сравнения формируется сигнал логической единицы, который открывает элемент И 13. Импульсный сигнал четвертого выхода блока 22 управления через элемент И 13 сбрасывает триггер 8 в нулевое состояние, в котором его сигнал прямого выхода блокирует элементы И 14-16. В

0 случае равенства У Х, имеем У V а в цепи циркуляции регистра 3 сдвига через элементы, ИЛИ 10, И 12, триггеры 17 и 19 задержки фиксируется последовательный двоичный код резуль5 тата извлечения кубического корня из данного значения аргумента X ,установленного в блоке 20 задания аргумента.

Разрядность п регистров 1-3 сдвига выбирается из .условий требуемого

0 диапазона представления аргумента и функции, максимальные значения которых не должны превышать величины . В каждом шаге вычислений последний п-й такт используется для

5 возврата блока 21 сравнения в исходное состояние импульсами, действующими на втором, выходе блока 22 управления;

Преимущество изобретения по сравнению с прототипом заключается в расширении функциональных возможностей за счет получения возможности выполнения операции извлечения кубического корня наряду с выполнением операции возв.едения в куб.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для возведения во вторую и третью степень | 1976 |

|

SU590729A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для возведения в куб | 1979 |

|

SU868755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-30—Публикация

1982-12-17—Подача