Изобретение относится к импульсной и вычислительной технике, в частности к импульсным счетчикам-делителям с коэффициентом деления 2, 3, 6 и 12, и может быть применено в устройствах промьшшенной автоматики и вычислительной техники.

Цель изобретения - повышение ремонтопригодности устройства.

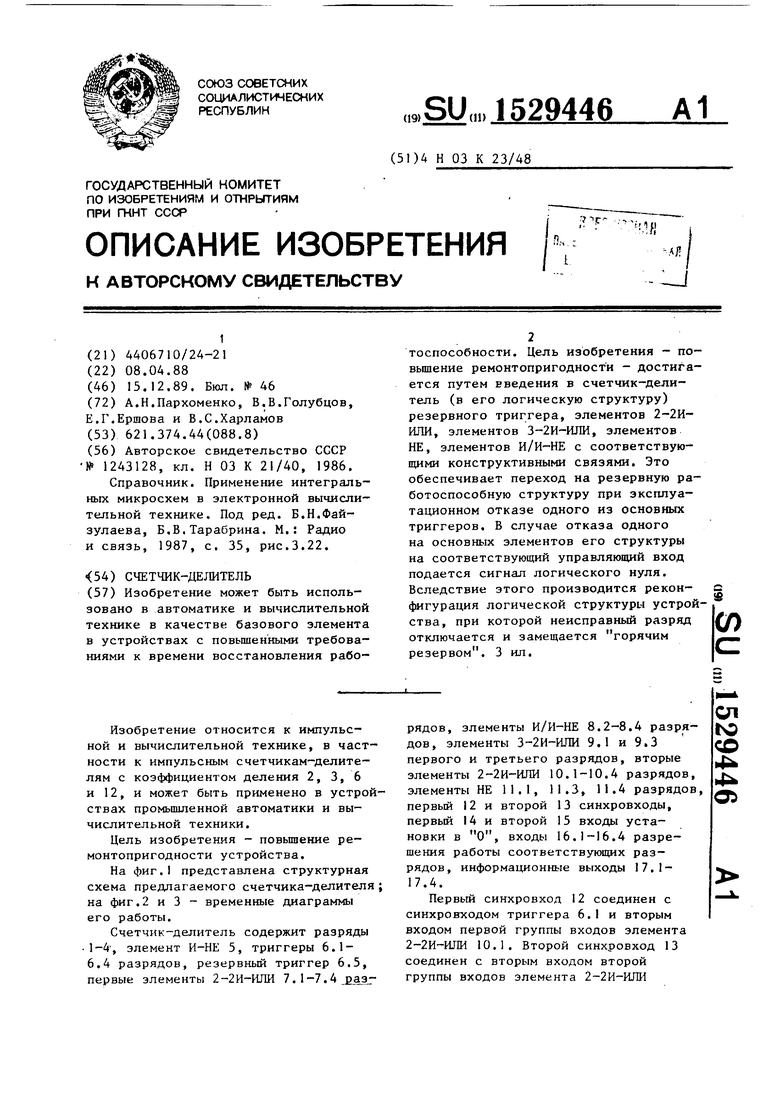

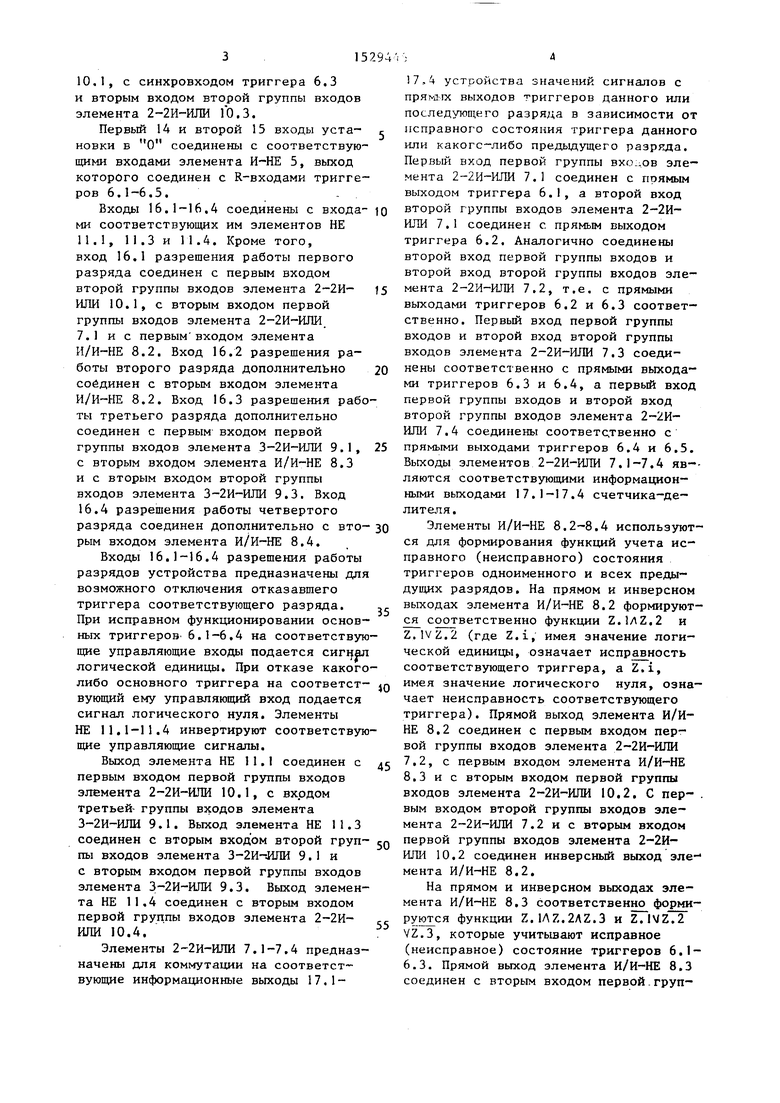

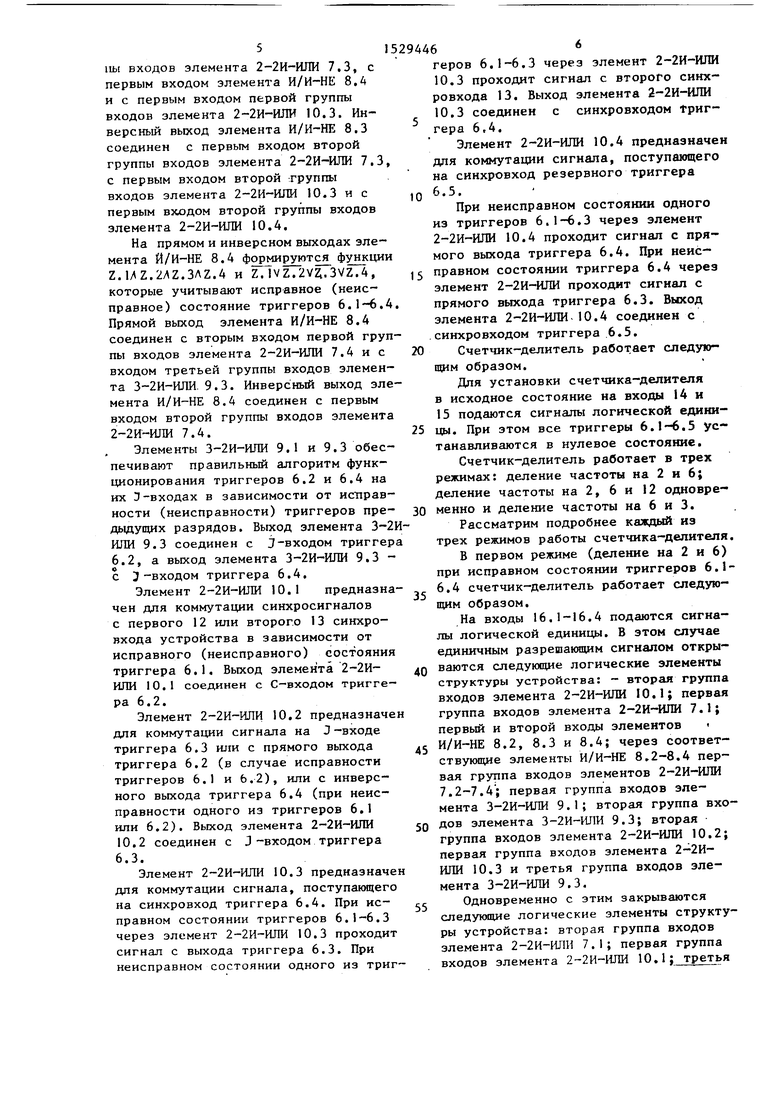

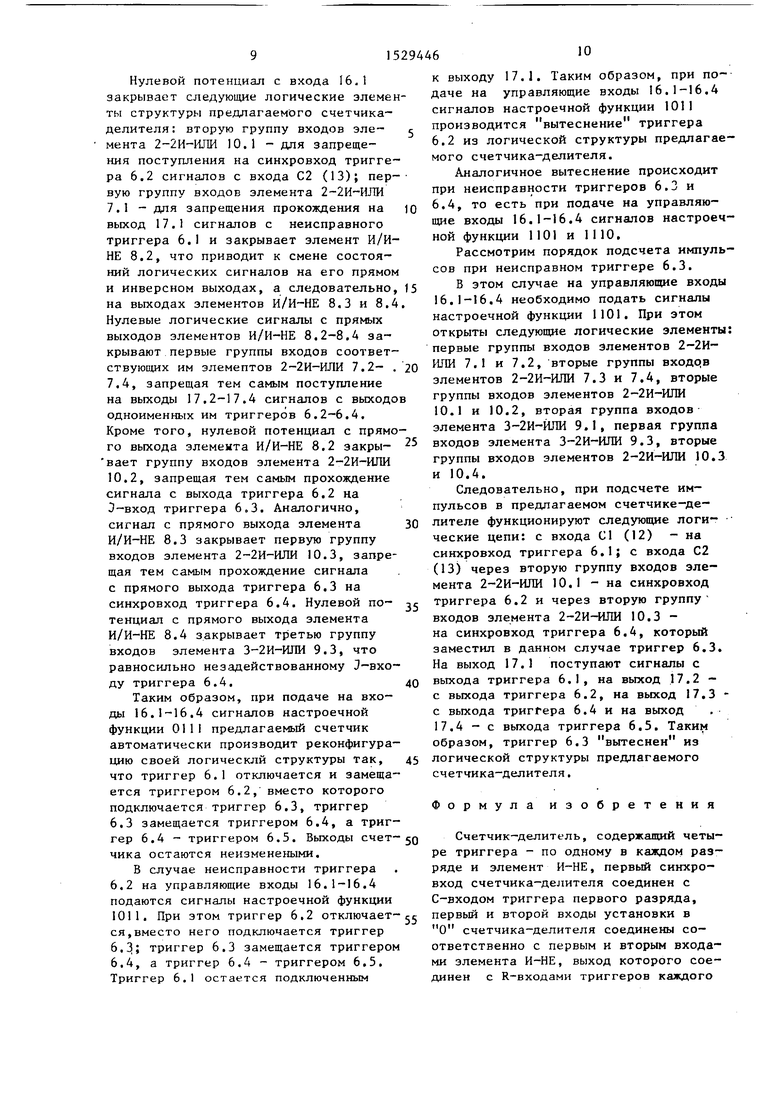

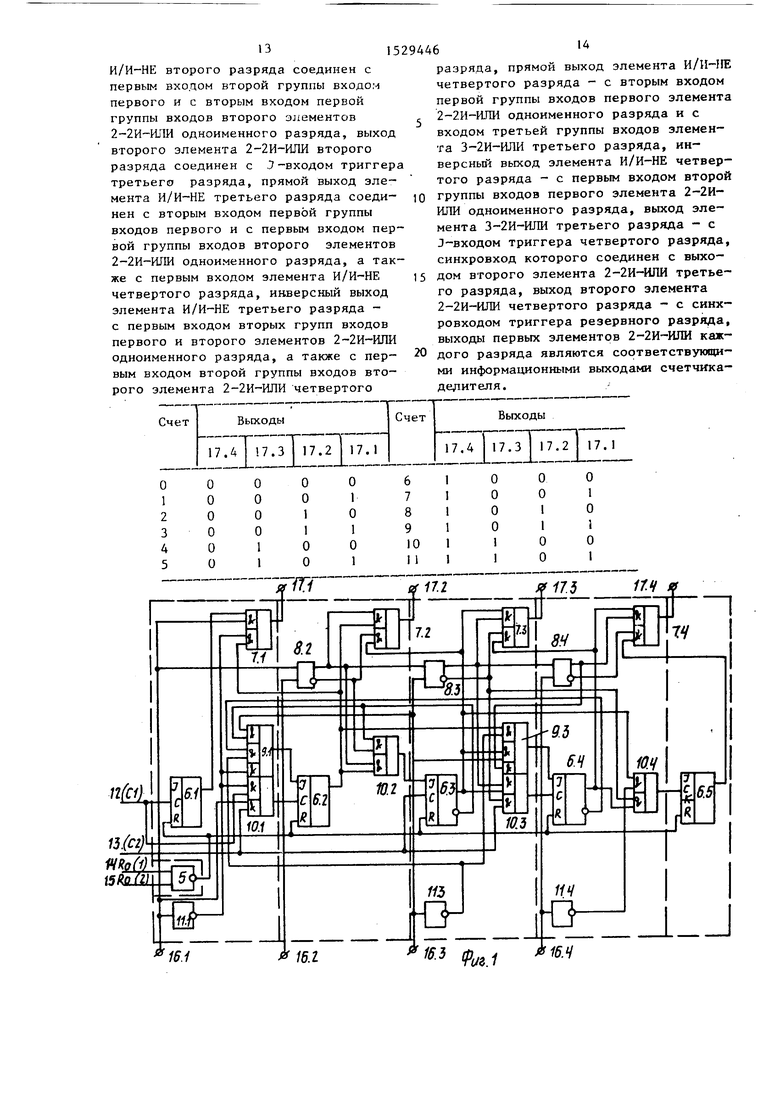

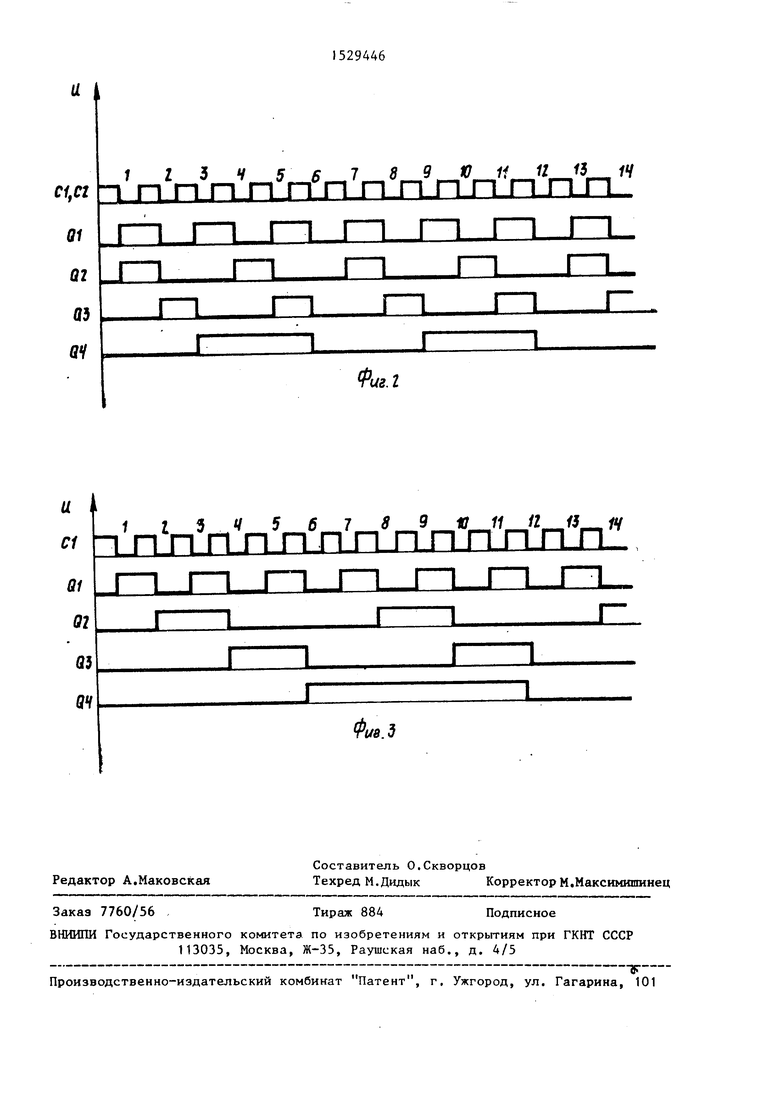

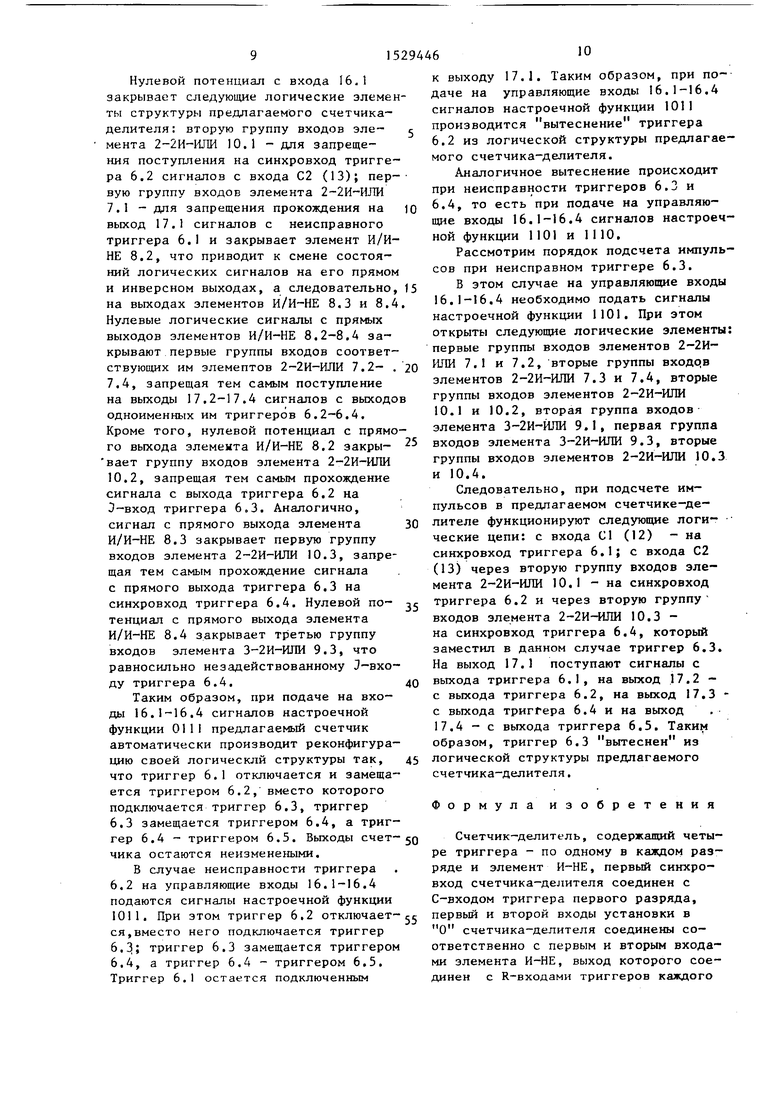

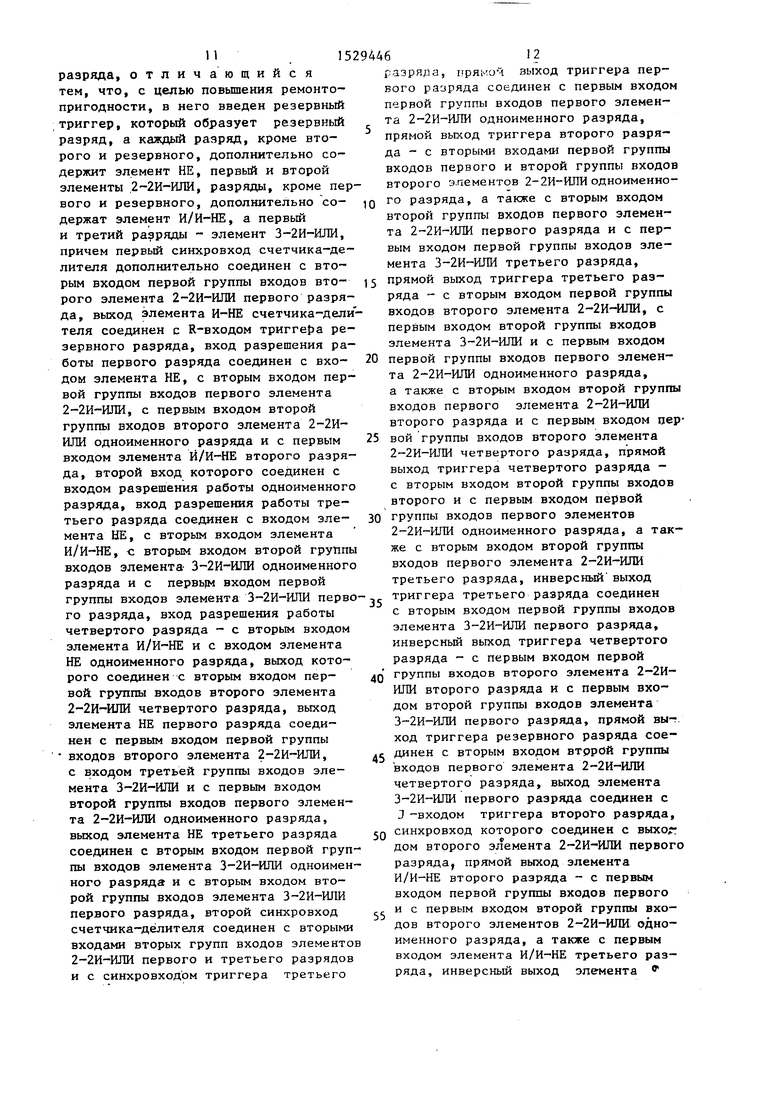

На фиг.1 представлена структурная схема предлагаемого счетчика-делителя ; на фиг.2 и 3 - временные диаграммы его работы.

Счетчик-делитель содержит разряды 1-4, элемент И-НЕ 5, триггеры 6.1- 6.4 разрядов, резервный триггер 6,5, первые элементы 2-2И-ИЛИ 7.1-7.4 EAST

рядов, элементы И/И-НЕ 8.2-8.4 разрядов, элементы 3-2И-ИЛИ 9.1 и 9.3 первого и третьего разрядов, вторые элементы 2-2И-ИЛИ 10.1-10.4 разрядов, элементы НЕ 11.1, 11.3, 11.4 разрядов, первый 12 и второй 13 синхровходы, первый 14 и второй 15 входы установки в О, входы 16.1-16.4 разрешения работы соответствующих разрядов, информационные выходы 17.1- 17.4.

Первый синхровход 12 соединен с синхровходом триггера 6.1 и вторым входом первой группы входов элемента 2-2И-ИЛИ 10.1. Второй синхровход 13 соединен с вторым входом второй группы входов элемента 2-2И-ИЛИ

сл

10

о

10.1, с синхровходом триггера 6,3 и вторым входом второй группы входов элемента 2-2И-ИЛИ ГО.З.

Первый 14 и второй 15 входы уста- новки в О соединены с соответствующими входами элемента И-НЕ 5, выход которого соединен с R-входами триггеров 6.1-6.5,Входы 16.1-16.4 соединены с входа- ми соответствующих им элементов НЕ 11.1, 11.3 и 11.4. Кроме того, вход 16.1 разрешения работы первого разряда соединен с первым входом второй группы входов элемента 2-2И- ИЛИ 10.1, с вторым входом первой группы входов элемента 2-2И-ИЛИ 7.1 и с первым входом элемента И/И-НЕ 8.2, Вход 16.2 разрешения работы второго разряда дополнительно соединен с вторым входом элемента И/И-НЕ 8.2. Вход 16.3 разрешения работы третьего разряда дополнительно соединен с первым входом первой группы входов элемента 3-2И-ИЛИ 9.1, с вторым входом элемента И/И-НЕ 8.3 и с вторым входом второй группы входов элемента 3-2И-ИЛИ 9.3. Вход 16.4 разрешения работы четвертого разряда соединен дополнительно с вто- рым входом элемента И/И-НЕ 8,4.

Входы 16,1-16.4 разрешения работы разрядов устройства предназначены для возможного отключения отказавшего триггера соответствующего разряда, При исправном функционировании основных триггеров 6.1-6,4 на соответствующие управляющие входы подается сигцал логической единицы. При отказе какого либо основного триггера на соответст- вующий ему управляющий вход подается сигнал логического нуля. Элементы НЕ 11,1-11,4 инвертируют соответствующие управляющие сигналы.

Выход элемента НЕ 11.1 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ 10,1, с входом третьей- группы входов элемента 3-2И-ИЛИ 9.1, Выход элемента НЕ 11.3 соединен с вторым входом второй груп- пы входов элемента 3-2И-ЛЛИ 9,1 и с вторым входом первой группы входов элемента 3-2И-ИЛИ 9,3, Выход элемента НЕ 11.4 соединен с вторым входом первой группы входов элемента 2-2И- ИЛИ 10,4,

Элементы 2-2И-ИЛИ 7.1-7.4 предназначены для коммутации на соответствующие информационные выходы 17.1

с Q

Q

7,4 устройства значений сигналов с прямнх выходов триггеров данного или последующего разряда в зависимости от исправного состояния триггера данного или какого-либо предыдущего разряда. Первый вход первой группы вхо:лов элемента 2-2И-ИЛИ 7,1 соединен с прямым выходом триггера 6.1, а второй вход второй группы входов элемента 2-2И- ИЛИ 7,1 соединен с прямым выходом триггера 6.2. Аналогично соединены второй вход первой группы входов и второй вход второй группы входов элемента 2-2И-ИЛИ 7,2, т.е. с прямыми выходами триггеров 6.2 и 6.3 соответственно. Первый вход первой группы входов и второй вход второй группы входов элемента 2-2И-ИЛИ 7,3 соединены соответственно с прямыми выходами триггеров 6.3 и 6,4, а первый вход первой группы входов и второй вход второй группы входов элемента 2-2И- ИЛИ 7,4 соединены соответственно с прямыми выходами триггеров 6.4 и 6.5. Выходы элементов 2-2И-Ш1И 7.1-7,4 яв-- ляются соответствующими информационными выходами 17.1-17.4 счетчика-делителя.

Элементы И/И-НЕ 8.2-8,4 используются для формирования функций учета исправного (неисправного) состояния триггеров одноименного и всех предыдущих разрядов. На прямом и инверсном выходах элемента И/И-НЕ 8,2 формируются соответственно функции Z,MZ,2 и Z.1VZ,2 (где Z,i, имея значение логической единицы, означает исправность соответствующего триггера, а Z.i, имея значение логического нуля, означает неисправность соответствующего триггера). Прямой выход элемента И/И- НЕ 8,2 соединен с первым входом первой группы входов элемента 2-2И-ИЛИ

7.2,с первым входом элемента И/И-НЕ 8,3 и с вторым входом первой группы входов элемента 2-2И-Ш1И 10,2, С пер- . вым входом второй группы входов элемента 2-2И-ИЛИ 7.2 и с вторым входом первой группы входов элемента 2-2И- ИЛИ 10.2 соединен инверсный выход эле- мента И/И-НЕ 8,2,

На прямом и инверсном выходах элемента И/И-НЕ 8,3 соответственно формируются функции Z,1AZ.2AZ.3 и zTlV/zTT VZ.3, которые учитьшают исправное (неисправное) состояние триггеров 6,16.3.Прямой выход элемента И/И-НЕ 8,3 соединен с вторым входом первой.групс f J - J , , „ f

lib входов элемента 2-2И-ИЛИ 7.3, с первым входом элемента И/И-НЕ 8.А и с первым входом первой группы входов элемента 2-2И-ИЛИ 10.3. Инверсный выход элемента 8.3 соединен с первым входом второй группы входов элемента 2-2И--ИЛИ 7.3, с первым входом второй труппы входов элемента 2-2И-ИЛИ 10.3 и с первым входом второй группы входов элемента 2-2И-ИЛИ 10.4.

На прямом и инверсном выходах элемента Й/И-НЕ 8.4 формируются функции Z.MZ.2AZ.3AZ.4 и ZJVZ72V 3VZ74, которые учитывают исправное (неисправное) состояние триггеров 6.1-6.4 Прямой выход элемента И/И-НЕ 8.4 соединен с вторым входом первой группы входов элемента 2-2И-ИЛИ 7.4 и с входом третьей группы входов элемента 3-2И-ИЛИ. 9.3. Инверсный выход элемента И/И-НЕ 8.4 соединен с первым входом второй группы входов элемента 2-2И-ИЛИ 7.4.

Элементы 3-2И-ИЛИ 9.1 и 9.3 обеспечивают правильный алгоритм функционирования триггеров 6.2 и 6.4 на их 3-входах в зависимости от истлрав- ности (неисправности) триггеров предыдущих разрядов. Выход элемента 3-2И ИЛИ 9.3 соединен с j-входом триггер 6.2, а выход элемента 3-2И-ИЛИ 9.3 - с 3-входом триггера 6.4.

Элемент 2-2И-ИЛИ 10.1 предназначен для коммутации синхросигналов с первого 12 или второго 13 синхро- входа устройства в зависимости от исправного (неисправного) состояния триггера 6.1. Выход элемента 2-2И- ИЛИ 10.1 соединен с С-входом триггера 6.2.

Элемент 2-2И-ИЛИ 10.2 предназначен для коммутации сигнала на J-входе триггера 6.3 или с прямого выхода триггера 6.2 (в случае исправности триггеров 6.1 и 6.2), или с инверсного выхода триггера 6.4 (при неисправности одного из триггеров 6.1 или 6.2). Выход элемента 2-2И-ИЛИ 10.2 соединен с J-входом триггера 6.3.

Элемент 2-2И-ИЛИ 10.3 предназначен для коммутации сигнала, поступающего на синхровход триггера 6.4. При исправном состоянии триггеров 6.1-6.3 через элемент 2-2И-ИЛИ 10.3 проходит сигнал с выхода триггера 6.3. При неисправном состоянии одного из триг0

5

0

5

0

5

0

5

0

5

геров 6.1-6.3 через элемент 2-2И-ИЛИ 10.3 проходит сигнал с второго сикх- ровхода 13. Выход элемента 2-2И-ИЛИ 10.3 соединен с синхровходом Триггера 6,4.

Элемент 10.4 предназначен для коммутации сигнала, поступающего на сиихровход резервного триггера 6.5.

При неисправном состояюш одного из триггеров 6.1-6.3 через элемент 2-2И-ИЛИ 10.4 проходит сигнал с прямого выхода триггера 6.4. При неисправном состоянии триггера 6.4 через элемент 2-2И-ИЛИ проходит сигнал с прямого выхода триггера 6.3. Выход элемента 2-2И-ИЛИ 10.4 соединен с синхровходом триггера 6.5.

Счетчик-делитель работает следующим образом.

Для установки счетчика-делителя в исходное состояние на входы 14 и 15 подаются сигналы логической единицы. При этом все триггеры 6.1-6.5 ус танавливаются в нулевое состояние.

Счетчик-делитель работает в трех режимах: деление частоты на 2 и 6; деление частоты на 2, 6 и 12 одновре- менио и деление частоты на 6 и 3.

Рассматрим подробнее каждый из трех режимов работы счетчика-делителя.

В первом режиме (деление на 2 и 6) при исправном состоянии триггеров 6.1- 6.4 счетчик-делитель работает следующим образом.

На входы 16.1-16.4 подаются сигналы логической единицы. В этом случае единичным разрешающим сигналом открываются следующие логические элементы структуры устройства: - вторая группа входов элемента 2-2И-ИЛИ 10.1; первая группа входов элемента 2-2И-ИЛИ 7.1; первый и второй входы элементов И/И-НЕ 8.2, 8.3 и 8.4; через соответствующие элементы И/И-НЕ 8.2-8.4 первая группа входов элементов 2-2И-НЛИ 7.2-7.4; первая группа входов элемента 3-2И-ИЛИ 9.1; вторая группа входов элемента 9.3; вторая группа входов элемента 2-2И-Ш1И 10.2; первая группа входов элемента 2-2И- ИЛИ 10.3 и третья группа входов элемента 3-2И-ИЛИ 9.3.

Одновременно с этим закрываются следующие логические элементы структуры устройства: вторая группа входов элемента 2-2И-ИЛИ 7.1; первая группа входов элемента 2-2И-ИЛИ 10.1; третья

группа входов элемента 3-2И-ИЛИ 9.1; через элементы И/И-НЕ 8.2-8.4 закры- ваются соответствующие им вторые группы входов элементов 2-2И-ИЛИ 7.2- , 7.4; первая группа входов элемента 2-2И-ИЛИ 10.2; вторая группа входов элемента 3-2И-ИЛИ 9.1; первая группа входов элемента 3 2И-ИЛИ 9.3; вторая группа входов элемента 2-2И-ИЛИ 10.3; первая и вторая группы входов элемента 2-2И-Ш1И 10.4.

В этом случае на выходы 17.1-17.4 через первые группы входов соответствующих элементов 2-2И-ИЛИ 7.1-7.4 поступают сигналы с одноименных триггеров 6.1-6.4. Триггер 6.5 находится в горячем реэерве. Деление частоты на 2, поступающей на вход С1, осуществляется триггером 6. 1, деление частоты на 3 - триггерами 6.2 и 6.3, так как на Л -вход триггера 6.2 через первую группу входов элемента 3-2И-Ш1И 9.1 поступает сигнал с инверсного выхода триггера 6.3; деление частоты на 6 - триггером 6.4, так как на его синхровход через первую группу входов элемента 2-2И-ИЛИ ГО.З постулает сигнал с выхода триггера 6.3.

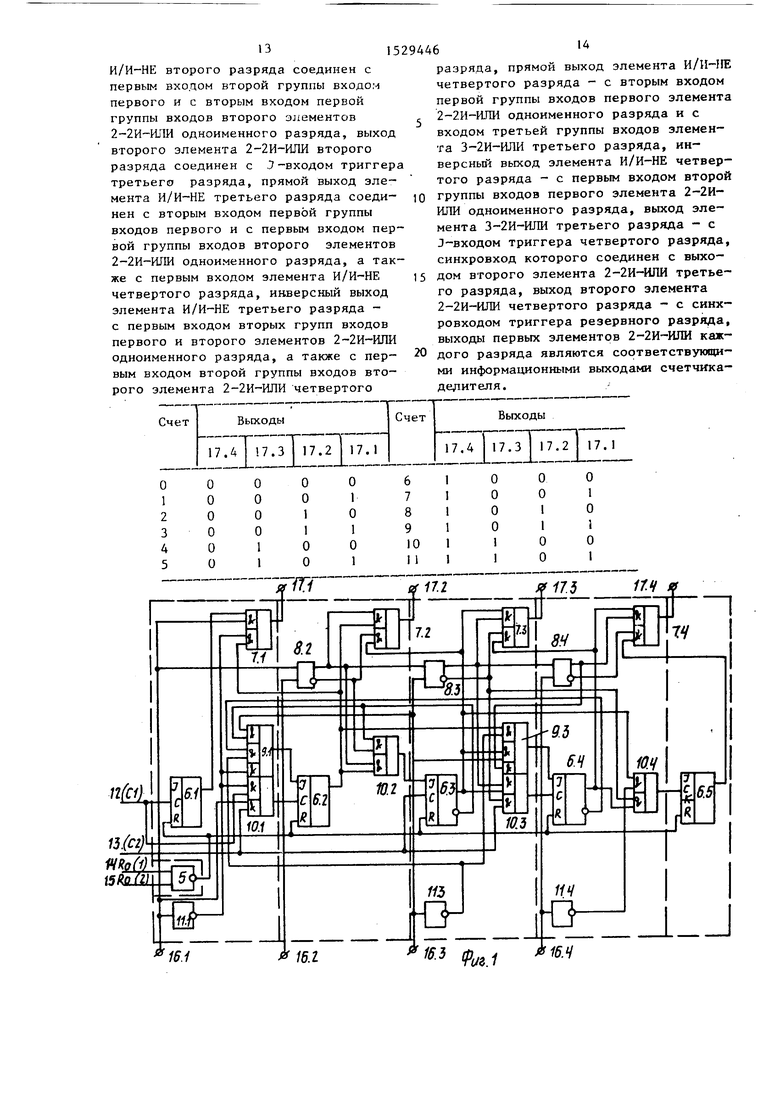

При необходимости деления частоты на 12 выход 17.1 соединяют с входом С2 (13), в этом случае работа счетчика подчиняется алгоритму функционирования, приведенному в сокращенной таблице истинности.

15294468

им элементов 2-2И-ИЛИ 7.2 и 7.3 соответственно. Синхронизирующий сигнал триггера 6.4 поступает на его синхровход с выхода триггера 6.3 через первую группу входов элемента 2-2И-ИЛИ 10.3.

Временная диаграмма работы счетчика в этом режиме показана на фиг.2.

При делении частоты следования на 12 выход 17.1 соединяют с входом С2 (13), а не подают изначальную частоту следования параллельно, как это было в первом случае, на оба входа С1 (12) и С2 (13) синхронизации.

Временная диаграмма работы счетчика в этом режиме показана на фиг.З.

Рассмотрим примеры работы предлагаемого счетчика-делителя при отказе одного из основных триггеров 6.1-6.4.

При отказе триггера 6.1 на соответствующий ему управляющий вход 16.1 подается сигнал логического ну15

20

25

30

35

ля, а на входы 16.2-16.4 - сигналы логической единицы. При этом сигнал логической единицы на выходе элемента НЕ 11.1 открывает первую группу входов элемента 2-2И-Ш1И 10.1 для прохождения на синхровход триггера 6.2 сигнала с входа С1 (12), открывает третью группу входов элемента 3-2И-ИЛИ 9.1,что равнорильно постоянно незадействованному J -входу триггера 6.2, а также вторую группу входов элемента 2-2И-ИЛИ 7.1, т.е. коммутирует выход триггера 6.2 на выход 17.1 счетчикй-делителя.

В режиме деления частоты следования на 2, 3 и 6 подсчет импульсов

производится по следующим логическим цепям: с входа С1 (12) - на синхровход триггера 6.1 (деление на 2); с выхода триггера 6.1 через первую группу входов элемента 2-2И-ИЛИ 7.1- на выход 17.1; с входа С2 (13) через вторую группу входов элемента 2-2И- ИЛИ 10.1 - на синхровход триггера 6.2 и с входа С2 (13) - непосредственно на синхровход триггера 6.3. Логику деления на 3 реализуют конструктивные связи J-входов триггеров 6.2 и 6.3 с инверсным выходом триггера 6.3 и прямым выходом триггера 6.2 соответственно через соответствующие группы входов элементов 3-2И-ИЛИ 9.1 и 2- 2И-ИЛИ 10.2. Сигналы с выходов триггеров 6.2 и 6.3 поступают на одноименные им выходы 17.2 и 17.3 через первые группы входов соответствующих

5

0

5

0

5

JQ сгля, а на входы 16.2-16.4 - сигналы логической единицы. При этом сигнал логической единицы на выходе элемента НЕ 11.1 открывает первую группу входов элемента 2-2И-Ш1И 10.1 для прохождения на синхровход триггера 6.2 сигнала с входа С1 (12), открывает третью группу входов элемента 3-2И-ИЛИ 9.1,что равнорильно постоянно незадействованному J -входу триггера 6.2, а также вторую группу входов элемента 2-2И-ИЛИ 7.1, т.е. коммутирует выход триггера 6.2 на выход 17.1 счетчикй-делителя.

Кроме этого, сигнал логической единицы формируется на инверсном выходе элемента И/И-НЕ 8.2, что приводит к последовательному открытию вторых групп входов соответствукядих элементов 2-2И-ИЛИ 7.2-7.4, то есть коммутации выходов триггеров 6.3 на выход 17.2, триггеров 6.4 - на выход 17.3 и триггера 6.5 - на выход 17,4. Одновременно с этим открываются первая группа входов элемента 2-2И-ИЛИ 10.2 - для прохождения на J-вход триггера 6.2 сигнала с инверсного выхода триггера 6.4; вторая группа входов элемента 2-2И-ИЛИ 10.3 - для прохождения на синхровход триггера 6.4 сигнала с входа С2 (13); вторая группа входов элемента 2-2И-ШШ 10.4 - для прохождения на синхровход триггера 6.5 сигнала с выхода триггера 6.4.

10

25

Нулевой потенциал с входа 16,1 закрывает следующие логические элементы структуры предлагаемого счетчика- делителя: вторую группу входов эле- мента 2-2И-ИЛИ 10.1 - для запрещения поступления на синхровход триггера 6.2 сигналов с входа С2 (13); пер- вую группу входов элемента 2-2И-ИЛИ

7.1- для запрещения прокождения на выход 17.1 сигналов с неисправного триггера 6.1 и закрывает элемент И/И- НЕ 8.2, что приводит к смене состояний логических сигналов на его прямом

и инверсном выходах, а следовательно, 15 на выходах элементов И/И-НЕ 8.3 и 8.4. Нулевые логические сигналы с прямых выходов элементов И/И-НЕ 8.2-8.4 закрывают первые группы входов соответствующих им элемептов 2-2И-ИЛИ 7.2- , 20 7.4, запрещая тем самым поступление на выходы 17.2-17.4 сигналов с выходов одноименных им триггеров 6.2-6.4. Кроме того, нулевой потенциал с прямого выхода элемента И/И-НЕ 8.2 эакры- вает группу входов элемента 2-2И-ИЛИ 10.2, запрещая тем самым прохождение сигнала с выхода триггера 6.2 на Э-вход триггера 6.3. Аналогично, сигнал с прямого выхода элемента И/И-НЕ 8.3 закрывает первую группу входов элемента 2-2И-ИЛИ 10.3, запрещая тем самым прохождение сигнала с прямого выхода триггера 6.3 на синхровход триггера 6.4. Нулевой потенциал с прямого выхода элемента И/И-НЕ 8.4 закрывает третью группу входов элемента 3-2И-ИЛИ 9.3, что равносильно незадействоваиному J-BXO- ду триггера 6.4.40

Таким образом, при подаче на входы 16.1-16.4 сигналов настроечной функции 0111 предлагаемый счетчик автоматически производит реконфигурацию своей логическлй структуры так, 45 что триггер 6.1 отключается и замещается триггером 6.2, вместо которого подключается триггер 6.3, триггер 6.3 замещается триггером 6.4, а триггер 6.4 - триггером 6.5. Выходы счет-50 чика остаются неизменеными.

В случае неисправности триггера .

6.2на управляющие входы 16.1-16.4 подаются сигналы настроечной функции 1011. При этом триггер 6.2 отключается,вместо него подключается триггер 6.3; триггер 6.3 замещается триггером 6.4, а триггер 6.4 - триггером 6.5. Триггер 6.1 остается подключенным

30

35

55

10

5

15 20 0

5 0

30

5

5

к выходу 17.1. Таким образом, при по даче на управляющие входы 16.1-16.4 сигналов настроечной функции 1011 производится вытеснение триггера 6.2 из логической структуры предлагаемого счетчика-делителя.

Аналогичное вытеснение происходит при неисправности триггеров 6.3 и 6.4, то есть при подаче иа управляющие входы 16.1-16.4 сигналов настроечной функции 1101 и 1110.

Рассмотрим порядок подсчета импульсов при неисправном триггере 6.3.

В этом случае на управляюпц1е входы 16.1-16.4 необходимо подать сигналы настроечной функции 1101. При этом открыты следующие логические элементы: первые группы входов элементов 2-2И- ИЛИ 7.1 и 7.2, вторые группы входрв элементов 2-2И-ИЛИ 7.3 и 7.4, вторые группы входов элементов 2-2И-ИЛИ 10.1 и 10.2, вторая группа входов- элемента 3-2И-ЙЛИ 9.1, первая группа входов элемента 3-2И-ИЛИ 9.3, вторые группы входов элементов 2-2И-ИЛИ 10.3 и 10.4.

Следовательно, при подсчете импульсов в предлагаемом счетчике-делителе функционируют следующие логические цепи: с входа С1 (12) - на синхровход триггера 6.1; с входа С2 (13) через вторую группу входов элемента 2-2И-ИЛИ 10.1 - на синхровход триггера 6.2 и через вторую группу входов элемента 2-2И-Ш1И 10.3 - на синхровход триггера 6.4, который заместил в данном случае триггер 6.3. На выход 17.1 поступают сигналы с выхода триггера 6.1, на выход .17.2 - с выхода триггера 6.2, на выход 17.3 - с выхода тригг-ера 6.4 и на выход 17.4 - с выхода триггера 6.5. Таки образом, триггер 6.3 вытеснен из логической структуры предлагаемого счетчика-делителя.

Формула изобретения

Счетчик-делитель, содержащий четыре триггера - по одному в каждом разряде и элемент И-НЕ, первый синхро- вход счетчика-делителя соединен с С-входом триггера первого разряда, первый и второй входы установки в О счетчика-делителя соединены соответственно с первым и вторым входами элемента И-НЕ, выход которого соединен с R-входами триггеров каждого

It

разряда, отличающийся тем, что, с целью повьшения ремонтопригодности, в него введен резервный триггер, который образует резервный разряд, а каждый разряд, кроме второго и резервного, дополнительно содержит элемент НЕ, первый и второй элементы 2-2И-ИЛИ, разряды, кроме первого и резервного, дополнительно со- держат элемент И/И-НЕ, а первый и третий разряды - элемент 3-2И-ИЛИ, причем первый синхровход счетчика-делителя дополнительно соединен с вторым входом первой группы входов вто- рого элемента 2-2И-ИЛИ первого разряда, выход элемента И-НЕ счетчика-дели теля соединен с R-входом триггера резервного разряда, вход разрешения работы первого разряда соединен с вхо- дом элемента НЕ, с вторым входом первой группы входов первого элемента 2-2И-ИЛИ, с первым входом второй группы входов второго элемента 2-2И- ИЛИ одноименного разряда и с первым входом элемента Й/И-НЕ второго разряда, второй вход которого соединен с входом разрешения работы одноименного разряда, вход разрешения работы третьего разряда соединен с входом зле- мента НЕ, с вторым входом элемента И/И-НЕ, с вторым входом второй группы входов элемента- 3-2И-ИЛИ одноименного разряда и с первь м входом первой

15

6

разряда,

12

прямом выход триггера первого разряда соединен с первым входо первой группы входов первого элемента 2-2ИИЛИ одноименного разряда, прямой выход триггера второго разряда - с вторыми входами первой группы входов первого и второй группы входо второго элементов 2-2И-И1ГИ одноименного разряда, а также с вторым входом второй группы входов первого элемента 2-2ИИЛИ первого разряда и с первым входом первой группы входов элемента 32И-ИЛИ третьего разряда, прямой выход триггера третьего разряда - с вторым входом первой группы входов второго элемента 2-2И-ИЛИ, с первым входом второй группы входов элемента 3 2И-Ш1И и с первым входом первой группы входов первого элемента 2-2ИИЛИ одноименного разряда, а также с вторым входом второй групп входов первого элемента 2-2И-ИЛИ второго разряда и с первым входом певой группы входов второго элемента 2-2И-ИЛИ четвертого разряда, прямой выход триггера четвертого разряда - с вторым входом второй группы входов второго и с первым входом первой группы входов первого элементов 2-2И-ИЛИ одноименного разряда, а так же с вторым входом второй группы входов первого элемента 2-2И-ИЛИ третьего разряда, инверсный выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик-делитель | 1989 |

|

SU1598169A1 |

| Двоично-десятичный счетчик | 1988 |

|

SU1517133A1 |

| Двоично-десятичный счетчик | 1989 |

|

SU1676098A1 |

| Двоичный счетчик | 1989 |

|

SU1598170A1 |

| Двоичный счетчик | 1988 |

|

SU1529447A1 |

| Двоичный счетчик | 1988 |

|

SU1555857A1 |

| Двоичный счетчик | 1989 |

|

SU1644374A1 |

| Счетчик импульсов | 1985 |

|

SU1298906A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

| Счетчик импульсов | 1986 |

|

SU1422404A1 |

Изобретение может быть использовано в автоматике и вычислительной технике в качестве базового элемента в устройствах с повышенными требованиями к времени восстановления работоспособности. Цель изобретения - повышение эксплуатационной отказоустойчивости-достигается путем введения в счетчик-делитель в его логическую структуру резервного триггера, элементов 2-2И-ИЛИ, элементов 3-2И-ИЛИ, элементов НЕ, элементов И/И-НЕ с соответствующими конструктивными связями. Это обеспечивает переход на резервную работоспособную структуру при эксплуатационном отказе одного из основных триггеров. В случае отказа одного на основных элементов его структуры на соответствующий управляющий вход подается сигнал логического нуля. Вследствие этого производится реконфигурация логической структуры устройства, при которой неисправный разряд отключается и замещается "горячим резервом". 3 ил.

группы входов элемента 3-2И-ИЛИ перво-.j триггера третьего разряда соединен

го разряда, вход разрешения работы четвертого разряда - с вторьм входом злемента И/И-НЕ и с входом элемента НЕ одноименного разряда, выход которого соединен с вторым входом первой группы входов второго элемента четвертого разряда, выход элемента НЕ первого разряда соединен с первым входом первой группы входов второго элемента 2-2И-ИЛИ, с входом третьей группы входов элемента 3-2И-ИЛИ и с первым входом второй группы входов первого элемента 2 2И-ИЛИ одноименного разряда, выход элемента НЕ третьего разряда соединен с вторым входом первой группы входов элемента 3-2И-ИЛИ одноименного разряда и с вторым входом второй группы входов элемента 3-2И-ШШ первого разряда, второй синхровход счетчика-делителя соединен с вторыми входами вторых групп входов элементов 2-2И-ИЛИ первого и третьего разрядов и с синхровходЬм триггера третьего

40

45

с вторым входом первой группы входо элемента 3-2И-ИЛИ первого разряда, инверсный выход триггера четвертого разряда - с первым входом первой группы входов второго элемента 2-2И ИЛИ второго разряда и с первым входом второй группы входов элемента 3-2И-ИЛИ первого разряда, прямой вы ход триггера резервного разрада сое динен с вторым входом втррой группы входов первого элемента 2-2И-ИЛИ четвертого разряда, выход элемента 3-2И-ИЛИ первого разряда соединен с 3 -входом триггера второго разряда 5Q синхровход которого соединен с выхо дом второго элемента 2-2И-ИЛИ перво разряда, прямой выход элемента И/И-НЕ второго разряда - с первым входом первой группы входов первого и с первым входом второй группы вхо дов второго элементов 2-2И-ШШ одно именного разряда, а также с первым входом элемента И/И-НЕ третьего раз ряда, инверсный выход элемента

55

триггера третьего разряда соединен

с вторым входом первой группы входов элемента 3-2И-ИЛИ первого разряда, инверсный выход триггера четвертого разряда - с первым входом первой группы входов второго элемента 2-2И- ИЛИ второго разряда и с первым входом второй группы входов элемента 3-2И-ИЛИ первого разряда, прямой вы-, ход триггера резервного разрада соединен с вторым входом втррой группы входов первого элемента 2-2И-ИЛИ четвертого разряда, выход элемента 3-2И-ИЛИ первого разряда соединен с 3 -входом триггера второго разряда, синхровход которого соединен с выхог дом второго элемента 2-2И-ИЛИ первого разряда, прямой выход элемента И/И-НЕ второго разряда - с первым входом первой группы входов первого и с первым входом второй группы входов второго элементов 2-2И-ШШ одноименного разряда, а также с первым входом элемента И/И-НЕ третьего разряда, инверсный выход элемента

И/И-НЕ второго разряда соединен с первым входом второй группы входом первого и с вторым входом первой группы входов второго элементов 2-2И-ИЛИ одноименного разряда, выход второго элемента 2-2И-ИЛИ второго разряда соединен с 3-входом триггер третьего разряда, прямой выход элемента И/И-НЕ третьего разряда соединен с вторым входом первой группы входов первого и с первым входом первой группы входов второго элементов 2-2И-ИЛИ одноименного разряда, а также с первым входом элемента И/И-НЕ четвертого разряда, инверсный выход элемента И/И-НЕ третьего разряда - с первым входом вторых групп входов первого и второго элементов 2-2И-ИЛИ одноименного разряда, а также с первым входом второй группы входов второго элемента 2-2И-ИЛИ четвертого

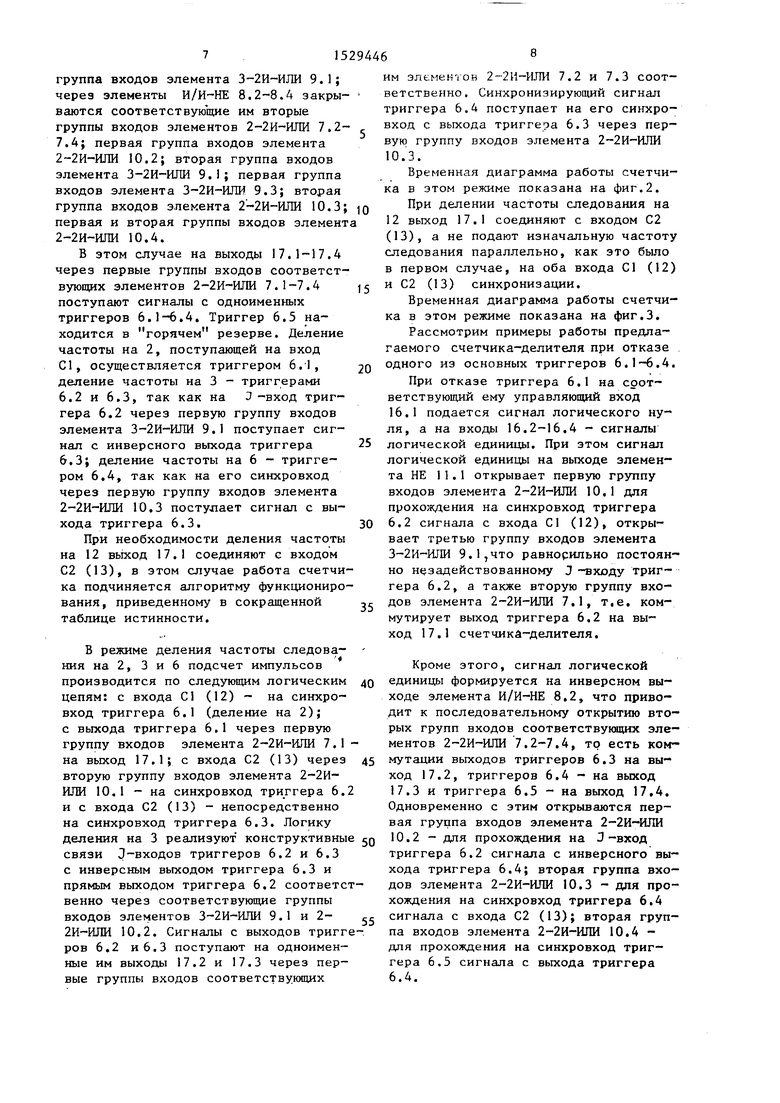

Счет

Выходы

О О О О О О

О О О О 1 1

О

о 1 1

о о

ТГГ

разряда, прямой выход элемента И/И-1ГЕ четвертого разряда - с вторым входом первой группы входов первого элемента 2-2И-ИЛИ одноименного разряда и с входом третьей группы входов элемента 3-2И-ИЛИ третьего разряда, ин- версньй выход элемента И/И-НЕ четвертого разряда - с первым входом второй

группы входов первого элемента 2-2И- ИЛИ одноименного разряда, выход элемента 3-2И-ИЛИ третьего разряда - с J-входом триггера четвертого разряда, синхровход которого соединен с выхо-

дом второго элемента 2-2И-ИЛИ третьего разряда, выход второго элемента 2-2И-ИЛИ четвертого разряда - с синх- ровходом триггера резервного разряда, выходы первых элементов 2-2И-Ш1И каждого разряда являются соответствующими информационными выходами счетчика- дедителя.

Счет

Выходы

6

7 8 9 10 I 1

О О О О 1 I

О О 1 1 О

о

о 1

о 1

о 1

1Г.Ч

| Делитель частоты следования импульсов | 1985 |

|

SU1243128A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Справочник | |||

| Применение интегральных микросхем в электронной вычислительной технике | |||

| Под ред | |||

| Б.Н.Фай- зулаева, Б.В.Тарабрина | |||

| М.: Радио и связь, 1987, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-08—Подача