-,. Раз/хи

т

ю

С

пв 1

С

к

Изобретение относится к вычислительной технике и может быть использовано для контроля логических бло- ков преимущественно в случаях, когда требуется повышенная достоверность контролирующего оборудования.

Целью изобретения является расширение функциональных возможностей за счет обеспечения самоконтроля в процессе функ1щонирования.

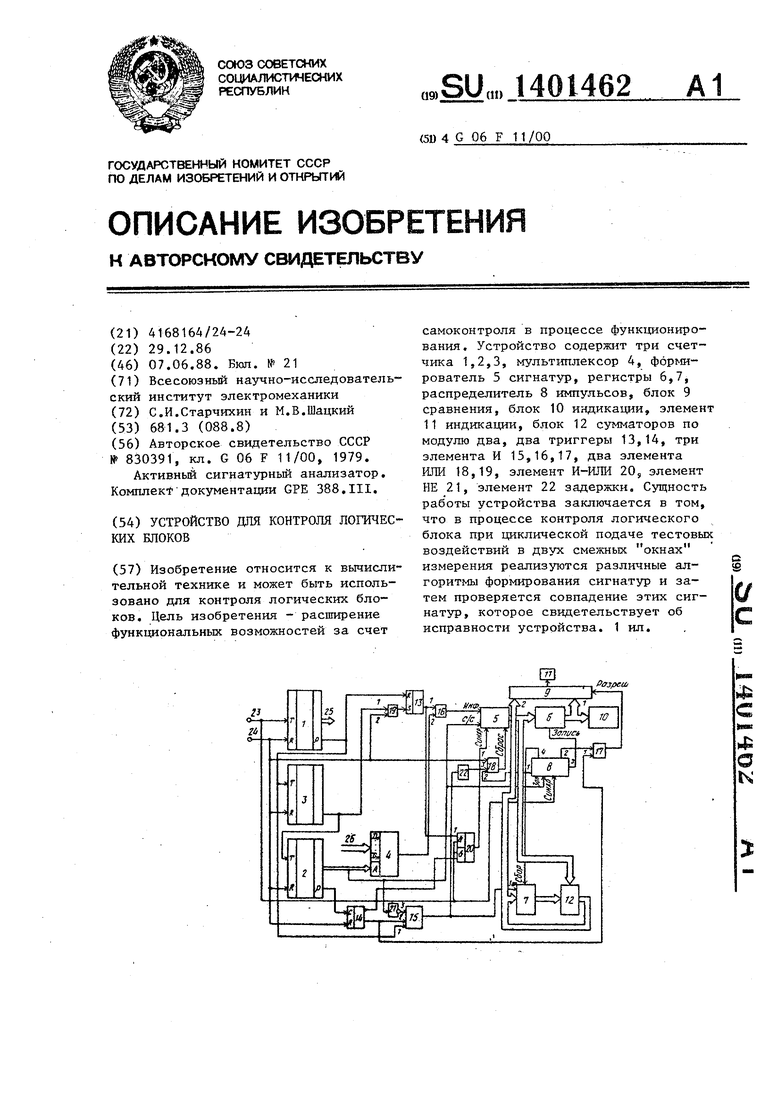

На чертеже приведена функциональная схема устройства для контроля логических блоков.

Устройство содержит три счетчика 1-3, мультиплексор 4, формирователь 5 сигнатур, первый 6 и второй 7 регистры, распределитель 8 -импульсов, блок 9 сравнения, блок 10 индикации, элемент 11 индикации, блок 12 сумма- торов по модулю два, два триггера 13 и 14, три элемента И 15-17, два элемента ИЛ 18 и 19, элемент И-ШШ

20, элемент НЕ 21, элемент 22 задерж

ки.

мультиплексора 4 через элемент И 16 сигналы с одного из выходов контролируемого логического блока.

Разрядность счетчика 1 выбирается исходя из условия

п,:} т, (п 16 для 16-разрядного анализатора), (1)

где п, - разрядность счетчика 1;

га - количество входов контролируемого блока (т 16), Разрядность счетчика 3 выбирается исходя из условия

П + П а N,

(2)

где Пд - разрядность счетчика 3,

N - разрядность формирователя 5

сигнатур,

Разрядность счетчика 2 выбирается следующим образом:

25 nj7/logjM,

(3)

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Сигнатурный анализатор | 1985 |

|

SU1312576A2 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1365087A2 |

| Устройство для контроля мультиплексора | 1990 |

|

SU1741136A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков. Цель изобретения - расширение функциональных возможностей за счет самоконтроля в процессе функционирования. Устройство содержит три счетчика 1,2,3, мультиплексор 4, формирователь 5 сигнатур, регистры 6,7, распределитель 8 импульсов, блок 9 сравнения, блок 10 индикации, элемент 11 индикации, блок 12 сумматоров по модулю два, два триггеры 13,14, три элемента И 15,16,17, два элемента ИЛИ 18,19, элемент И-ИЛИ 20, элемент НЕ 21, элемент 22 задержки. Сущность раб оты устройства заключается в том, что в процессе контроля логического блока при циклической подаче тестовых воздействий в двух смежных окнах измерения реализуются различные алгоритмы формирования сигнатур и затем проверяется совпадение этих сигнатур, которое свидетельствует об исправности устройства. 1 ил. i С

На чертеже также обозначены синхро вход 23 устройства, вход 24 сброса, группа 25 информационных выходов для подключения входов контролируемого блока, группа 26 информационных вхо дов для подключения выходов контролируемого блока.

Устройство работает следующим образом;

По сигналу исходного состояния, подаваемого на вход 24 Сбр ос, устанавливаются в нулевое состояние счетчики 1-3, триггер 14 и формирователь 5 сигнатур. Триггер 13 устанавливается этим сигналом в единичное состоя- ние.

С прихбдом первого после сигнала сброса синхросигнала на вход 23 устройства начинается подсчет синхросигналов счетчиками 1-3. При этом раз- рядными выходами счетчиков 1 осуществляется стимуляция контролируемого блока (для простоты рассматривается случай, когда все входы контролируемого блока являются совместимыми и стимуляция осуществляется тривиальньи двоичным кодом.

Синхросигналы с входа 23 устройства через элемент И-ИЛИ 20, открытый разрешающим потенциалом на его четвертом входе с инверсного выхода триггера 14, поступает на синхровход формирователя 5 сигнатур. На информа- 1ДИОННЫЙ вход его поступают с выхода

0

5 0

5

0

5

где HI - разрядность счетчика 2,

М - количество выходов контролируемого блока,

После перебора счетчиком 1 (2 -1) состояний на его выходе появляется сигнал переполнения, который поступает на счетньй вход счетчика 3, Этим же сигналом,устанавливается в нулевое состояние триггер 13, и нулевой потенциал с его выхода поступает на первый вход элемента И 16, запрещая прохождение информации с выхода мультиплексора 4 на информационный формирователя 5 сигнатур, В то же время синхросигналы на синхровход формирователя 5 сигнатур продолжают поступать. Это эквивалентно поступлению на его информационный вход последовательности нулей.

После прихода ()-го синхроимпульса сигьал с выхода переполнения счетчика 3 поступает на счетный вход счетчика 2, изменяя состояние его выходов и выбирая тем самым с помощью мультиплексора 4 следующий информационный выход контролируемого блока. Одновременно этот же сигнал переполнения через элемент ИЛИ 19 устанавливает триггер 13 в единичное состояние, разрешая прохождение информации с выхода мультиплексора 4 через элемент И 1б на информационный вход формирователя 5 сигнатур.

Далее описанные циклы повторяются до тех пор, пока сигналом с выхода старшего разряда счетчика 2 не будет прекращено формирование сигнатуры в

iia,,i..,ai,400,,.0 ,, . .0 ... ам1 а щ.. .аы|;00.. .0

1 где

Можно показать, что справедливо следующее равенство:

У1

S(A) I.S(Aj),

где S(A) - сигнатура последовательности А,

S(A.) - частная сигнатура последовательности

А .«,а{|,

- знак сложения по модулю два.

На основании равенства (5) и осуществляется самоконтроль устройства.

После окончания цикла формирования первой сигнатуры сигналом со старшего разрядного выхода счетчика 2 разрешается работа распределителя импульсов, который по четырем следующим друг от друга синхроимпульсам поочередно вьщает на четырех своих выход ах управляющие сигналы, которые обеспечива:от последовательную реализацию следующих функций: сравнение в блоке 9 сравнения сигнатуры, хранящейся в регистре 6, и суммы сигнатур с выхода блока 12 (в случае наличия на первом входе элемента И 17 разрешающего потенциала с прямого выхода триггера 14)} запись в регистр 6 содержимого формирователя 5 сигнатур; обнуление регистра 7; обнуление формирователя 5.сигнатур.

В первом окне измерения (и во всех последующих окнах с нечетным номером) нулевой потенциал с прямого выхода триггера 14 запрещает прохождение сигнала разрешения сравнения с выхода распределителя 8 импульсов на вход разрешения блока 9 сравнения

Далее, до переполнения счетчика 2, состояние формирователя 5 сигнатур и распределителя 8 импульсов остается неизменным.

Сигнал с выхода переполнения счетчика 2 поступает на счетный вход триггера 14 и устанавливает его в

формирователе 5 сигнатур. При этом за (2 -1) прошедших тактов на информационный вход форшфователя 5 сигнатур поступает последовательность

. .0 ... ам1 а щ.. .аы|;00.. .0

2-1

(4)

t

единичное состояние. Начинается второе окно измерения, При этом на четвертый вход элемента И-ИЛИ 20 по15 ступй ет нулевой потенциал с инверсного выхода триггера 14, и прохождением синхросигналов от синхровхода 23 устройства до синхровхода формирователя 5 сигнатур начинает управлять

20 по первому входу элемента И-ИЛИ 20 триггер 13,

После вьщачи сигнала с выхода переполнения счетчика 2 все счетчики 1-3 устанавливаются в нулевое состоя25 ние, а триггер 13 - в единичное состояние (так как сигнал переполнения с выхода счетчика 3 поступает позже, чем сигнал переполнения с выхода счетчика 1). При этом при поступле-

30 НИИ на вход 23 устройства синхросигналов он через элемент И-ИЛИ 20 поступают на синхровход формирователя 5, а на его информационньп вход поступает входная информация с выхода

ос мультиплексора 4 через элемент И 16, После того, как на информационный вход Формирователя 5 сигнатур будет подана частная информационная последовательность А,а ,, а ,1 ,. .а, , сиг40 нал с выхода переполнения счетчика 1 устанавливает триггер 13 в нулевое состояние, прекращая тем самым подачу на формирователь 5 сигнатур и информационной, и синхронизирующей по4g следовательностей.

Этот же сигнал переполнения через элемент И 15 поступает на вход записи регистра 7, в которьй при этом записывается сумма по модулю два

gQ предьиущего состояния регистра 7 (в данном случае, нуля) и частной сигна-. туры, сформированной в формирователе 5 сигнатур. Этот же сигнал, пройдя через элемент 22 задержки и элемент

ИЛИ 18, обнуляет формирователь 5 сиг- 55

натур.

Далее счетчики 1 и 3 продолжают подсчитывать синхроимпульсы, поступающие на вход 23 устройства. После

прохождения ()-го синхроимпульса вырябатывается сигнал переполнения счетчика 3, Этот сигнал переключает в следующее состояние счетчик 2,т.е, с помощью fyльтиплeкcopa 4 подключа™ ет очередной выход контролируемого блока к цепи контроля. Одновременно сигнал переполнения с быхода счетчика 3 устанавливает в единичное состояние триггер t3, разрешая прохождение на формирователь 5 сигнатур информа ционной и синхронизирующей последовательностей. Цикл измерения повторяется, при этом в формирователе 5 сиг- натур формируется сигнатура частной информационной последовательности rT...k

Далее в регистр 7 записывается , формирователь 5 сигнатур в очередной раз обнуляется, т.е. подготавливается к формирбванию сигнатуры очередной частной информационной последовательности .

После того, как таким образом бу- дут.сформированы сигнатуры всех частных информационных последовательностей, в регистре 7 будет храниться ве- м

величина Ж S(A-). При этом, как ука i .

зыва.пось,в регистре 6 хранится значение сигнатуры SCA), сформированное в первом окне измерения.Сигнал со старшего разрядного вы

хода счетчика 2 через элемент НЕ 21 запрещает дальнейшее прохождение импульсов записи в регистр 7 и сброса в фор1 гирователь 5 с выхода элемента И 15. Этот же сигнал разрешает рабо- ту распределителя 8 импульсов, вьща- ющего сиглалы сравнения содержимого регистров 6 и 7j записи в регистр 6 содержимого формирователя 5 сигнатур обнуления регистра 7 и формирователя 5 сигнатур. Б случае несовпадения содержимого регистров 6 и 7 элемент 11 индикации сигнализирует о наличии неисправности в схеме устройства, так как одинаковые сиг натуры, сфор- мированные различными способами, оказались не равными между собой. Далее весь описанньй выше цикл измерений повторяется. Полученная сигнатура индицируется блоком 10 индикации (цепь управления индикГацией условно не показана) и сравнивается оператором с эталонной сигнатурой контролируемого блока.

с

0

5

0

5

Q

По окончании второго окна измерения в регистр b записывается сигнатура последней частной информационной последовательности, т.е. ненужная информация. Однако это несзтцественно ввиду того, что в следунлцем окне измерения сравнение содержимого регистров 6 и 7 не производится из-за наличия нулевого запрещающего потенциала на прямом выходе триггера 14. Во всех же окнах измерения с четными номерами производится сравнение в полном соответствии с равенством (5).

Таким образом, предлагаемое устройство позволяет в смежных окнах измерения формировать одну,и ту же сигнатуру входной информационной последовательности двумя различными способами с последукяцим их сравнением. Несовпадение полученных таким образом сигнатур свидетельствует о наличии неисправности в схеме устройства. Процедура самоконтроля осущв - ствляется непосредственно в процессе работы.

Формула изобретения

Устройство для контроля логических блоков, содержащее первый и второй счетчики, мультиплексор, формиро- ватель сигнатур, первьш регистр, блок сравнения, распределитель импульсов, первьй элемент ЕЛИ, блок индикации и элемент индикации, причем синхро- вход устройства подключен к синхро- входу распределителя импульсов и к счетному входу первого счетчика,, группа разрядных выходов которого является группой информационных выходов устройства для подключения входов контролируемого блока, вход сброса устройства подключен к первому входу первого элемента ИЛИ и к входам сброса первого и второго счетчиков, группа разрядных выходов второго счетчика соединена с группой адресньвс входов мультиплексора, старший разряд груп-. пы адресных входов мультиплексора соединен с входом управления окном измерения формирователя сигнатзф и с входом запуска рвспредепителя импульсов, группа информационных входов мультиплексора является группой информационных входов устройства для подключения выходов контролируемого блока, первый выход распределителя импульсов соединен с вторым входом

первого элемента ИЛИ, выход которого соединен с входом сброса формирователя сигнатур, группа выходов которого соединена с группой информационных входов первого регистра, группа выходов которого соединена с группой входов блока индикации и первой группой информационных входов блока сравнения, выход которого соединен с BXOдом элемента индикации, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения самоконтроля в процессе функционирования, оно дополни- тельно содержит третий счетчик,, второй регистр, блок сумматоров по модулю два, два триггера, три элемента И, второй элемент ИЛИ, элемент И-ИЛИ, .элемент НЕ и элемент задержки, при- чем счетный вход третьего счетчика объединен с нулевым входом первого триггера, первым входом первого элемента И и подключен к выходу переполнения первого счетчика, вход сброса третьего счетчика объединен с нулевым входом второго триггера, вторым входом второго элемента ИЛИ и подключен к входу сброса устройства, выход переполнения третьего счетчика соединен с первым входом второго элемента ИЛИ и счетным входом второго счетчика, выход переполнения которого соединен со сч етным входом второго триггера, выход второго элемента ИЛИ соединен с единичным входом первого триггера, выход которого соединен с первыми входами второго элемента И и элемента И-ИЛИ, второй вход и выход второго

Q 0 5

0

5

элемента И подключены к вькоду мультиплексора и информаи:ионно гу входу формирователя сигнатур соответственно, второй и третий входы элемента И-РШИ объединены и подключены к син- хровходу устройства, четвертый вход и выход элемента И-ИЛИ подключены к инверсному выходу второго триггера и синхровходу формирователя сигнатур соответственно, прямой выход второго триггера соединен с вторьп { входом первого элемента И и первым входом третьего элемента И, вход и выход элемента НЕ подключены к старшему разряду группы адресных входов мультиплексора и третьему входу первого элемента И соответственно, выход первого элемента И соединен с входом записи второго регистра и через элемент задержки - с третьим входом пер- влгр элемента ИЛИ, группа информационных входов второго регистра объединена с второй группой информационных- входов блока сравнения и подключена к группе выходов блока сумматоров по модулю два, первая и вторая группы входов которого соединены с группами выходов формирователя сигнатур и второго регистра соответственно, второй, третий и четвертьй выходы распределителя импульсов соединены соответственно с вторым входом третьего элемента И, входом записи первого регистра и входом сброса второго регистра, выход третьего эле- мента И соединен с входом разрешения блока сравнения.

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Активньй сигнатурный анализатор | |||

| Уровень с пузырьком | 1922 |

|

SU388A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-29—Подача